FPGA软件静态质量度量∗

2018-01-04李晨阳

李晨阳

(中国电子科技集团公司第十研究所 成都 610036)

FPGA软件静态质量度量∗

李晨阳

(中国电子科技集团公司第十研究所 成都 610036)

针对FPGA软件质量依靠商业工具评价不足现象,通过对软件代码静态质量度量模型研究,结合FPGA软件自身特性,提出了FPGA软件静态质量度量新方法,以量化数据表示代码质量水平,给出评价算法和评价流程,并对商业工具Alint质量评价系统进行了改造,运用于实际案例分析中。测试结果表明,新的度量方法能够有效地对软件静态质量进行度量,为评价FPGA软件质量水平提供了一条新的验证途径,减少了软件质量评价中的主观性。

FPGA软件;静态质量;度量元;规则集;加权

1 引言

随着FPGA在军事、航空航天等领域越来越广泛而重要的应用,对FPGA软件测试受到越来越多的行业重视和研究。在FPGA软件生命周期模型中,代码检查是测试的第一道门户,这道门户检查质量的好坏不仅对代码本身质量带来影响,而且对后续工作会产生很大影响,后续各个环节出现问题都会反馈回代码本身,产生反复的迭代工作。目前代码检查质量度量通常的做法是采用软件的代码质量评价标准,有失公平且过于粗糙化;其次采用第三方验证厂商提供的验证工具对代码质量度量评价系统在实际使用过程中指导意义不大。随着行业内FPGA软件测试质量的逐渐重视和强烈要求,也希望有一套科学严谨的方法去评价软件质量。因此,为了真实地反映出FPGA软件的质量,迫切需要提出一种能够对FPGA软件进行质量评价的新方法。正是以此为目的而开展研究,基于FPGA软件检查,通过理论分析研究和实际应用相结合,建立FPGA软件质量度量评价模型,提出度量评价流程、度量元分类、度量元加权系数计算、度量计算方法、评价规则和实际运用,最后举例证明方法的有效性。

2 传统FPGA软件质量度量模型

一直以来FPGA软件静态质量度量主要是采用软件的代码质量度量方法去评价测试结果。国内西安电子科技大学邸博士提出了一种以复杂度为导向的FPGA源代码抽象方法进行质量评估[1],德国Dresden实验室从IP核的角度提出了一种FP⁃GA软件评价方法[2],尽管取得一定研究成果,但普遍性指导意义不强。业内主流验证工具Alint提供了一个质量评价系统,但内容划分简单,在实际应用过程中指导意义不大。

GJB 16260标准中定义了软件的外部、内部和使用质量的三种质量模型,根据该规定,可靠性的依从性度量目的是遵循与产品的可靠性适用的法规、标准和约定的程度如何,是对要求的依从性已经满足的项数进行统计,与要求的项数进行比较[3],那么代码质量评价计算方式如下。

式中:A为在测试中规定的可靠性的依从性还未完全实现的项数;B为规定的可靠性的依从性项总数。

式(1)表明,A为所发生的缺陷数,B为所要求的依从数量。当A越大,则X越小,越接近于0,则表明越差;反之,当A越小,则X越大,越接近于1,则表明越好。使用这种方法来评价FPGA软件质量,具有简单直接,但缺少了考虑FPGA软件度量元差异性带来的影响,也未反映出FPGA软件度量元数量等因素所产生的影响。

3 新的FPGA软件质量度量模型

新的模型处理方法将避免传统一刀切的处理方式,通过严格设定度量元及其度量元加权系数计算,建立一套行之有效的计算方法和评价机制。

3.1 FPGA软件质量度量评价流程

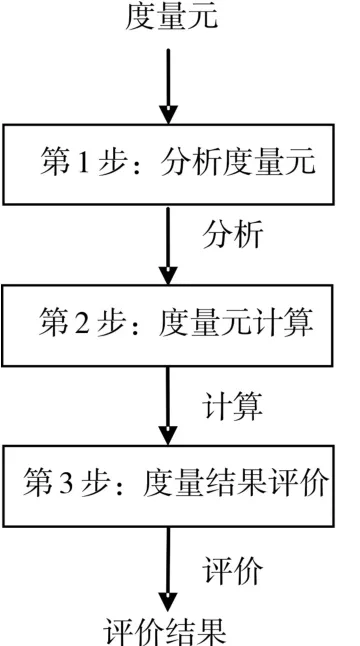

为了能够客观地评价检查结果的质量,评价流程需要分为“三步走”[4]。第 1步:分析评价违反的度量元组成类型,提取相关加权系数,确定评价度量元的数量;第2步:按照公式计算出违反的度量元与规定的度量元比分;第3步:根据公式和评价规则,给出评价结果。整个评价流程如图1所示。

三步走包含了分析、计算和评价三个过程,评价流程中更加注重度量元的分析计算,不同于传统的FPGA软件质量度量评价过程,新的流程将对该工具进行改造,并给出最终评价结果。

图1 FPGA软件静态质量评价流程

3.2 FPGA软件度量元分类

FPGA软件质量的好坏取决于规则集的制定,不同的规则集对检查代码的质量影响不同。因此,度量元是选取规则集及其包含的规则。FPGA软件包含VHDL和Verilog两种语言,对应规则分为VH⁃DL和Verilog两种,但通常设计都是采用两者混合语言使用,因此,度量元将两者规则集混合起来统计。

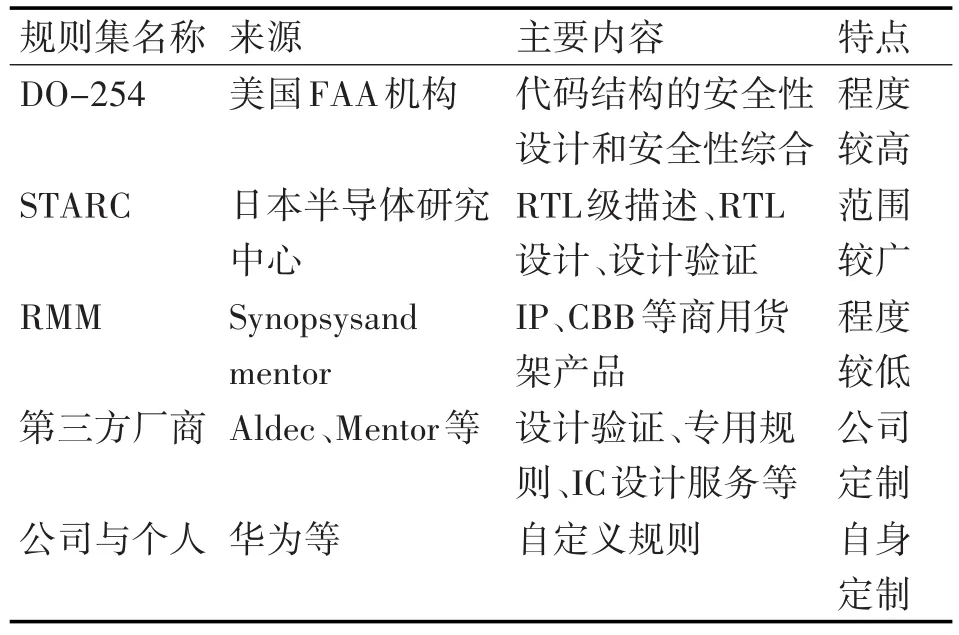

目前,行业内的规则集主要分为三类,首先是外国的DO-254、STARC、RMM等规则集,其次是第三方厂商提供,如 Aldec、Mentor、Synopsys、Xilinx、Altera等国外公司,最后是国内的一些单位以及个人等整理或者定制的编码规则集。具体分类如表1所示。

表1 FPGA软件规则集分类

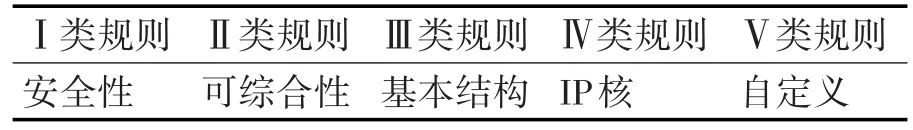

总结分析,FPGA软件的度量元选取主要涉及到安全性设计、可综合性设计、基本结构设计、IP核设计和自定义设计等。具体分类情况如表2所示。

表2 FPGA软件度量元分类

3.3 FPGA软件度量元加权系数计算

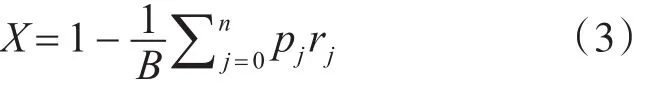

由于FPGA软件选取度量元的每个成员函数的准则值对所属类准则值的影响权重不相同,依据对质量影响的严重程度按照缺陷严重性等级的不同而进行不同的加权比,同时每个度量元缺陷发生的数量多少也会影响评价效果,加权的计算要和自身规则的影响程度符合,根据GJB 2423A的故障统计次数计算[5],那么式(1)中的缺陷总数 A为

式中:pj为某类缺陷的加权系数;rj为某类缺陷发生的次数;j为缺陷类型;n为缺陷类型数。

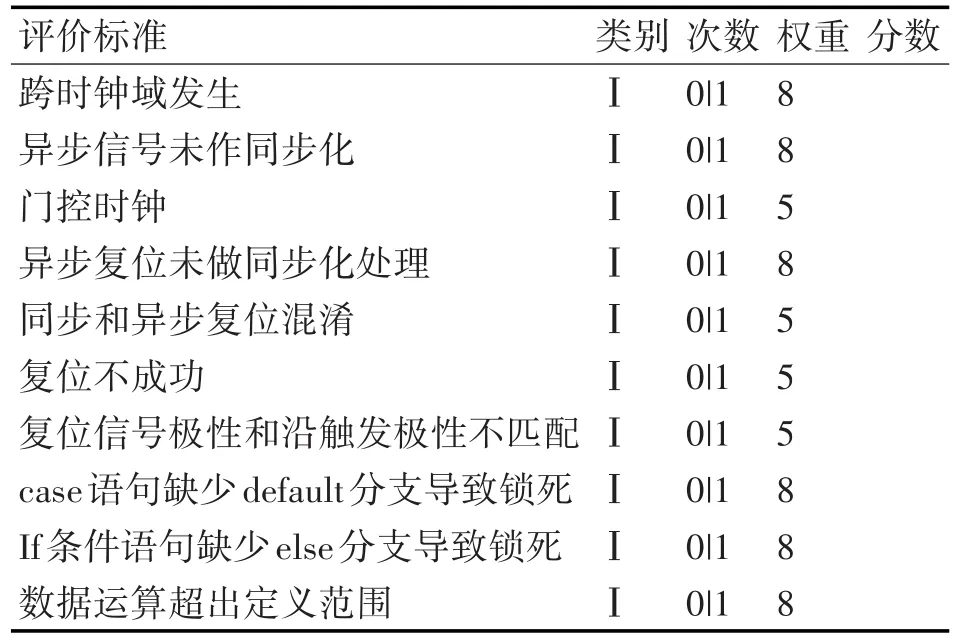

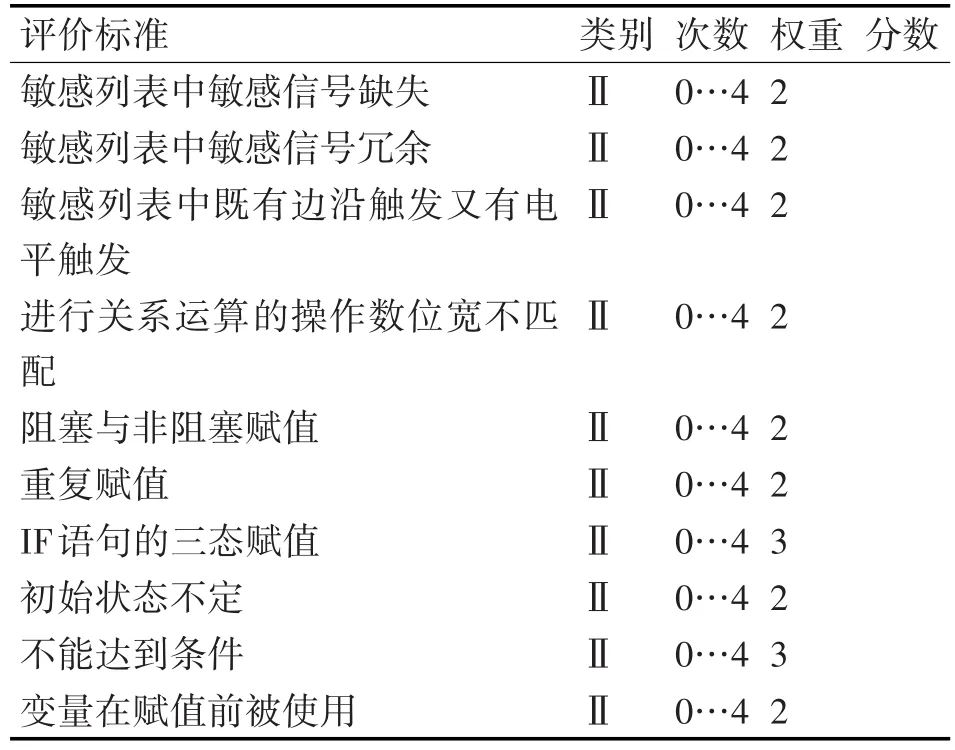

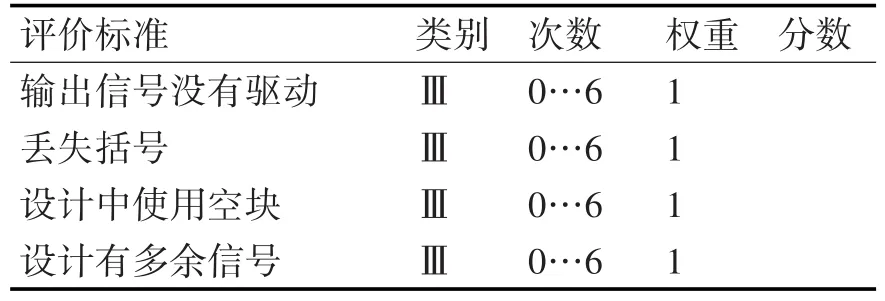

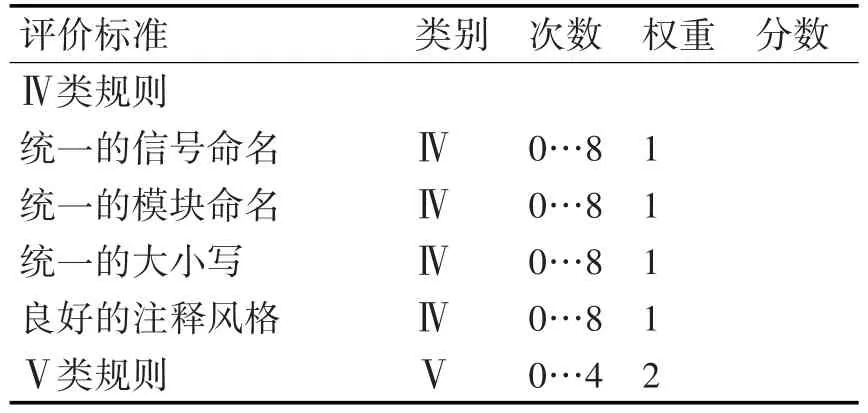

其中,确定加权系数的原则,在GJB 2423A中描述,对缺陷进行分类、定级,分析缺陷的原因、潜在的影响及对人员的危害性,对实现功能的影响程度等。根据影响程度结合文献[2]和其他相关文献[6~7],对FPGA软件度量元进行分类加权,加权情况如表3~6所示。

表3 Ⅰ类规则度量元加权表

表4 Ⅱ类规则度量元加权表

表5 Ⅲ类规则度量元加权表

表6 Ⅳ和Ⅴ类规则度量元加权表

表3~6分别对FPGA软件评价标准的度量元在五个类别的基础上再次细分,评价准则分别包含类别、次数、权重和分数。次数0|1表示分配数选取是0和1,次数0…4表示分配数选取是0~4之间。在本文中,其权重表明度量元在软件评测中所占的比重,对软件代码质量影响大且与其它度量元相差大的则赋予较大的数值。

其中,安全性规则主要涉及对设计起着重要作用且影响严重程度最高的规则集,分配比分最高。亚稳态是FPGA软件中典型的缺陷,是首要查找的缺陷,只要有异步元件存在,亚稳态就无法避免;其次,复位电路是FPGA软件中最核心的组成部分之一,设计中的任何一个逻辑单元都必须要附加复位逻辑电路,以保证电路能够从错误状态中恢复,可靠地工作[8];其他规则都按照影响程度不同做了不同的加权。尽管加权带有一定的主观性,但加权都是在总结实际经验和参考其他文献的基础上客观地反应出每个规则对FPGA软件的安全性、设计性、可综合性和可移植性带来的影响程度。

3.4 FPGA软件度量计算方法

依据表3~6,将式(2)代入式(1),那么最终FP⁃GA软件质量度量方法是:

式(3)表明,当随着缺陷次数rj、权重 pj和缺陷类型数n值各自增大时,则评价值X越小,表明质量越坏;反之,当随着缺陷次数rj、权重 pj和缺陷类型数n值各自减小时,则评价值X越大,表明质量越好[9]。

3.5 FPGA软件度量评价

在GJB 5236中有过描述,用于质量需求度量的测量标度可以根据需求将测量度分为三个级别:达到目标(良好)、最低可接受(合格)和不可接受(不合格),至于在何种程度加以评价标准中没有给出明确规定。那么根据FPGA软件度量具有归一化的处理特性,因此定义FPGA软件质量度量值X评价规则如下:

当 X>0.8,认为良好;

当0.5<X≤0.8,认为合格;

当 X≤0.5,认为不合格。

代码质量度量评价问题实际上是一个多目标决策问题,在处理多目标问题时,往往要考虑各目标的相对重要性[10]。最后,代码质量评价还需求经过实际工程验证,经过多次反复证明才是有用,只有这样,我们才能确保使用的评价方法和实际需求是一致。

4 测试结果与分析

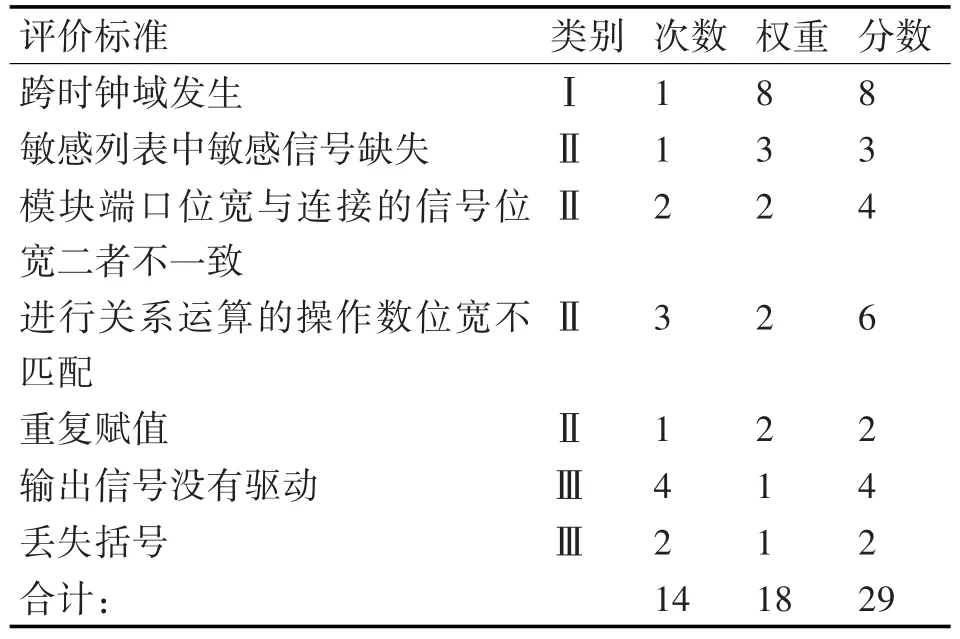

以某工程的信号处理和数据处理两类FPGA软件测试为例,被评的两类软件度量元取数都为66个。测试人员对类1软件进行了编码规则检查,共发现缺陷7个(其中致命缺陷0个,严重缺陷1个,一般缺陷4个,建议改进2个)。测试人员对类2软件进行了编码规则检查,共发现缺陷9个(其中致命缺陷0个,严重缺陷0个,一般缺陷5个,建议改进4个)。具体类1和类2违反的规则情况如表7和表8所示。

表7 类1软件FPGA软件度量元分类加权评价

表8 类2软件FPGA软件度量元分类加权评价

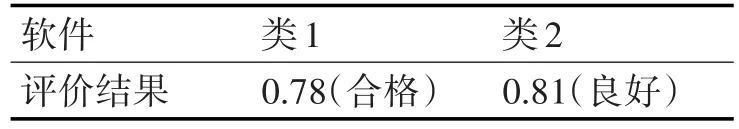

根据式(2)和式(3)的计算的比分数值,结合改造后工具Alint自动分析的结果,类1和类2代码评价后的结果如下表9所示。

表9 类1和类2代码的评价结果

从表9中可以看出,被评软件中软件类1评分结果为0.78,达到了合格水平,软件类2评分结果为0.81,达到了良好水平。总体上看,类1的安全性较差,可综合性和基本结构设计相对较好,而类2的安全性较好,可综合性和基本结构设计相对较差。经对数据做人工分析,从安全性的影响严重程度上可以看出评价的结果和新设计的计算准则是基本吻合。

5 结语

目前FPGA软件代码静态质量度量中存在手段缺乏,不能有效满足实际工程需要的问题。针对这些问题,提出了新的代码静态质量度量方法,结合通用的软件质量模型,分析度量元与加权系数,给出评价方法、评价规则和评价流程,并对商业工具Alint做了改造,最后通过实例对方法进行了有效验证,为FPGA软件测试的代码静态度量建立了一套有效的评价标准。当然,评价标准需求经过实践不断验证和不断的改良,评价度量元和加权系数也是需要在实践中不断验证而修改和补充。

[1]邸志雄.HDL代码质量评估方法关键技术研究与电路性能优化[D].西安:西安电子科技大学,2013.DI Zhixiong.Research on key techniques and circuit per⁃formance optimization of HDL code quality assessment method[D].Xi'an:Xi'an Electronic and Science Universi⁃ty,2013.

[2]Ronny F,Steffen R,Torsten S,et al.Use of HDL code checkers to support the IP entrance check-a requirement analysis[C]//Proceedings of the Euromicro Symposium on Digital System Design,IEEE,2002:364-370.

[3]中国电子技术标准化研究所.软件工程产品质量:第3部分 内部度量:GB/T 16260.3-2006[S].北京:中国标准化出版社,2006:5.China Electronic Technology Standardization Research In⁃stitute.software engineering product quality:Part 3 Inter⁃nal metrics:GB/T 16260.3-2006[S].Beijing:China Stan⁃dardization press,2006:5.

[4]Ali I,Karima M,Alain A.On the Use of Software Quality Standard ISO_IEC9126 in Mobile Environments[C]//20th Asia-Pacific Software Engineering Conference,IEEE,2013:1-8.

[5]中国人民解放军总装备部司令部.榴弹发射器定型试验规程:GJB 2423A-2009[S].北京:中国标准化出版社,2009:44.General Armament Department of the people's Liberation Army.Test procedures for setting the grenade launcher:GJB 2423A-2009[S].Beijing:China Standardization press,2009:44.

[6]张雁,林英,王红菘.面向对象软件度量的研究[J].计算机与数字工程,2009,37(3):117-119.ZHANG Yan,LIN Ying,WANG Hongsong.The research object-oriented software metrics[J].Computer and Digital Engineering,2009,37(3):117-119.

[7]中国人民解放军总装备部电子信息基础部.军用软件安全性设计指南:GJB/Z 102A-2012[S].北京:总装备部军标出版发行部,2012.General Armament Department of the Chinese people's Liberation Army.Military software security design guide:GJB/Z 102A-2012[S].BeiJing:The General Armament Department military standard publishig department,2012.

[8]吴继华.设计与验证Verilog HDL[M].北京:人民邮电出版社出版,2006:77-81.WU Jihua.Design and verification Verilog HDL[M].Bei⁃jing:People post and Telecommunications Press,2006:77-81.

[9]中国人民解放军总装备部电子信息基础部.军用软件质量度量:GJB 5236-2004[S].北京:中国标准化出版社,2004:4-5.General Armament Department of the Chinese people's Liberation Army.Military software quality metrics:GJB 5236-2004[S].Beijing:China Standardization press,2004:4-5.

[10]孙梦,宋晓秋,巢翌.软件程序代码质量度量技术研究[J].计算机工程与设计,2016,27(2):325-327.SUN Meng,SONG Xiaoqiu,CHAO Yi.Quality measure⁃ment technology research in software[J].Computer Engi⁃neering and Design,2016,27(2):325-327.

Static Quality Measurement of FPGA Software

LI Chenyang

(China Electronic Technology Group Corporation Tenth Research Institute,Chengdu 610036)

Lacking for efficiently evaluating FPGA software quality in use business tool,based on the study of software static quality evaluation models,the characteristic of FPGA software structure,a static quality evaluation method is proposed for software,and the evaluation results are expressed by quantitative data and presented by evaluating arithmeticand evaluating flow,and reform to the business tool Alint quantity evaluation system,then it is used in actual case.Experiment result shows the proposed method can evaluate software static quality efficiently,and indicate a newpath for evaluating the quality level of FPGA software,and then the subjectivity during software evaluation can be reduced.

FPGA software,static quality,metrics,rule set,weight

Class Number TP312

TP312

10.3969/j.issn.1672-9722.2017.12.047

2017年6月5日,

2017年7月24日

李晨阳,男,硕士,工程师,研究方向:FPGA软件测试、数字信号处理。