基于USB接口多位数据格式的高速传输系统∗

2018-01-04张锦鹏赵建军唐海峰

张锦鹏 赵建军 唐海峰 赵 恩

(昆明理工大学理学院 昆明 650500)

基于USB接口多位数据格式的高速传输系统∗

张锦鹏 赵建军 唐海峰 赵 恩

(昆明理工大学理学院 昆明 650500)

该设计实现了一种基于USB2.0接口的数据传输系统。该系统由FPGA产生一个35位自加到250清0的计数器,实现通过USB把计数器的数值传送到上位机的功能。该设计采用的FPGA芯片为Altera公司的CycloneII EP2C5Q208C8N,USB芯片为Cypress公司EZ-USB系列的CY7C68013A。通过Quartus II软件,Keil软件,Cypress控制台进行USB接口多位数据传输系统的设计。该系统可用于高精度、高速度、低成本的批量数据传输。

FPGA;USB;数据传输;Cypress

1 引言

USB又称为串行数据接口,具有高速率传输数据,即插即用的优点。USB2.0标准规定其传输速率高达480Mbps,它已经成为目前电脑中的标准扩展接口[1~3]。本系统设计的目的是通过 FPGA 产生一个35位自加到250清零的计数器,实现通过USB把计数器的数值传送到上位机,最终实现一种基于CY7C68013A的USB数据传输系统。

2 系统总体设计方案

本设计通过FPGA产生一个35位自加到250清零的计数器,通过USB把计数器的数值传送到上位机。因为USB的数据位宽为16,计数器为35位,因此需要分开传送。图1所示为本设计的RTL(Register Transfer Level)视图。

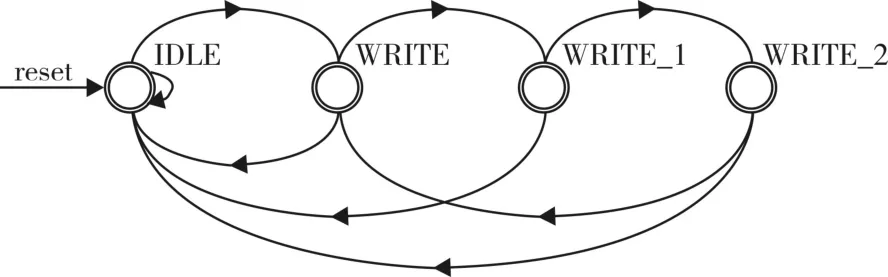

图1中的datagen产生一个cnt的35位计数器,由于要分三次传送所以计数器的时钟驱动为USB时钟的三分频。USB模块为USB的传输模块,通过USB传输到上位机的功能实现就在此模块中实现。其中图2所示为USB模块设计的状态机流程图。

EZ-USB系列的USB控制器主要通过两种模式进行传输:Slave FIFO和General ProgrammableInterface(GPIF)。在本文中就是通过Slave FIFO模式下实现USB数据传输[4]。

图1 系统RTL视图

图2 状态机流程图

尽管一些USB的设备可以使用EZ-USB中的CPU直接处理USB数据,但大部分情况只是将EZ-USB作为USB与外部处理数据逻辑的一种管道。USB数据流通过EZ-USB内部的端点FIFOs在主机和从机中流动。对于外部逻辑而言,这些端点FIFOs提供了时钟信号、握手信号、读写使能和输出使能等[5]。而其端点FIFO由外部逻辑产生,这就是Slave FIFO模式即从模式。

本设计所采用的Slave FIFO模式设计,也就是对FIFO进行写操作把数据传送到上位机。当有写事件发生时,进入WRITE状态,写入cnt[15:0],若FIFO非满则跳转WRITE_1状态,不然跳回IDLE状态;在WRITE_1状态,写入cnt[34:32],其余高位补零,若FIFO非满则跳转到WRITE_2状态,不然跳回 IDLE状态;在 WRITE_2状态,写入 cnt[31:16],若FIFO非跳转到WRITE状态,则跳回IDLE状态[6]。其中注意,WRITE_1状态和WRITE_2状态传输的cnt位数不能交换。

3 系统硬件设计

3.1 系统硬件框图

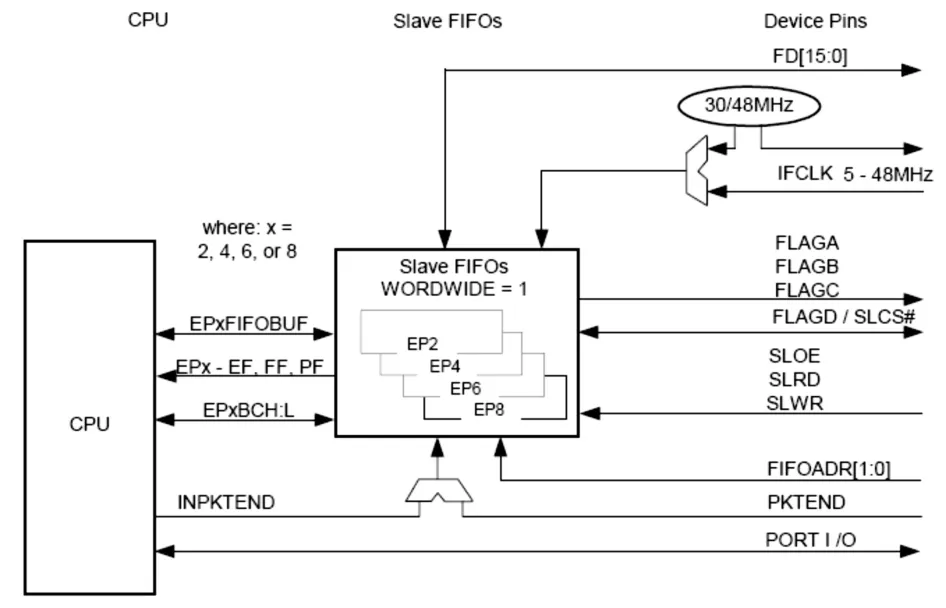

本设计采用FPGA作为控制器件,其控制USB接口芯片CY7C68013A。下图3为USB器件工作在Slave FIFO模式下时USB和FPGA的典型电路连接图。

设计是采用同步的方式,在IFCLK为上升沿的时候SLRD,SLWR有效[7]。当IFCLK为上升沿时SLWR有效,FD的数据写入FIFO中。当IFCLK为上升沿时SLRD有效,FIFO中的数据读出。其中SLWR 和 SLRD 为低有效[8~10]。

3.2 FPGA与USB简介

本设计中所采用的控制器件FPGA芯片为Al⁃tera公司的CycloneII EP2C5Q208C8N,USB芯片为Cypress公司的 EZ-USB 系列的 CY7C68013A[11]。其中EP2C5Q208C8N芯片拥有4608个逻辑单元,片上RAM共计119808 bits,13个18*18硬件乘法器,2个高性能PLL以及多达142个用户自定义IO[12]。板上提供了大容量的SDRAM和Flash ROM等存储单元。标准的2.54mm间距的扩展插座供用户方便使用。电源管理模块只需要外接DC-5V电源即可。该芯片本身具有低成本、高性能、低功耗等优点,因此这里选用该器件作为控制器件。

该USB芯片CY7C68013A是Cypress半导体公司EZ-USB系列的一款USB控制器芯片[13]。CY7C68013A芯片具有以下几个显著特点:内部集成工业标准的8051处理器[14];全USB吞吐量;基于RAM的架构设计允许无限制的配置和升级;自动处理USB协议,为用户设计大大简化了代码。其中图4所示为EZ-USB系列芯片的内部框架图。可以在图4中明显看到该系列芯片内部集成了48MHz的8051处理器,外部具有PHY(物理层)接口。在设计中比较关注的就是8051的处理器的配置,对USB寄存器的配置,对FIFOs的读写操作。在CY7C68013A中具有4片FIFO,每一片FIFO对应一个端点EP。实现USB的传输工作主要就是对这4片FIFO进行读写操作[15]。

图4 EZ-USB系列芯片的内部框架图

在进行USB传输设计工作时,要先对CY7C68013A内部的寄存器进行配置,该工作是必不可少的,目地是配置USB的一些工作方式[16]。

3.3 USB的传输方式

本设计采用Slave FIFO的模式。图5所示为Slave FIFO在EZ-USB系统中的角色。

图5 Slave FIFO在EZ-USB系统中的角色

其中在Slave FIFOs中可以看见有EP2,EP4,EP6,EP8四片FIFO。IFCLK为USB的内部时钟信号,本设计采用48MHz。其中FLAGA,B,C,D为在固件设计中的标志位,由固件程序所确定。SLOE为输出使能信号。SLRD为读信号,SLWR为写信号。FIFO的选择通过FIFOADR[1:0]来确定。当FIFOADR为00时选择EP2;01时选择EP4;10时选择 EP6;11 时选择EP8[17]。FD[15:0]表示为 16位的USB数据信号,也可以通过固件程序选择为8位的数据信号。PKTEND表示为一个包结束的信号。

4 系统软件设计

在进行USB的设计中,主要分别对USB内部固件程序的编写和对FPGA的USB接口设计[3]。完成了这两步后就可以利用Cypress公司官方提供的Cyconsole EZ-USB上位机软件对USB的数据进行接收。

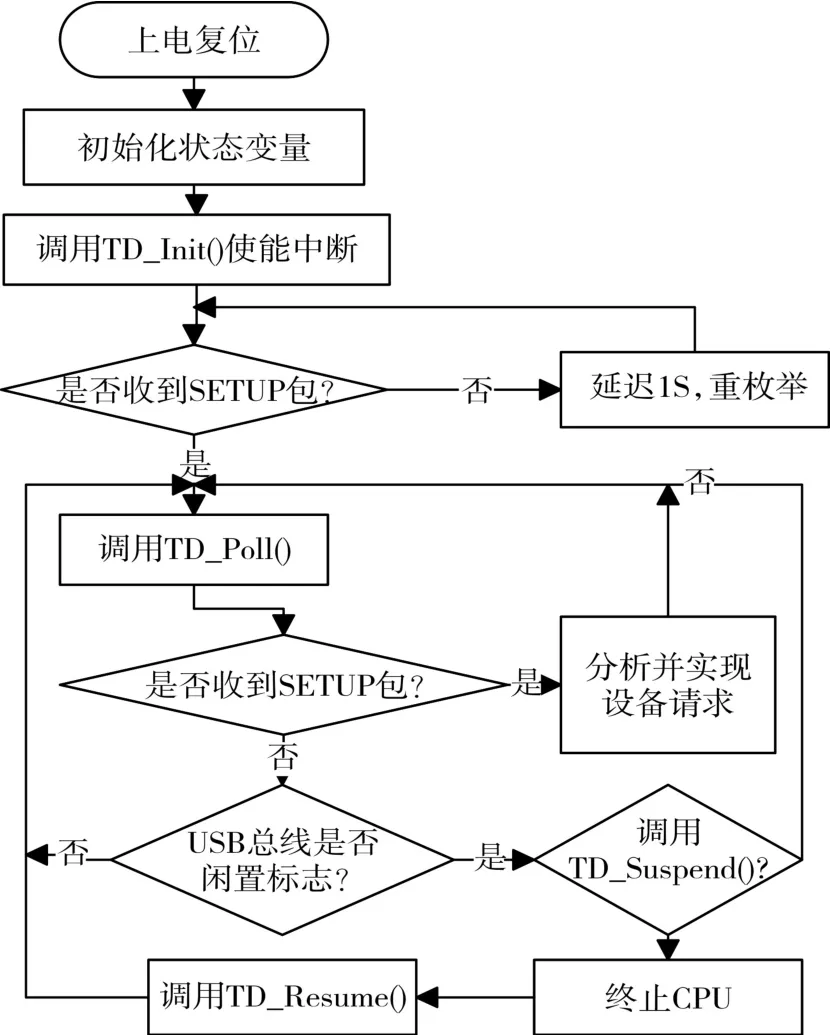

4.1 设计固件程序

在对USB的芯片介绍中,CY7C68013A内部集成了一个51单片机的内核作为处理器,并且有许多对USB功能协议控制的寄存器。对固件程序的设计简单而言就是对USB内部寄存器的配置,通过对这些寄存器的配置来对USB的模式、传输位数、端点的接收情况等进行设置。其中图6为对固件程序设计的流程图。

图6 固件程序流程图

CY7C68013A内部的寄存器都是8位,其中TD_Init()函数是对CY7C68013A芯片进行初始化工作[18],即CPU的工作频率设置、USB的传输模式设置、FLAGA、B、C、D管脚进行设置以及对端点操作的设置等。TD_Poll()主要对数据进行搬移,循环调用。对固件程序的修改主要也就是修改TD_Init()和TD_Poll()两个函数[19~21]。

4.2 设计FPGA产生计数器和USB通信

1)计数器通过USB传送到上位机

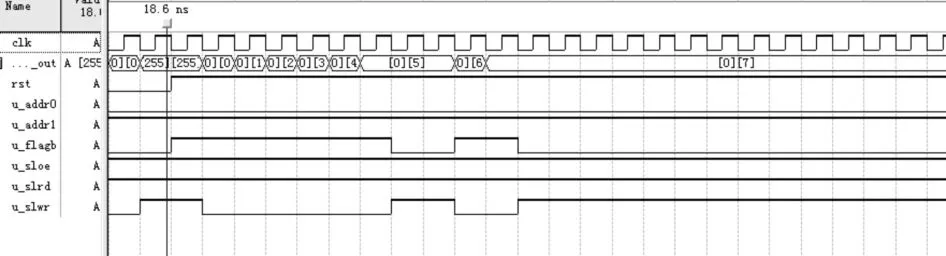

在FPGA内部产生一个16位计数器,计数到250时清零重新计数。通过USB传送到上位机。采用写FIFO的方式进行设计,设计具体方法同步写FIFO设计中,FPGA内部产生1个16位递增计数器写入FX2 FIFO中,并通过FX2发送到上位机,如果FX2内部FIFO满,则计数器停止计数,非满则计数并写入FX2的FIFO中[22]。图7为设计的仿真波形。

图7 系统仿真波形

当u_flagb为高时进入写状态,u_slwr为低有效开始写入FIFO。当u_flagb为低时进入IDLE状态停止写,此时u_slwr为高。在此情况下data_out数据一直保存不变直到u_flagb发生变化。下载到FPGA开发板,用Cypress控制台进行测试。本设计把FPGA的数据传送到EP6,其他端点并不使用。所以这边只用EP6进行接收数据即可[23]。

通过图7所示可以看出实验达到了预期效果,由FPGA内部产生的一个计数器通过USB传送到了上位机。

2)异步FIFO的测试

通过异步FIFO改变使频率相匹配,异步FIFO的RTL视图如图8所示。

图8 异步FIFO的RTL视图

其中wr_clk为写时钟,wr_en为写使能信号;rd_clk为读时钟,rd_en为读使能信号;din为输入管脚;dout为FIFO输出管脚;empty为空标志位;full为满标志位。rst为复位信号,此为低电平有效。图9所示为FIFO的仿真波形图。

图9 FIFO的仿真波形图

其中clk_1为clk的两分频,cnt为0~9的计数器,dout为FIFO的输出信号。利用异步FIFO改变数据输入输出的频率大小。在此注意FIFO的rst为低电平有效,wr和rd信号必须作为output不然波形无法出现。由图9可以看出使数据的频率发生了变化达到了预期的效果。

3)三分频的测试

把频率clk进行三分频测试,设计两位的计数器记到2时清零。当计数到2时clk_out为1,其余的为0。由于是时序逻辑,所以得到的结果是在00时clk_out为0。图10所示为仿真波形。

图10 仿真波形

其中clk为主频,clk_out为三分频后的频率。由图10所示可以看出clk_out的时钟为clk的三倍,可得设计正确。

5 系统功能测试

本设计的USB固件程序利用官方提供的固件库,把EP6改成IN,大小为512即可。换句话而言就是本设计只利用EP6做为接收,其余不变。当打开Cypress官方提供的控制台后下载固件,跳到EP6上进行接收。

最后 WRITE 状态将 cnt[15:0]传送给 data,WRITE_1 状态 将 cnt[34:32]加 1 传送给 data,WRITE_2状态将cnt[31:16]加1传送给data。结果由Cypress控制台打出,如图11所示。

图11 EZ-USB对采集数据的测试结果图

其中图11所示的传输到上位机端的数据与所采集的数据一致,验证了系统的可行性。

6 结语

本文利用CY7C68013A芯片对计数器数据进行传输。首先完成了对USB内部固件程序的配置,再对FPGA内部产生数据通过USB控制模块对FP⁃GA内部信号进行发送。最后利用Cypress公司提供的EZ-USB Interface界面对USB发送来的数据进行采集,验证了系统的可行性。因此本系统可用于高精度、高速度、低成本的批量数据传输。

[1]马伟.计算机USB系统原理及其主/从机设计[M].北京:北京航空航天大学出版社,2004:7-8.MA Wei.Computer USB system principle and its master/slave design[M].Beijing:Beijing University of Aeronau⁃tics and Astronautics Press,2004:7-8.

[2]边海龙,贾少华.USB2.0设备的设计与开发[M].北京:人民邮电出版社,2004.1:15-17.BIAN Hailong,JIA Shaohua.USB2.0 device design and development[M].Beijing:People's Posts and Telecommu⁃nications Press,2004.1:15-17.

[3]罗向东.基于FPGA与CY7C68013A的USB接口系统设计[J].科技广场,2010(6):96-98.LUO Xiangdong.Design of USB Interface Based on FPGA and CY7C68013A[J].Technology Square,2010(6):96-98.

[4]马俊涛,李振宇.Slave FIFO模式CY7C68013和FPGA的数据通信[J].中国传媒大学学报(自然科学版),2009,16(2):38-44.MA Juntao,LI Zhenyu.Data Communication of Slave FIFO Mode CY7C68013 and FPGA[J].Journal of Commu⁃nication University of China(Natural Science),2009,16(2):38-44.

[5]任莉.基于USB2.0构建分布式偏振耦合测试仪数据采集系统[D].天津:天津大学,2006.REN Li.Design of Data Acquisition System for Distributed Polarization Coupling Analyzer with USB2.0 Protocols[D].Tianjin:Tianjin University,2006.

[6]陈续.GNSS卫星中频信号采集器的设计与实现[D].北京:北京邮电大学,2010.CHEN Xu.Design and Implementation of GNSS Satellite IF Signal Collector[D].Beijing:Beijing University of Posts and Telecommunications,2010.

[7]于健.基于FPGA和DSP成像信号处理板设计[D].西安:西安电子科技大学,2009.YU Jian.Design of SAR Imaging Signal Processer Based on FPGA and DSP[D].Xi'an:Xidian University,2009.

[8]马玲.基于FPGA和USB2.0的数据采集系统[J].电子世界,2014:22-23.MA Ling.Data Acquisition System Based on FPGA and USB2.0[J].Electronic World,2014:22-23.

[9]张俊涛,王豫莹.基于FPGA和USB2.0的高速数据采集系统[J].仪表技术与传感器,2011(10):46-48.ZHANG Juntao,WANG Yuying.High Speed Data Acquisi⁃tion System Based on FPGA and USB2.0[J].Instrumenta⁃tion Technology and Sensor,2011(10):46-48.

[10]闫成彦.基于USB的阵线CCD图像采集系统[D].大连:大连理工大学,2009.YAN Chengyan.Fuzzy CCD Image Acquisition System Based on USB[D].Dalian:Dalian University of Technol⁃ogy,2009.

[11]吕超,张玉霞,王立欣.USB接口高速数据传输的实现[J].计算机测量与控制,2009,17(5):1003-1005.LU Chao,ZHANG Yuxia,WANG Lixin.Realization of High-speed Data Transmission Based on USB Interface[J].Computer Measurement and Control,2009,17(5):1003-1005.

[12]张伯约,王丽卿.基于本地交通网络服务的电子辅助驾驶系统[J].微型机与应用,2015,34(9):68-70.ZHANG Boyao,WANG Liqing.Electronic Auxiliary Driving System Based on Local Traffic Network Service[J].Microcomputer And Applications,2015,34(9):68-70.

[13]星硕工控科技.FCUSB-CY7C68013-56开发文档,2004.12:8-10.Star Shuo Industrial Technology Development.FCUSB-CY7C68013-56 development document,2004.12:8-10.

[14]刘胜,陈华,聂雄.基于EZ-USB FX2的图像采集系统的 设 计 与 实 现[J].电 子 设 计 工 程 ,2011(11):160-162.LIN Sheng,CHEN Hua,NIE Xiong.Design and Imple⁃mentation of Image Capturing System Based on EZ-USB FX2[J].Electronic Design Engineering,2011(11):160-162.

[15]甘建伟,秦付军,王鹏.基于FPGA的高速多通道数据采集系统设计[J].测控技术与仪表技术,2013(39):55-57.GAN Jianwei,QIN Fujun,WANG Peng.Design of Multi-channelHigh-speedDataAcquisition System Based on FPGA[J].Journal of Measurement and Control Technology and Instrumentation,2013(39):55-57.

[16]袁益民.基于USB2.0+FPGA的密码算法硬件设计平台设计[D].长沙:中南大学,2008.YUAN Yimin.USB2.0+FPGA based cryptographic algo⁃rithm hardware platform[D].Changsha:Central South University,2008.

[17]纪超,刘慧英,孙景峰,等.虚拟与现实交互中跟踪系统的改进设计[J].计算机测量与控制,2014,22(2):528-530.JI Chao,LIU Huiying,SUN Jingfeng,et al.Design Im⁃provements of Tracking System in Virtual and Reality In⁃teraction[J].Computer Measurement and Control,2014,22(2):528-530.

[18]张建喜,汪峰,李金海,等.基于USB的GPS数据采集系统[J].电讯技术,2010(6):96-100.ZHANG Jianxi,WANG Feng,LI Jinhai,et al.A GPS Da⁃ta Acquisition System Based on USB[J].Telecommuni⁃cations Technology,2010(6):96-100.

[19]刘志才,郭付才,彭新伟,等.基于CY7C68013A的FP⁃GA配置和通信接口[J].电子技术应用,2013(2):18-21.LIU Zhihua,GUO Fucai,PENG Xinwei,et al.Design of the FPGA's Configuration and Communication Interface Based on CY7C68013A[J].Journal of Electronic Tech⁃nique,2013(2):18-21.

[20]王红凯.基于CY7C68013A的USB接口系统设计[J].现代机械,2008(1):77-79.WANG Hongkai.Design of USB Interface Based on CY7C68013A[J].Modern Machinery,2008(1):77-79.

[21]张超,李洪文,朱丹丹,等.基于USB的高速数据传输系统设计[J].计算机应用,2013(z2):54-56.ZHANG Chao,LI Hongwen,ZHU Dandan,et al.Design of a High-speed Data Transmission System Based on USB[J].Journal of Computer Applications,2013(z2):54-56.

[22]刘世银.基于USB的数据采集系统研究与设计[D].武汉:武汉理工大学,2013.LIU Shiyin.Research and Design of USB-based Data Ac⁃quisition System[D].Wuhan:Wuhan University of Tech⁃nology,2013.

[23]唐海峰.基于FPGA的时间测量电路的研究[D].昆明:昆明理工大学,2016.TANG Haifeng.The Research of Time Measurement Cir⁃cuit Based on FPGA[D].Kunming:Kunming University of Science and Technology,2016.

High Speed Transmission System Based on USB Interface Multi Bit Data Format

ZHANG JinpengZHAO Jianjun TANG HaifengZHAO En

(College of Science,Kunming University of Science and Technology,Kunming 650500)

This design realizes a data transmission system based on USB2.0 interface.The system from the FPGA to produce a 35-bit added to 250 from 0 of the counter,to achieve the value of the counter through the USB to the host computer's function.The design of the FPGA chip uses Altera's CycloneII EP2C5Q208C8N,USB chip Cypress's EZ-USB series CY7C68013A.Through the Quartus II software,Keil software,Cypress console for USB interface design of multi-bit data transmission system.The system can be used for high-precision,high-speed,low-cost bulk data transmission.

FPGA,USB,data transmission,Cypress

Class Number TN919.3

TN919.3

10.3969/j.issn.1672-9722.2017.12.026

2017年6月21日,

2017年7月28日

国家自然科学基金青年科学基金项目(编号:11103069)资助。

张锦鹏,男,硕士研究生,研究方向:嵌入式系统、云计算、交通物联网。赵建军,男,硕士,副教授,研究方向:X射线脉冲星导航、嵌入式系统、物联网数据融合、云计算、交通物联网。唐海峰,男,硕士研究生,研究方向:X射线脉冲星导航、嵌入式系统。赵恩,女,硕士研究生,研究方向:嵌入式系统。