一种低温度系数高电源抑制比带隙基准

2017-12-23奚冬杰杜士才

奚冬杰,杜士才

(中国电子科技集团公司第五十八研究所,江苏 无锡 214072)

一种低温度系数高电源抑制比带隙基准

奚冬杰,杜士才

(中国电子科技集团公司第五十八研究所,江苏 无锡 214072)

提出了一种基于基极电流补偿的具有低温度系数和高电源抑制比的带隙基准电压源结构,通过消除三极管基极电流对基准输出电压温度系数的影响,有效降低了基准的温漂系数,同时通过自偏置电流镜结构和滤波电容提高了基准在全频段的电源抑制比(PSRR)。Cadence中利用TSMC 0.18 μm工艺进行的仿真结果表明,在-55~125℃的温度范围内,得到9.1×10-6/℃的温漂系数,低频时的电源抑制比达到-80 dB。

基极电流补偿;低温漂系数;高电源抑制比

1 引言

现代集成电路设计中,电压基准源是一个使用广泛不可或缺的模块[1]。DC-DC电源电路、数模和模数转换器、数字集成电路以及混合信号集成电路中都需要获得一个不随电源以及温度变化而变化的电压基准源,作为参考电位以实现电路功能。电压基准源会显著影响整个电路的功耗、速度、效率和性能,因此设计者对其的优化是提高整个系统性能的前提[1~3]。

本文首先介绍了传统电压带隙基准源的理论原理,然后给出其电路图和输出基准电压表达式。针对其温度系数过大、电源抑制比过低等问题,提出一种具有基极电流补偿的带隙基准结构。该电路通过在恰当的节点上增加额外的电阻,然后利用其压降来消除三极管基极电流对基准输出电压温度系数的影响。其次提出一种在不同频率段利用不同方法来改善电路PSRR特性的思路:在中低频时利用自偏置共源共栅电路的高阻抗以及额外的正反馈支路来提高PSRR,在高频时利用滤波电容来提高PSRR。最终电路在整个频率段内都具有良好的PSRR特性。

2 电路分析与设计

2.1 传统电压带隙基准电路

由半导体理论可知,两个工作在不同电流密度下的三极管的基极发射极电压(VBE)的差值具有正温度特性,同时三极管的基极发射极电压(VBE)具有负温度特性[4]。因此如果将上述两种具有不同温度系数的电压配以一定的加权系数比例进行相加后就能得到不随温度变化而变化的基准电压源。

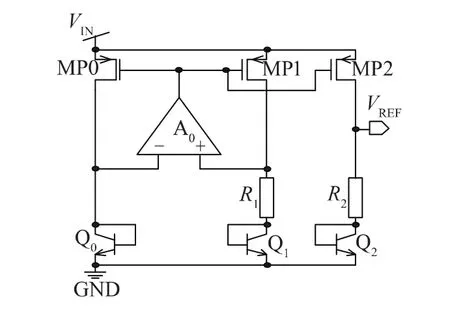

图1 传统带隙基准电压源

传统带隙基准电压源结构如图1所示,包含运算放大器、电流镜、电阻、三极管以及基准输出支路。利用运算放大器对其输入端的箝位作用以及电流镜的镜像作用可保证流过三极管Q0和Q1的电流相等。基准输出支路由MOS管MP2、电阻R2和三极管Q2组成,基准电压在电阻R2的上端输出[5]。忽略三极管的基极电流,三极管Q0和Q1基极和发射极的压差为:

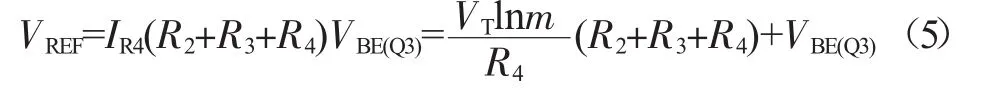

其中n为三极管Q1和Q0的发射极面积之比,VT为热电压,常温下为26 mV。电阻R1上的压降为(1)式中所求 ΔVBE,MOS 管 MP0、MP1、MP2 尺寸相同,由此可得基准输出电压为:

在传统带隙基准的电路结构和工作原理推导中有两点值得注意:(1)在求解ΔVBE时我们认为三极管Q0和Q1的发射极和集电极的电流相等,忽略了两者的基极电流[6],但实际上在CMOS工艺中由于三极管的β值是有限值,因此基极电流不能忽略,其存在会使基准输出产生较大温漂;(2)由于采用了运放箝位的结构,因此整个带隙电路的电源抑制比受运放带宽的限制[7~8]。

2.2 新型电压带隙基准电路

为了消除三极管基极电流对基准电压温度系数的影响,本文提出了一种具有基极电流补偿的基准电路,图2为其核心部分电路图。

图2 基于基极电流补偿带隙的核心部分

自偏置共源共栅电流镜,MP4、MP5、MP6、MP7 和R5通过镜像电流确保三极管Q1和Q2的集电极电流ICQ1和ICQ2相等。

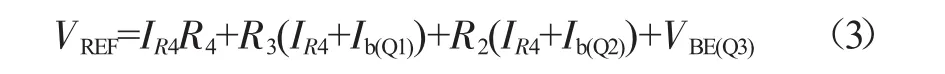

因此有:

其中Ib(Q1)和Ib(Q2)为三极管Q1和Q2的基极电流。m为三极管Q1和Q2的发射极面积之比。如果让

电阻R2和R3的阻值相等,则有:

图3为低温度系数高电源抑制比带隙基准结构图,虚线左边为其启动电路。使能信号EN高为无效状态,MP9和MP10不导通,EN低为有效状态。当EN为低有效,且电源开始上电后,启动电路通过MN1从B点抽取电流使其电位下降,同时通过MP3向A点注入电流使其电位上升,最终使基准核心环路摆脱电流为零的状态。当基准环路建立以后通过电流镜MP0、MP4和MP5的镜像作用对电容C0进行充电,最终关断MN1和MP3,使得启动电路退出,结束对基准环路的影响。

图3低温度系数高电源抑制比带隙基准结构图

图3 中的电路采用自偏置共源共栅结构,为自己提供偏置电流,这样提高了电路低频时的电源抑制比。低频时共源共栅电流镜的高输出阻抗提高了基准的环路增益,且由 MP1、MP4、MP6、R5、MN2 和 MN3 构成的正反馈环路加速了MP4栅极电压跟随电源变化的速度(MP4栅极升高→MN2栅极降低→MP4栅极升高)。在高频时通过电容C1将A点短路到地,且在基准输出处增加了电容C3进行一阶RC滤波,进一步提高了基准输出的稳定性,最终维持了基准偏置电流的稳定,因此减小了MP4栅极受电源影响的程度。

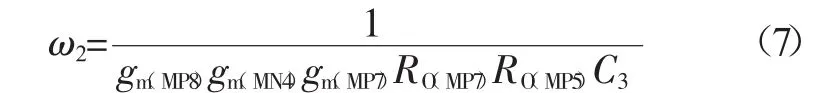

基准核心部分包含有正负两条反馈环路,从VREF→R3→Q1→MN3→MP4→MP5→MP8→VREF为负反馈,从 VREF→R3→Q2→MN4→MP5→MP8→VREF为正反馈。由于电阻R3、R4和R2的分压特性,确保了负反馈支路的增益大于正反馈支路的增益。C2跨接在MN4源端和基准输出端的补偿结构不但避免了左半平面的零点,而且将环路的次级点外推到一个很高的频率。

主极点频率为:

其中在LDO输出端电阻ROUT≈R6。

次极点频率为:

此时次极点相比于普通的米勒补偿提高了由MN4、MP7和MP5组成的共基极放大器所能提供的增益的倍数,使得环路更稳定且带宽更大。

3 仿真结果及其分析

采用TSMC 0.18 μm设计工艺,仿真工具为spectre,仿真条件[8]为电源电压2.5~5V,温度-55~125 ℃。

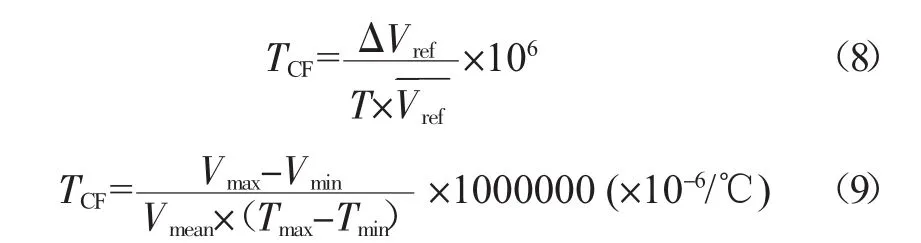

温漂系数是衡量带隙基准电压源输出电压随温度变化的一个性能参数,单位为×10-6/℃,表示当温度变化1℃时,输出电压变化的百万分比。其计算公式为[(基准电压最大值-基准电压最小值)/(基准电压的平均值×温度范围)]×1000000,符号表达式如式(8)、(9)所示:

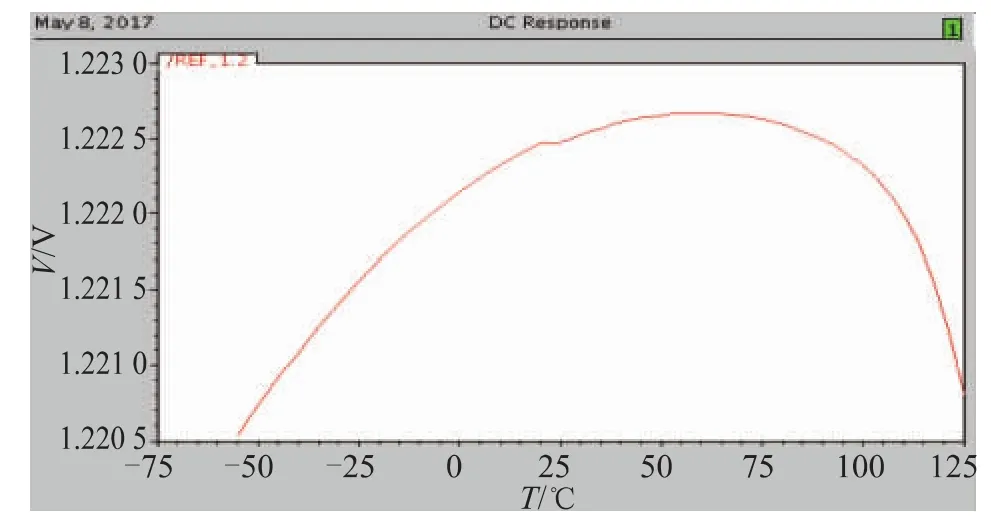

图4 基准温度系数的仿真

通过式(8)和图4的仿真结果,我们可以计算出该基准的温度系数为9.1×10-6/℃。

虽然该基准仅仅进行了一阶温度特性补偿,但由于消除了三级管基极电流对输出电压的影响,因此依然具有很低的温度系数。表1列出了在各个工艺角下基准温度系数的仿真结果,从表1中可以看出温度系数最大不超过10×10-6/℃,满足低温度系数要求。

表1 各个工艺角下基准温度系数仿真结果

当基准外围的应用环境较复杂、电源上的波动对其干扰较大时,电源抑制比也是我们考量其性能的一个重要指标。

如图5的仿真结果所示,电路在低频时电源抑制比高达80 dB,中频时随着环路增益的下降,电源抑制比也开始下降。随着频率的进一步升高,在高频时由于输出端RC滤波网络的存在,电源抑制比又开始上升。

图5 基准电源抑制比的仿真

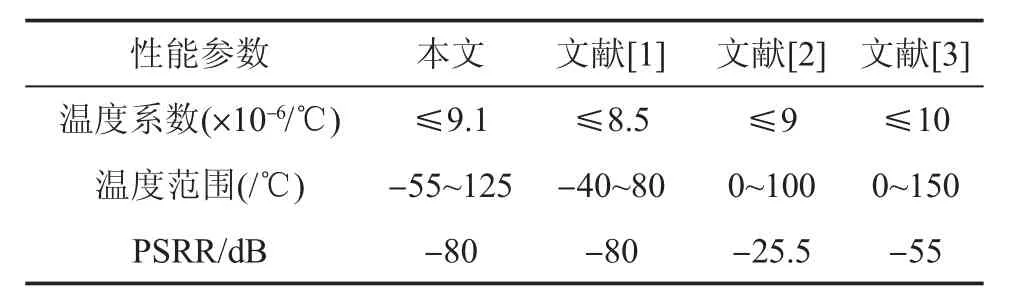

表2列出与本文设计相关的参考文献中的电路的比较结果,可以看出本文所设计的电路在性能上有一定优势。

表2 本设计和几种电路温度系数仿真结果对比

4 结论

本文设计了一种基于基极电流补偿的具有低温度系数和高电源抑制比的带隙基准电路。通过在合适节点添加额外电阻消除了三级管基极电流对基准输出电压的影响,因此仅仅采用一阶补偿的结构就得到了低至9.1×10-6/℃的温度系数。且通过在低频时利用共源共栅自偏置电流镜结构提高环路增益的方法得到低至-80 dB的PSRR,并在高频时利用电容对关键节点进行滤波避免受电源波动干扰的方法提高了全频段的PSRR。

[1]Fang H,Jian L V,Junsheng Y U,et al.Curvature Compensated CMOS Bandgap Voltage Reference for High Precision Application[J].Modern Electronics Technique,2010.

[2]Mattia O E.0.9 V,5 nW,9 ppm/℃Resistorless Sub-Bandgap Voltage Reference in 0.18 μm CMOS[C].Latin-American Symposium on Circuits and Systems,2014.

[3]Xing X,Wang Z,Li D.A low voltage high precision CMOS bandgap reference[C].Norchip,IEEE,2007:1-4.

[4]Chen J,Ni X,Mo B.A curvature compensated CMOS bandgap voltage reference for high precision applications[C].International Conference on Asic,IEEE,2008:510-513.

[5]Leung K N,Mok P K T,Chi Y L.A 2-V 23-μA 5.3-ppm/℃curvature-compensated CMOS bandgap voltage reference[J].Solid-State Circuits,IEEE Journal of,2003,38(3):561-564.

[6]Li J H,Zhang X B,Yu M Y,et al.A 10ppm/℃1.8 V piecewise curvature-corrected bandgap reference in 0.5 μm CMOS[C].Microelectronics&Electronics,2009.Prime Asia 2009.Asia Pacific Conference on Postgraduate Research in.IEEE,2010:416-419.

[7]RAZAVI B.Design of analog CMOS intergrated circuits[M].New York:McGraw-Hill Companies,2001:312-313.

[8]何乐年,王忆.模拟集成电路设计与仿真[M].北京:科学出版社,2008:198-199.

A Low Temperature Coefficient and High PSRR Bandgap Voltage Reference Source

XI Dongjie,DU Shicai

(China Electronics Technology Group Corporation No.58 Research Institute,Wuxi 214072,China)

The paper present a new kind of bandgap voltage reference source.By using base current compensation,it has a low temperature coefficient and a high PSRR.Through eliminating the transistor base current effect on the temperature coefficient of reference voltage,it effectively reduces the temperature drift coefficient of the circuit.At the same time by the using of self biased current mirror and filter capacitor,we improves the power supply rejection ratio of the circuit in full frequency.TSMC 0.18 μm process is adopted by the circuit,by the simulation result in Cadence,it shows that the temperature coefficient is 9.1×10-6/℃ and the PSRRreaches-80dBinlowfrequency.

base currentcompensation;low temperature coefficient;highPSRR

TN402

A

1681-1070(2017)12-0030-04

2017-07-01

奚冬杰(1989—),男,江苏无锡人,硕士学历,工程师,现从事集成电路中电源管理类的研究工作。