40 nm工艺SRAM型FPGA总剂量辐射效应研究

2017-12-23徐玉婷郭俊杰

徐玉婷,孙 静,郭俊杰,闫 华

(1.无锡中微亿芯有限公司,江苏 无锡 214072;2.中国电子科技集团公司第五十八研究所,江苏 无锡 214072)

40 nm工艺SRAM型FPGA总剂量辐射效应研究

徐玉婷1,孙 静1,郭俊杰2,闫 华1

(1.无锡中微亿芯有限公司,江苏 无锡 214072;2.中国电子科技集团公司第五十八研究所,江苏 无锡 214072)

对自主研发的40 nm工艺SRAM型FPGA电路的抗总剂量辐射能力进行摸底试验和分析。试验表明,采用普通商用40 nm工艺未做加固的FPGA电路抗总剂量辐射能力可达100 krad(Si),说明普通商用40 nm工艺本身具有一定的抗总剂量性能。同时验证了总剂量辐射引起的器件参数退化随栅氧化层厚度的减薄而下降。

40 nm;FPGA;总剂量辐射;试验

1 引言

当航天器和武器型号中所使用的电子元器件工作在电离总剂量辐射环境中时,会遭到高能粒子及光子的轰击,其工作参数及使用寿命不可避免地会受到影响和危害,严重时可引起航天系统失效,甚至导致航天事故[1]。FPGA(现场可编程门阵列)由于自身集成度高、面积小、功耗低、实现功能多等特点,在航天领域应用前景广泛。领先的抗辐射FPGA产品主要来自美国Micro semi、Xilinx、Atmel公司。而目前国内对抗辐射FPGA研究较少。因此,本文对自主研发的千万门级FPGA电路的总剂量辐射性能进行了摸底试验,对其总剂量效应进行了研究,为FPGA的抗辐射加固设计打下基础。

2 器件选择和试验方法

随着半导体工艺技术进入深亚微米乃至超深亚微米范围,MOS结构的栅氧化层厚度也随之减小。当栅氧化层厚度减小到一定程度时,总剂量辐射已无法在其中产生大量的辐射感生电荷,加上沟道电子可以通过遂穿效应进入氧化层中和部分辐射感生电荷,最终使总剂量辐射对薄栅氧化层的影响可以被忽略。一般认为深亚微米CMOS技术本身即是加固的,也称之为本征加固[2]。

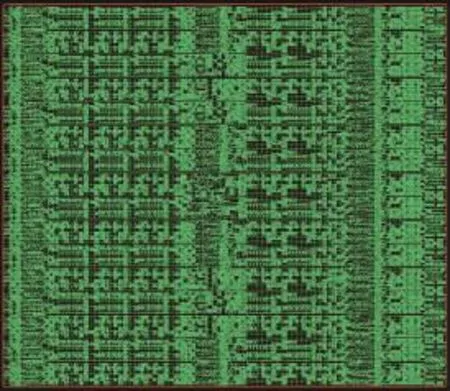

试验样品选用电路为某自主研发的千万门级FPGA电路(如图1所示),包括可编程逻辑单元、时钟管理模块、嵌入式BRAM、PCIE、IOB、DSP等多种功能模块。该电路采用40 nm商用工艺,芯片尺寸16.32 mm×14.07 mm,采用CCGA1136封装,内核电压1.0 V,端口电压1.2~3.3 V,辅助电压2.5 V。该电路未做加固设计,对其抗总剂量能力进行摸底。

图1 千万门级FPGA电路顶层版图

试验选用的辐射源是中科院上海应用物理研究所的水储式圆柱形排列的60Co源,辐射源强度为1.52×105Ci。试验过程选取15 rad(Si)/s的剂量率。4只器件辐照到100 krad(Si),试验过程中,每隔10 krad(Si)观察并记录电路内核电流变化,如电流没有明显变化,将其中2只器件追加辐射到150 krad(Si)。试验完成后,用干冰保存带回。辐照到100 krad(Si)的两只电路用测试机ultraflex测试功能和参数,并将150 krad(Si)的2只电路进行高温退火。高温退火条件为温度(100±5)℃,时间 168 h。168 h后进行参数测试。具体流程如图2所示。

图2 总剂量辐照试验流程

3 试验结果及分析

试验过程中,4只电路内核电流变化记录如表1和表2所示。监控的3路内核电流在100 krad(Si)以内无明显变化,3号片和4号片追加到150 krad(Si)后,内核电流也没有明显变化。

表1 剂量率15 rad(Si)/s、总剂量100 krad(Si)电路电流表

表2 追加到150 krad(Si)电路电流表

2只FPGA电路(1号片和2号片)在100 krad(Si)辐照过程中功能正常,用干冰保存带回,用ultraflex测试,电参数和功能测试均通过。另2只追加50 krad(Si)的电路(3号片和4号片)高温退火后进行测试,功能正常、电参数均在规定范围内。测试结果如表3所示。

表3 测试机测试结果列表

由此可见,在40 nm工艺下,总剂量辐射引起的器件参数退化及功能失效并不明显。采用普通商用40nm工艺设计的FPGA,虽无任何加固设计,仍具有一定的抗总剂量能力。

表4为100 k辐射剂量的1号片、150 k辐射剂量的3号片和退火后3号片相同测试项在ultraflex上的测试结果对比。对测试数据分析发现,不同的辐射剂量100 k和150 k对电路参数造成的影响差异很小,参数均满足测试规范要求。说明由于其栅氧化层厚度减小到一定程度,辐射剂量累积对半导体器件参数的影响已不明显。

表4 部分参数测试列表

4 结论

由实验结果分析可知,由于40 nm工艺的工艺特点,总剂量辐射所导致的半导体器件参数的退化以及功能的失效随栅氧厚度的减薄而下降,使得该自主FPGA电路本身具有一定的抗总剂量辐射能力。因此在深亚微米工艺下,总剂量不再是抗辐射加固设计的主要考虑因素。而随着晶体管特征尺寸的减小,单粒子效应越来越成为CMOS电子器件损伤的主要来源。因此针对40 nm工艺,如何对FPGA电路各个单粒子敏感模块进行加固设计,提升FPGA电路整体的抗单粒子辐射能力,是我们日后FPGA加固设计研究的重点。

[1]沈自才,丁义刚.抗辐射设计与辐射效应[M].北京:中国科学技术出版社,2015.

[2]刘远,恩云飞,李斌,等.先进工艺对MOS器件总剂量辐射效应的影响[J].半导体技术,2006,31(10):738-742.

[3]Johnson E,Wirthlin M,Caffrey M.Single-event upset simulationon an FPGA[C].Proceedings of the Engineering of Reconfigurable Systems and Algorithms (ERSA),LasVegas,Nevada,USA,2002.

[4]Battezzati N,Sterpone L,Violante M.Monte Carlo analysis of the effects of soft errors accumulation in SRAM-based FPGAs[J].IEEE Transactions on Computers,2008,55(4):3381-3387.

[5]Xilinx.Virtex-5 FPGA Configuration User Guide[P].2012.

Total Ionizing Dose Radiation Effects Test and Research of SRAM Type FPGA Based on 40 nm Process

XU Yuting1,SUN Jing1,GUO Junjie2,YAN Hua1

(1.East Technologies,inc.Wuxi 214072,China;2.China Electronic Technology Group No.58 Research Institute,Wuxi 214072,China)

The paper presents a research and test of total ionizing dose radiation effects of FPGA circuit based on 40 nm process.In our experiment,as the radiation total does rises to 100 krad(Si),the parameter and the function of unhardened device are normal after radiation.Experiment results prove that 40 nm CMOS transistors take ability to withstand TID by itself.It also verifies that device parameter degradation descends as the decrease ofthe oxide gate.

40nm;FPGA;TID;test

TN406

A

1681-1070(2017)12-0042-03

2017-09-13

徐玉婷(1983—),女,江西南昌人,硕士,工程师,研究方向为千万门级FPGA设计。