深亚微米SOI工艺的输出结构ESD研究

2017-12-23高国平黄登华

高国平,黄登华

(中国电子科技集团公司第五十八研究所,江苏 无锡 214072)

深亚微米SOI工艺的输出结构ESD研究

高国平,黄登华

(中国电子科技集团公司第五十八研究所,江苏 无锡 214072)

SOI(Silicon-On-Insulator)是一种在未来很有竞争优势的工艺技术,但由于其与体硅工艺结构上的不同,给其ESD设计带来了额外的挑战。通过串联的NMOS管来提高输出管的触发电压,以提升输出缓冲器的ESD能力。

SOI;ESD;输出缓冲器

1 引言

SOI(Silicon-On-Insulator)是一种在未来很有竞争优势的工艺技术,具有消除了Latch-Up、减小了寄生结电容等优点,但由于其与体硅工艺结构上的不同,给其ESD设计带来了额外的挑战。本文主要关注深亚微米部分耗尽型SOI工艺中输出缓冲器(Output Buffer)的ESD能力提高问题。

SOI(Silicon-On-Insulator)技术指的是在绝缘层上形成具有一定厚度的单晶半导体硅薄膜层的材料制备技术及在薄膜层上制造半导体器件的工艺技术。该技术可以实现完全的介质隔离,与用P-N结隔离的体硅器件相比,具有无闩锁、高速度、低功耗、集成度高、耐高温、耐辐射等优点[1]。根据SOI硅膜厚度可以将SOI器件分为厚膜器件和薄膜器件。对于厚膜SOI器件而言,当SOI硅膜厚度大于两倍的最大耗尽宽度时,被称为部分耗尽器件;对于薄膜SOI器件,当硅膜的厚度小于最大耗尽宽度时,称为全耗尽器件。

在SOI技术中,器件被制作在顶层很薄的硅膜中,器件与衬底之间由一层埋氧化层隔开。正是这种结构使得SOI/MOS器件具有功耗低等众多优点,比传统的体硅MOS工艺相比,更适合于高性能的ULSI和VLSI电路。

2 NMOS器件的ESD能力

从ESD保护分析,由于SOI工艺MOS器件在埋氧化层上方形成,与体硅相比,减小了器件的散热体积,所以器件的ESD保护能力大大减弱,尤其是输出NMOS。

目前国际上对SOI工艺电路的ESD保护多采用两种方式:(1)利用栅控二极管进行ESD保护,主要使用栅控二极管的正向导通特性;(2)采用动态开启的MOS管,主要使用MOS管和寄生栅控二极管同时导通。以上两种方式很难满足输入/输出端口多样的需求。

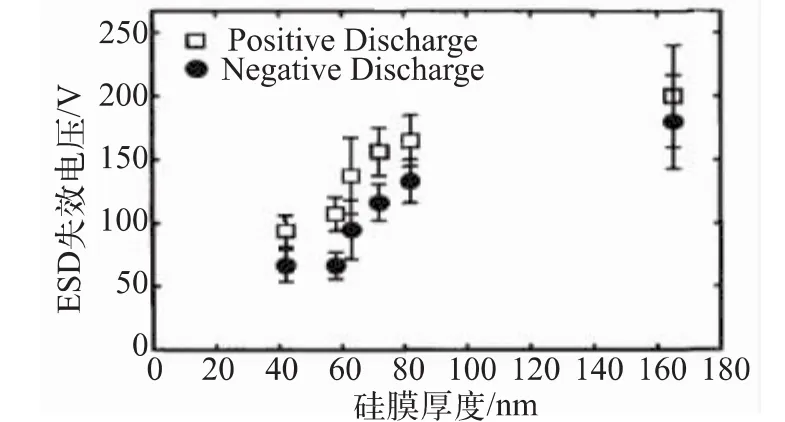

图1 体硅与SOI NMOS器件在正HBM ESD应力下的ESD失效电压比较示意图

图2 体硅与SOI NMOS器件在负HBM ESD应力下的ESD失效电压比较示意图

图1 、2是国外文献[1]关于SOI NMOS器件与体硅NMOS器件抗ESD水平的对照结果。在同一硅衬底材料上,利用特殊处理方法制造的两个尺寸和版图布局设计完全相同的SOI NMOS器件和体硅NMOS器件,两者在HBM正、负ESD应力下失效电压进行对比,SOI器件对ESD的承受能力远小于体硅器件,因此SOI电路的ESD能力已成为提高SOI电路可靠性的最大技术瓶颈之一。

本单位研发的一种0.18 μm SOI CMOS工艺设计的GGNMOS ESD结构,见图3。该工艺的硅膜厚度约为235 nm,接触孔到栅的距离(DCG)是2 μm。正向HBM模式下的抗ESD能力很差,没有通过100 V,其原因分析为SOI工艺散热性不如体硅,导致大量热量积累在P阱中。试验结果见表1。在正向ESD打击试验中,GGNMOS的ESD能力并未随着总器件宽度的增加而增加,因而在体硅工艺中常用于提高ESD能力的方法不能使用在SOI工艺中。

硅膜厚度是SOI工艺设计的一个关键参数[1]。在相同的功耗下,随着硅膜厚度的减小,由于散热能力的下降,硅的温度增加。更严重的问题是,薄的硅膜带来了更大的电阻和更高的电流密度,最终导致越薄的硅膜器件的ESD能力越低。图4是SOI工艺的硅膜厚度和ESD失效电压的关系示意图。

图3 GGNMOS的剖面图和电路图

表1 GGNMOS ESD应力测试结果

图4 SOI工艺硅膜厚度和ESD失效电压的关系示意图

3 常规的输出结构

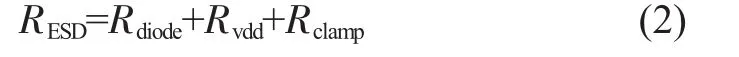

常规的输出结构见图5[2]。输出端口电压VIO在人体模型ESD打击时可用式(1)表示:

其中,Vdiode-on是二极管的导通电压(约1 V),Vclamp-on是电源与地之间的PowerClamp的导通电压(约0.5V),RESD是ESD路径上的导通电阻,可表示为:

其中,Rdiode是二极管的导通电阻,Rvdd是二极管和最近的Power Clamp之间的金属导线的电阻,Rclamp是Power Clamp的导通电阻。Rvdd需要保持尽可能小(小于 1 Ω)。

一个ESD结构的健壮性可表示为:

Vcrit表示I/O端口上最脆弱的地方。在输出结构中,最脆弱的通常是NMOS管的寄生NPN的触发电压Vt1。在图5中为了提高输出的健壮性,增加了电阻Rs,限制在NMOS管两端的电压。

图5 常规的输出结构图

4 ESD优化后的输出结构

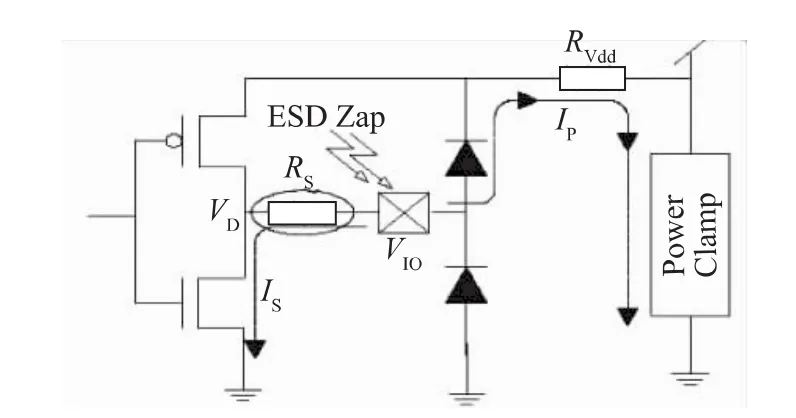

一款使用深亚微米PD-SOI工艺设计的电路的输出采用了图5的输出结构,未加电阻RS。在ESD2000V正脉冲打击时,输出NMOS管失效,输出结构版图和失效EMMI照片见图6。其中栅控二极管的击穿电压在10 V左右,PMOS、NMOS管的源漏击穿在12 V左右。栅控二极管的面积为1200 μm2。

图6 常规输出结构版图和失效EMMI照片

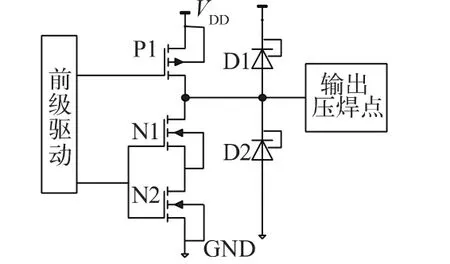

通过以上分析,为了进一步提高输出端口的健壮性,可以进一步提高Vcrit,即NMOS管寄生NPN的触发电压,采用图7的方式可把式(3)进一步表示为:

图7 ESD优化后的输出结构图

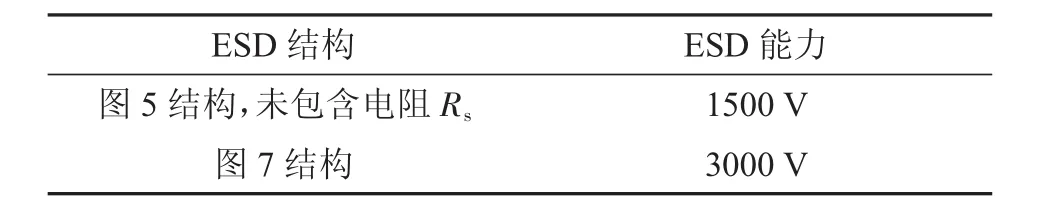

经过ESD优化后的输出结构,经试验验证,原本1500 V耐受的ESD能力提高到了3000 V。

表2 ESD优化前后的ESD测试结果

5 总结

本文介绍了SOI工艺的优势及其带来的ESD设计上的挑战,通过试验数据证实了SOI工艺中NMOS管的脆弱性。通过对常规输出结构的分析,利用SOI工艺的特点提出了一种提高输出端口ESD能力的新方法。经验证,该方法可以达到提高输出端口ESD能力的效果,并已成功应用于产品的ESD设计中。

[1]黄如,张国艳,李映雪,张兴.SOI CMOS技术及其应用[M].北京:科学出版社,2005.

[2]Mansun Chan,Selina S Yuen,Zhi-Jian Ma,Kelvin Y Hui,Ping K Ko,Chenming Hu.ESD Reliability and Protection Schemes in SOI CMOS Output Buffers[J].IEEE TRANSACTIONS ON ELECTRON DEVICES,1995,42(10).

[3]S Mitra,R Gauthier,A Salman,C Putnam,S Beebe,R Halbach,C Seguin.I/O Architecture for Improved ESD Protection In Deep Sub-Micron SOI Technologies[C].2006 IEEE International SOI Conference Proceedings.

Improved ESD Characteristics of Output Buffer in Deep Sub-Micron SOI Technology

GAO Guoping,HUANG Denghua

(China Electronics Technology Group Corporation No.58 Research Institute,Wuxi 214072,China)

Silicon-on-insulator(SOI)is a potential high-performance technology due to its inherent structural advantage over bulk Silicon-based technology.However,the structural differences create additional challenges for providing ESD protection in SOI devices.The paper utilizes SOI's structural advantage of series NMOS to improve ESDcharacteristicsofoutputbuffer.

SOI;ESD;outputbuffer

TN406

A

1681-1070(2017)12-0045-03

2017-08-11

高国平(1979—),男,浙江嘉善人,本科,现在中国电子科技集团公司第五十八研究所从事各类接口电路设计和可靠性研究工作。