ARINC659总线桥接的设计及对总线同步的影响分析

2017-12-15,,,

,,,

(北京空间飞行器总体设计部,北京 100094)

ARINC659总线桥接的设计及对总线同步的影响分析

刘伟伟,程博文,汪路元,于敏芳

(北京空间飞行器总体设计部,北京100094)

ARINC659总线因其在时间和空间上均提供了完备的故障冗余和操作健壮性,已经逐渐在对数据通信确定性及故障沉默和屏蔽要求较高的航天领域中展开应用;为了使ARINC659总线能够更好的适应航天器综合电子系统的高度冗余容及分布式控制的需求,对一种能够在不同设备中ARINC659总线之间相互桥接的技术进行了研究,进而实现分布式综合电子系统中所有硬件模块的统一时序规划和通信调度,可以显著提升系统中的资源共享、并行处理、故障冗余及分布式控制能力,同时也为关键系统中不同设备中的硬件模块间实现严格的时序关系操作提供了一种解决方案;最后就桥接对ARINC659总线同步机制的影响进行了分析,据此提出了桥接设计的约束和实现规则。

ARINC 659;总线桥接;总线同步;信号偏斜;航天器;综合电子

0 引言

星载综合电子系统是航天器数据和信息管理的重要组成部分,对航天器功能的实现和性能的提升具有举足轻重的低位,其设计方式和性能直接关系到整个航天器的安全性和可靠性、先进性以及成本消耗。为此星载综合电子系统的设计在不断向高集成度、轻小型化、低功耗方向发展的同时,也在致力于寻找一种方式既能够有效的提升系统的通信确定性以及故障冗余和隔离等可靠性保障能力,也能够充分利用软硬件资源实现系统分布式控制以及降低航天器设计成本的机制。而设备背板总线作为各硬件模块之间互联和通信的桥梁,其功能性能的优劣以及连接方式好坏在机制实现过程中起到了十分重要的作用。

ARINC659总线是一种线性多节点半双工通信的高可靠性标准背板总线[1],基于时间触发架构以及表驱动比例访问(TDPA)协议[2-3],在时间和空间上提供双重的故障冗余和操作健壮性,具有高度的容错性、可用性和完整性[4],能够满足在高数据吞吐量、严格故障隔离、数据传输确定的电子系统中的应用[5]。正是由于ARINC659总线这种特性,使得它越来越多的应用于航空航天领域的关键系统及单机中。然而当前ARINC659总线仅局限于但设备内部应用,无法实现具有严格时序关系的多设备间的统一访问,为此本文设计实现了一种能够将不同设备的ARINC659总线进行互联的桥接技术,实现综合电子系统中所有硬件模块的统一时序规划和通信调度,最终达到提升综合电子系统可靠性保证能力以及分布式控制和低成本设计的能力。

1 ARINC659总线架构

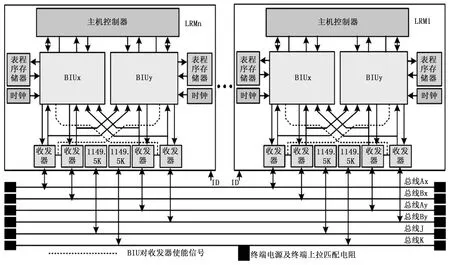

ARINC659总线是由双总线对组成的双——双配置,总线对A和B分别具有“X”和“Y"两条总线,同时每一个在线可更换模块(line replaceable module, LRM)有2个总线接口单元,分别为BIUx和BIUy,BIUx经由X总线发送数据,BIUy经由Y总线发送数据,而每一个BIU均接收所有4条总线上的数据。另外,每一条总线(AX、Ay、Bx和By)有各自的1条时钟线和2条数据线,每个时钟传送2个数据位,完整的总线组由12条线组成,具体如图1所示。

图1 ARINC659总线体系架构

ARINC659总线物理层采用BTL电平进行数据传输,在总线两端设置终端上拉电阻以及终端电源,在总线空闲期间,总线中的各信号线保持高电平状态,在总线传输数据期间,通过不断的触发BTL收发器导通来产生低电平信号。其中总线两端的终端上拉电阻除了维持总线空闲状态的电平以及在维持总线低电平所需的电流,更为重要的是与总线中各条传输线的特征阻抗匹配,以提升信号传输质量。

ARINC659总线通过帧描述语言(Frame Description Language)来实现链路层的表驱动比例访问(TDPA)协议,所有ARINC659总线接口单元按照相同的TDPA程序运行,TDPA程序中的命令由若干帧组成,每个帧又被划分为一系列窗口,窗口即为ARINC659总线进行数据传输和同步操作的最小通信单元。窗口可以分为数据窗口、空闲窗口、同步窗口3种,其中数据和空闲窗口的长度可以为32 bit到8 192 bit,同步窗口用于实现ARINC659总线上所有BIU之间的同步关系,根据同步类型的不同,由同步脉冲以及可选的同步消息组成,其中同步脉冲为一个大约5 bit的低电平脉冲。在实际运行过程中,TDPA程序中每一个窗口不仅定义了窗口的长度,发送者以及接收这,还定义了发送和接收数据的存储地址,从而使总线上不必再传输额外的长度和地址信息,既节约了消息地址域耗用的带宽,也消除了在传输过程中可能的地址错误[6-7]。

2 ARINC659总线桥接设计

2.1 ARINC659总线桥接应用需求

ARINC659总线作为设备背板总线,仅能够完成对设备内部硬件模块之间的连接和数据通信。在航天器综合电子系统中,为了实现分布式的控制和就近布局的需求,通常包含多台不同的电子设备,这些设备不得不单独配置处理器或控制器,也不得不单独配置ARINC659总线,一方面增加了系统的处理器资源开销,另一方面也无法实现不同设备间的同步调度操作,难以达到系统的优化资源配置和严格的时序操作序列。因此在设备之间实现ARINC659总线的桥接,将不同设备中的ARINC659总线通过“虚拟背板”总线进行连接,将整个综合电子系统的所有ARINC659总线看作一条ARINC659总线进行统一的时序规划和同步处理就显得非常有必要。

1)ARINC659总线桥接能够满足关键系统中存在严格时序关系的操作。在电子设备单独设置ARINC659总线时,各总线之间独立运行和调度,即使将所有的ARINC659总线上的通信节点配置相同的表程序,也很难保证不同设备中的ARINC659总线之间的同步关系,也就很难保证设备之间严格的时序序列操作,通过总线桥接,将所有的ARINC659总线统一规划和调度,系统中的所有硬件模块相当于运行于一条ARINC659总线上,借助ARINC659总线的时间确定性,可以很容易满足严格时序系列的操作要求。

2)ARINC659总线桥接能够增强综合电子系统的冗余容错能力。尽管在综合电子系统的电子设备中的硬件模块均设置了冗余备份措施,然而仍然不能排除设备中冗余处理器均故障的情况,通过ARINC659总线的桥接以及适当的总线时序规划,故障设备中的其余硬件模块即可非故障设备中的处理器模块接管,实现任务的无缝迁移和故障的沉默恢复,提升冗余容错能力以及系统硬件模块的资源利用率。

3)ARINC659总线桥接能够实现系统中软硬件资源的共享。通过ARINC659总线桥接,处理器不仅能够访问和控制本机中的硬件模块资源,也可以访问和控制其他设备中的硬件模块资源,实现处理器以及硬件模块的软硬件资源的共享和充分利用,并实现硬件模块的分布式控制,同时也可实现降低软硬件资源的配置数量,降低设计成本。

4)ARINC659总线桥接技术能够实现多并行计算与任务处理。通过ARINC659总线桥接,所有处理器资源运行于一条虚拟的背板总线上,通过全局的时序规划可以实现所有处理器在相同步调下实现同一任务的并行计算和处理,减缓对单一处理器的压力,增强系统性能。

2.2 ARINC659总线桥接设计方案

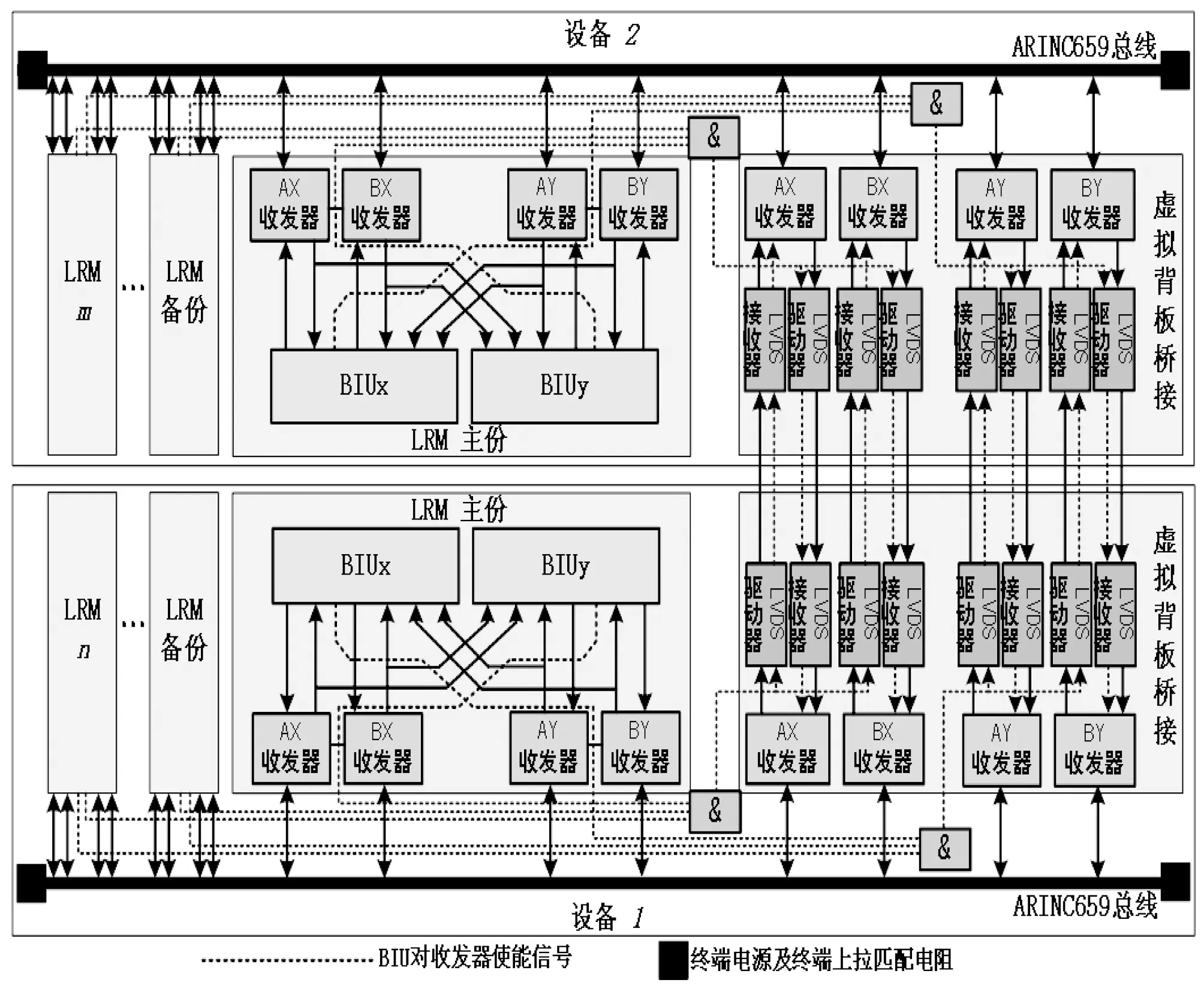

ARINC659总线的多点连接架构及其单线传输方式使得信号质量受信号反射的影响较大,而信号的反射与信号线阻抗的连续性密不可分,如果直接将所有设备的ARINC659总线简单的连接在一起,那么背板PCB与连接电缆之间的阻抗差异和长线传输的分布式电容及电感影响将会使得信号质量严重变差,甚至使ARINC659总线无法正常运行。因此本文对桥接的实现仍旧以保持各设备内部完整的ARINC659总线为基础,通过信号转换后的“虚拟背板”将各个分段的ARINC659总线桥接在一起。具体实现方式如图2所示。

图2 ARINC659总线桥接技术实现示意图

通过虚拟背板对ARINC659总线进行桥接时,首先通过ARINC659总线收发器将本机的总线信号转换为TTL电平,再通过LVDS驱动器转换为差分信号作为“虚拟背板”信号进行传输。在虚拟背板另一端,首先通过LVDS接收器将“虚拟背板”差分信号后转为TTL信号,再通过ARINC659总线收发器将信号驱动到这个设备的ARINC659总线上,进而实现两条独立ARINC659总线之间的互联互通。

在正常的ARINC659总线操作中,每个LRM中的BIUx与BIUy具有通过相互“捂嘴”(即BIU互相对对方的总线收发器使能信号进行控制)的功能实现故障沉默,也就是任意一个BIU的故障都不会将错误的数据送到ARINC659总线上而影响总线上其他模块间的通信,从而提升总线确定性和可靠性。为了在ARINC659总线桥接设计中保留 “捂嘴”功能,保证单一BIU的故障不影响总线操作,将同一设备中各硬件模块BIU对收发器的使能信号引出,并经过“与”操作后由LVDS驱动器送到对方设备中,将其转换为TTL信号后送到对应的总线收发器上,实现本机设备BIU对另一设备中桥接的总线收发器使能控制。

同一设备内部所有BIU的使能信号的“与”操作必须考虑LRM之间的冷/热冗余备份关系,为了保证冷备份LRM的使能信号不至于使“与”操作电路的输入产生不定态信号而影响电路功能以及不会对冷备份的LRM产生串电影响,“与”操作电路无法使用简单的集成芯片实现,为此设计中通过光电隔离器件或分离的晶体管组成开关电路实现所有使能信号的“线与”操作。另外,为了增强桥接电路的可靠性,在实际应用过程中可对“线与”电路中的器件进行串并联处理,也可对每台设备中对虚拟背板桥接模块设置双冗余冷备份处理,增强桥接电路在复杂空间环境中的可靠性。

图3 线与电路示意图

3 桥接对ARINC659总线同步机制影响分析

3.1 ARINC659总线同步机制

ARINC659总线上所有BIU运行相同的TDPA程序,为了保证BIU间执行TDPA程序的步调一致而不至于出现总线运行混乱的情况,必须有一种同步的机制使得所有BIU处于同步状态。为此ARINC659总线提供了3种不同形式的同步消息来实现位级以及帧级的同步,3种同步消息分别为初始同步消息、长同步消息、短同步消息:

1)初始同步消息由初始同步脉冲和长同步消息组合而成,用于在上电后或者整条总线范围出现失同步反常现象时初始化总线,使得所有的BIU能够重新从表程序的起始位置开始运行,重新建立所有BIU间的同步关系;

2)长同步消息由长同步脉冲和同步消息组成,同步消息的功能和种类有两种,一种为入口重同步消息用于将失去同步的BIU重新和总线上处于同步的BIU之间建立同步关系,并使失去同步的BIU从同步消息指定的表程序位置开始执行;另一种是帧变换消息用于控制所有的BIU从TDPA程序中当前正在执行的帧程序切换到另一个帧程序执行;

3)短同步消息实是一个大约持续5 bit长度的同步脉冲,用于纠正晶振的漂移来维持BIU间的位级同步以及邻近消息之间的消息间隔。

由于短同步消息为一个同步脉冲,因此无法对BIU执行TDPA程序产生影响,而仅能提供位级同步,而初始同步消息和长同步消息则可提供帧级同步,能够对BIU执行TDPA程序的位置产生影响,实际上,由于初始同步和长同步消息中包含同步脉冲,因此在提供帧级同步的同时,也可提供位级同步。通过ARINC659总线的位级同步即可保证所有处于同步状态的BIU按照统一的步调运行,并及时纠正BIU间的同步差异,从而实现保证同一个LRM中的BIUx和BIUy之间的信号偏斜小于2比特时间(tbit),以及保证总线上任意两个相邻消息之间的间隔不会为零,在TDPA程序中消息间间隔由GAP值定义,大小可在2比特到9比特之间进行选择。

同步消息在传输的过程中,不可避免的要受到元器件及传输线等引起的信号偏斜的影响,通过ARINC659总线的运行以及同步机制可以看出,如果信号偏斜对同步消息的影响较大,那么将导致BIU间执行TDPA程序的一致性受到影响,严重时将出现不同BIU发送的消息在总线上交叠的现象,最终导致数据以及同步消息的错误,使BIU无法正常处于同步状态,也就使整条ARINC659总线无法正常运行。因此,在实际工程设计中必须考虑信号偏斜的大小,并据此优化ARINC659总线的设计。

3.2 ARINC659总线中信号偏斜分析

信号偏斜的产生包含多种因素,包括元器件的传输延迟、传输线的传输延迟以及晶振漂移等原因。根据信号偏斜产生的机制不同以及对ARINC659总线影响的不同,将ARINC659总线中的信号偏斜分为空间信号偏斜、时间信号偏斜、XY信号偏斜:

1)空间信号偏斜(Sskew):由每个LRM或BIU处于背板的不同位置而引起的信号偏斜,与背板的长度、LRM的等效电容、LRM间的间隔、背板电气特性、信号传输速度等有关,由于在系统设计完毕后以上影响因素等参数也就固定下来,因此空间信号偏斜不随时间的变化而变化;

2)时间信号偏斜(Tskew):两个LRM处于背板的同一位置,由信号在两个LRM中经过不同元器件产生不同的传输延迟以及晶振漂移产生的信号偏斜,与背板到收发器间信号路径的不同、不同总线收发器产生偏斜的不同、收发器与BIU间信号线路径的不同、晶振漂移的不同,不同BIU输入缓冲器引起偏斜以及同步操作的精度等有关;由于时间信号偏斜受晶振漂移影响,因此会随时间的变化而逐渐变大;

3)XY信号偏斜(XYskew):同一个LRM中BIUx和BIUy间的时间偏斜,受收发器和BIU间信号线的不同引起的偏斜、两个BIU缓冲器引起的偏斜、晶振漂移及同步操作精度等影响;由于XY信号偏斜也受晶振的漂移的影响,因此会随时间变化而逐渐变大。

时间信号偏斜以及XY信号偏斜均受晶振漂移的影响,其大小会随着时间而不断增大,因此在一次同步操作刚刚结束时,时间信号偏斜和XY信号偏斜的值为最小,但是受到信号传输路径的不同,以及收发器和BIU等延迟不同,时间信号偏斜和XY信号偏斜的最小值都不可能为零,这个初始的最小值可由时间同步误差和XY同步误差进行描述:

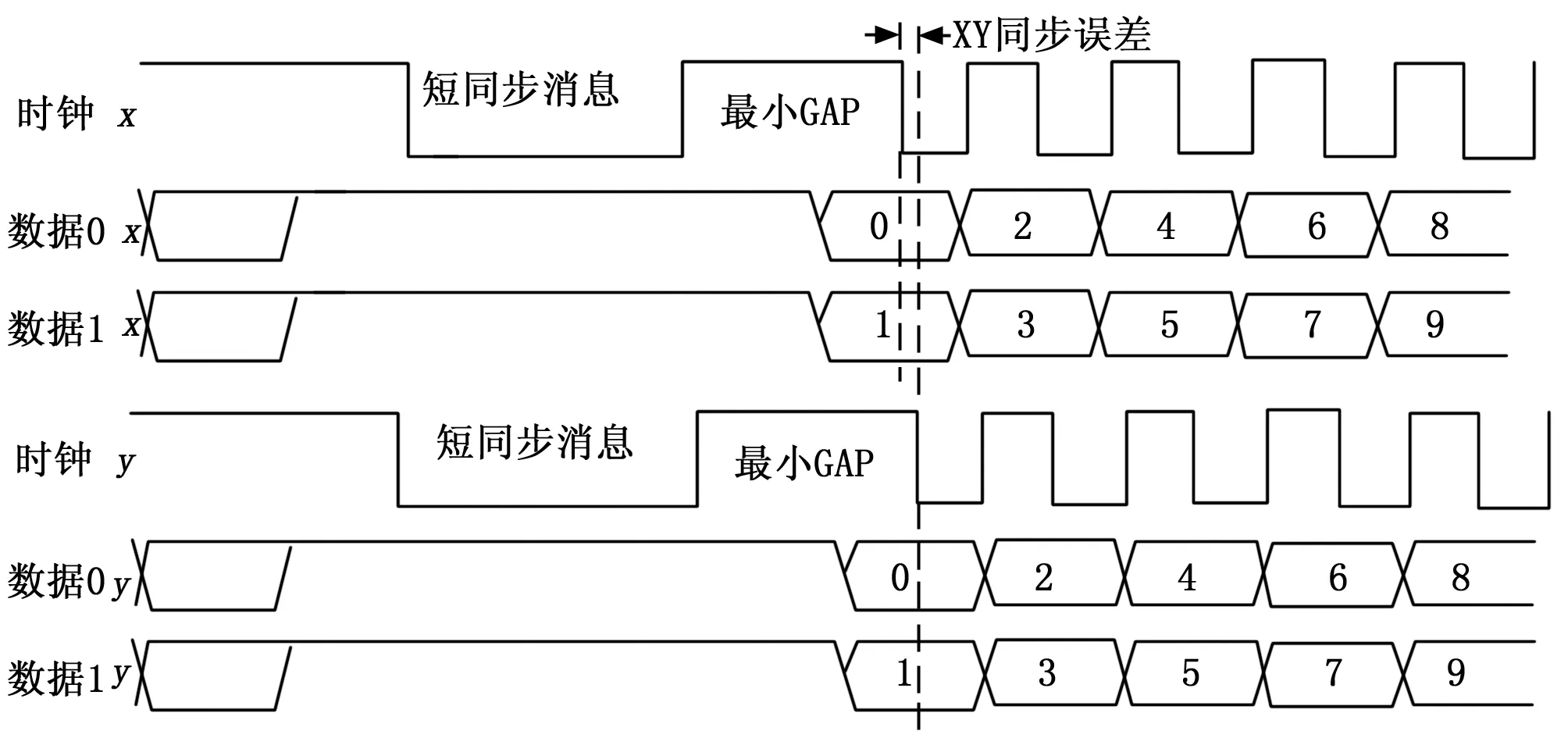

1)时间同步误差(Terror):同步操作刚结束时初始的时间信号偏斜,将两个LRM放置在总线的同一个位置,使它们在同步操作后以最小的GAP间隔立即轮流传输长度为1个字的消息,两个窗口间第一个时钟下降沿之间的时间与窗口实际长度的差值可以看做是时间同步误差;

2)XY同步误差(XYerror):同步操作刚结束时存在的初始XY信号偏斜,可在同步操作后以最小的GAP间隔立即开始消息传输,测量X总线(Ax和Bx总线)和Y总线(Ay和By总线)上消息数据对应的第一个时钟下降沿间的时间差来获得XY同步误差。

图4 时间同步误差测量示意图

图5 XY同步误差测量示意图

由于晶振的漂移,时间信号偏斜以及XY信号偏斜是在时间同步误差和XY同步误差的基础上随时间变化的一个函数,考虑不同BIU晶振的漂移在最坏的情况下为漂移方向相反,那么可以通过等式1和等式2计算时间信号偏斜和XY信号偏斜的大小,其中Cerror为晶振漂移率。

Tskew(t)=Terror+2×Cerror×t

(1)

XYskew(t)=XYerror+2×Cerror×t

(2)

在实际系统中,每个LRM之间实际是以一定的间隔位于ARNC659总线的不同位置,那么将空间信号偏斜考虑进去,可通过等式3获得ARINC659总线上总的信号偏斜Askew。

Askew(t)=Tskew(t)+Sskew

(3)

3.3 桥接对同步机制影响分析

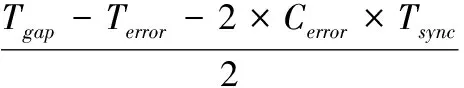

对于BIUx和BIUy之间的信号偏斜小于2比特时间需求,也就是XYskew小于2比特时间,根据等式2可以得到:

XYerror+2×Cerror×Tsync<2×tbit

(4)

在等式(4)中,将时间t以Tsync代替,Tsync为ARINC659总线的同步周期。根据等式(4)可以看出,XY信号偏斜的大小仅取决于同步周期和晶振漂移率,而与总线的长度以及空间信号偏斜无关。而ARINC659总线桥接所实现的正是将多个独立的ARINC659总线连接在一起,相当于将总线的长度拉长,但是并不会对时间相关的信号偏斜产生影响,也就是总线桥接不会对XY信号偏斜产生影响。

对于ARINC659总线上任意两个相邻消息间的间隔不能接近零的需求,存在一种最差的情况就是位于总线一端的LRM发送消息结束时,位于总线的另一端的LRM开始发送消息,但是在发送之前必须保证前面那个LRM发送的消息的最后一比特已经在整个总线上传输完成,而在总线上传输完成也就意味着经历了一次空间信号偏斜,因此得出Askew+Sskew (5) 在等式(5)中,同样将时间t以Tsync代替,同时可以看出,空间信号偏斜Sskew的大小与GAP值Tgap的选取以及同步周期Tsync的选取密切相关,而Tgap值的选择存在最大值限制,同步周期Tsync也要以不能影响正常的数据消息窗口传输前提,因此Tsync的选择存在最小值限制,也就是说空间信号偏斜Sskew存在最大值的限制。ARINC659总线桥接最为直接的影响就是增大了整条虚拟的ARINC659总线的长度,也就增大了空间信号偏斜Sskew,因此空间信号偏斜Sskew会对Tgap以及Tsync的选择产生影响,相反地,最大的Tgap以及最小的Tsync也就决定了ARINC659总线桥接实现的可行性,如果最大的Tgap以及最小的Tsync的仍不能满足等式5中对Sskew的要求,则说明ARINC659总线桥接时无法实现的。 通过在综合电子系统的两台设备之间建立ARINC659总线桥接实现对桥接技术的可实现性以及对同步的影响进行验证。桥接后总的ARINC659总线的最大长度小于5米,桥接电缆及PCB、元器件引入总的空间信号偏斜约为115 ns。 为了确保ARINC659总线桥接的最大可实现性,Tsync选择为最小可能周期,也就是在每个数据消息窗口后面都设置一个同步消息,其中最长的数据消息长度为1024字节,因此最小的Tsync为((1024×8)÷2)×tbit+2×Tgap。初始同步时间误差仅与信号路径不同有关且最大为1比特时间,所使用的晶振漂移率为50 ppm。根据等式5可以得出消息间间隔大小Tgap必须大于277 ns(也就是Tgap值须大于8.3 bit时间)。 在测试过程中分别设置不同的Tgap值进行ARINC659总线通信测试,当将Tgap值选择最大值9 bit以及8 bit时桥接后的ARINC659总线能够正常进行通信,由此验证了所设计的ARINC659总线桥接技术和设计方案是可行且是可实现的。另外,Tgap的值可为8 bit的主要原因是初始同步误差Terror以及晶振漂移率在实际应用过程中的测试比较困难,因此计算过程直接以最大值或标称值进行计算,因而引入的计算误差导致计算出的需求Tgap值偏大,然而对于工程应用而言,计算出的Tgap值偏大有利于实际应用时ARINC659总线具备一定的时序裕量,便于弥补通信电路以及元器件受环境及温度影响产生的参数漂移。 针对航天器综合电子系统设备间背板总线桥接的需求,本文提出的通过虚拟背板实现ARINC659总线桥接的方案具有较强的可行性和工程适用性,与此同时在对ARINC659总线运行和同步机制的基础上,对ARINC659总线中存在的各种信号偏斜进行了深入分析,并就总线桥接对信号偏斜的影响以及对总线设计中各参数选择的影响进行了分析,并给出计算参考公式,不仅可用于验证ARINC659总线桥接的可实现性,也可优化对GAP值以及同步周期的选取。为实现航天器综合电子系统的一体化设计以及并行计算和分布式控制提供了一种解决方案,在航天器研制中具有十分重要的推广意义。 [1] 张 锐,吴成富,段晓军. ARINC659总线在飞控余度管理技术中的应用[J]. 航空计算技术,2013, 43(2):128-133. [2] 李文星,樊晓桓,安建峰. ARINC659航空总线监控器的设计[J]. 计算机测量与控制,2012,20(1):91-94. [3] 臧 威,刘 芳,李 锐. 基于协议芯片和工具链的ARINC659总线开发平台[J]. 电子科技,2013,26 (9):85-91. [4] 张喜民. ARINC659背板数据总线协议初探[J]. 电光与控制,2013,20(3):93-97. [5] 李爱军,赵 刚,李伟成,等. 基于659总线的飞行器电气控制系统设计与实现[J]. 计算机测量与控制,2015,23(4):1218-1221. [6] 许宏杰,田摇泽,郭摇亮,等. ARINC659芯片设计与实现关键技术研究[J]. 计算机技术与发展,2014,24(3):26-30. [7] 刘海旭. ARINC 659通信总线的设计与实现[D].北京:北京交通大学,2010. DesignofARINC659BusBridgingandEffectAnalysisofBridgingtoBusSynchronization Liu Weiwei, Cheng Bowen, Wang Luyuan, Yu Minfang (Beijing Institute of Spacecraft System Engineering,Beijing 100094,China) With the characteristic of complete fault redundancy and operation robustness in both time and space, ARNC659 bus has been gradually adopted by aerospace which has high requirement of communication certainty as well as fault silence and insulation. In order to make the ARINC659 bus can better adapt to the demand of highly redundant and distributed control in spacecraft integrated avionics, this paper achieves a bridging technology that can connect the ARINC659 bus among different devices, so as to achieve unified timing planning and communication scheduling of all hardware modules of distributed integrated avionics. This improves significantly the ability of avionics in resource sharing and parallel computing and fault tolerance, and also provides an approach to operate between modules within different devices of pivotal system with strict temporal relationship. Finally, the effect of bus bridging to bus synchronization are analyzed, and puts forward design constraints and implementation principle during design of bus bridging. ARINC 659;bus bridging;bus synchronization;signal skew;spacecraft;integrated avionics 2017-04-09; 2017-05-18。 刘伟伟(1985-),男,山东东营人,硕士研究生,工程师,主要从事航天器综合电子、空间数据及信息系统等方向的研究。 1671-4598(2017)11-0129-04 10.16526/j.cnki.11-4762/tp.2017.11.033 TP3 A

4 实验结果与分析

5 结束语