基于RTD和HEMT的D触发器设计

2017-12-01冯杰姚茂群

冯杰, 姚茂群

(杭州师范大学 国际服务工程学院, 浙江 杭州 311121)

基于RTD和HEMT的D触发器设计

冯杰, 姚茂群

(杭州师范大学 国际服务工程学院, 浙江 杭州 311121)

共振隧穿二极管(RTD)作为一种新的量子器件和纳米电子器件,具有负内阻、电路功耗低、工作频率高、双稳态和自锁等特性,可突破CMOS工艺尺寸的物理极限,在数字集成电路领域有更为广阔的发展空间. 针对RTD的特性,采用3个RTD串联的单双稳态转换逻辑单元(MOBILE)和类SR锁存器,设计了基于RTD和HEMT(高电子迁移率晶体管)的D触发器. 较于其他研究的D触发器,该D触发器能有效降低电路的器件数量和复杂度,且能抗S、R信号的延时差异干扰,具有更稳健的输出.

共振隧穿二极管;高电子迁移率晶体管;单双稳态转换逻辑单元;D触发器

0 引 言

随着数字集成电路的快速发展,传统CMOS工艺尺寸不断减小,电路的集成度越来越高,同时也出现了一些由功耗和互连线等带来的问题,如热耗散、短沟道效应、量子力学效应等[1-3].共振隧穿二极管(resonant tunneling devices,RTD)作为一种新的量子器件和纳米电子器件,可以突破传统CMOS设计工艺所面临的物理限制,且比CMOS器件拥有更优秀的特性.RTD具有负内阻、电路功耗低、工作频率高、双稳态和自锁等特点[4-5].

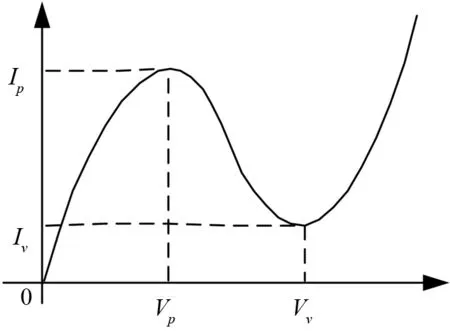

(1) 负内阻(negative differential resistance,NDR).RTD器件在随着电压从低电平到高电平变化的过程中,其电流从零开始增大;到达第1个波峰后,电流开始减小;到达第1个波谷后,电流继续增大.电流从波峰到波谷的这一段曲线表现为RTD的负内组特性,如图1所示.Vp为波峰电压,Ip为波峰电流,Vv为波谷电压,Iv为波谷电流.

图1 负内阻Fig.1 NDR

(2) 电路功耗低.RTD器件的负内阻特性,使得由其设计的电路在结构上更加简单,且RTD器件电路的工作电压低,一般在0.8 V左右,稳定时的工作电流也相对较低,一般为μA数量级.

(3) 工作频率高.由于RTD器件具有共振隧穿效应,这是一种高速变化的物理过程,所以一般RTD的工作频率都很高,且工作速度快.

(4) 双稳态和自锁.RTD器件的负内阻特性,使得由其组成的单双稳态转换逻辑单元(Mo nostable bistable transition logic element, MOBILE)具有双稳态和自锁特性,这相当于自身带了一个锁存器,非常有利于时序电路设计中器件数目的减少.

本文将RTD组成的MOBILE及三端器件作为输入分支,以设计D触发器.

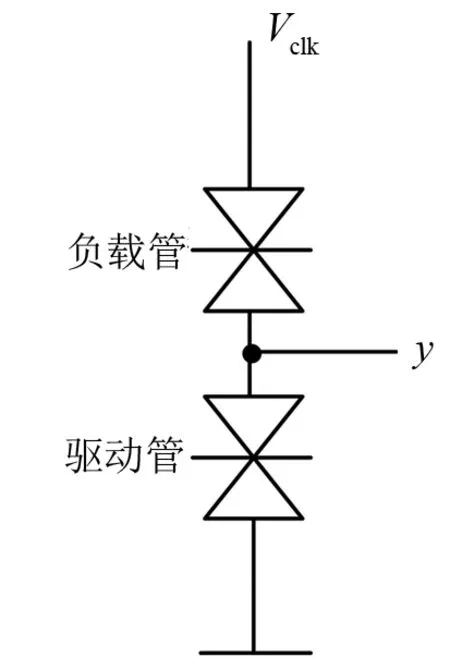

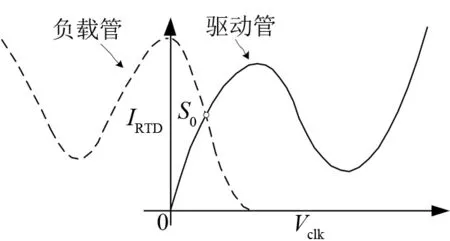

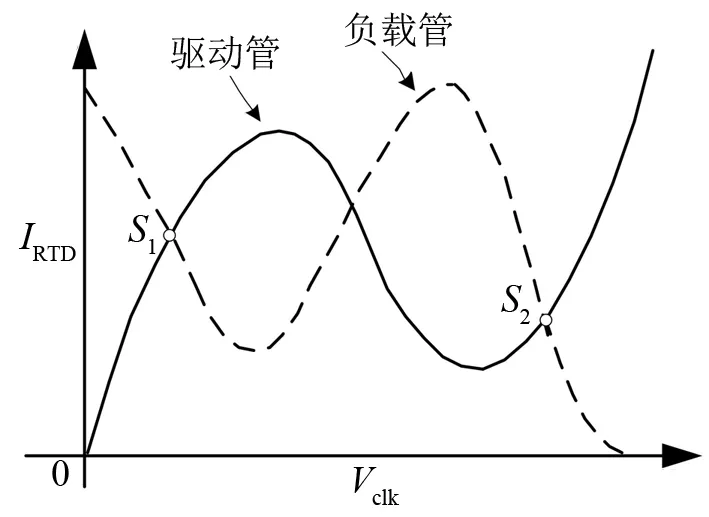

1 单双稳态转换逻辑单元

MOBILE是基于RTD电路设计的一个重要逻辑单元,可由2个或更多个RTD串联而成.由2个或是更多个RTD串联的MOBILE,均具有类似的工作原理.以2个RTD串联的MOBILE为例,电路如图2(a)所示[6-9].在图2(a)中,上面的RTD为负载管,下面的RTD 为驱动管,时钟信号Vclk为偏置电压.当Vclk较低时,负载管和驱动管工作在第1个正阻区,此时电流电压特性曲线如图2(b)所示,电路稳定于S0点,处于单稳态;y输出为低电平.当Vclk继续增大,超过2倍的RTD波峰电压时,电路将出现2个稳定状态S1、S2,如图2(c)所示;具体处于哪个稳定状态由负载管和驱动管中波峰电流较小的决定.当负载管的波峰电流较小时,负载管先进入负阻区,呈现较大的阻抗,电路处于S1稳定状态,y输出低电平;反之,当驱动管的波峰电流较小时,电路处于S2稳定状态,y输出高电平;即MOBILE具有双稳态特性.由于当RTD的电流密度一定时,其波峰电流和波谷电流与面积成正比,可通过改变RTD的面积来获得需要的输出.当Vclk保持高电平时,y输出将保持不变;即MOBILE具有自锁特性.

(a) MOBILE

(b) 单稳态

(c) 双稳态图2 MOBILE特性分析Fig.2 Characteristic analysis of MOBILE

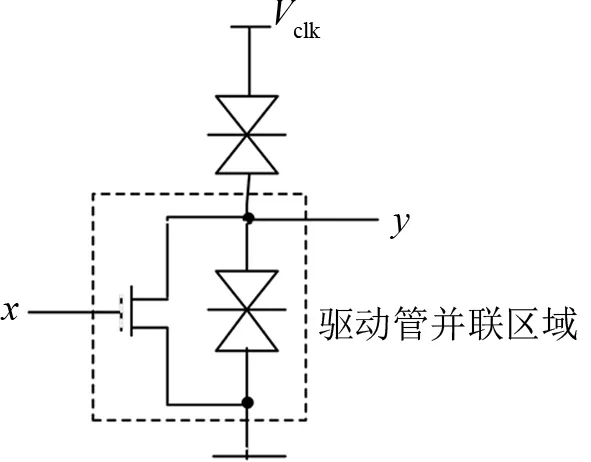

由于RTD是一个二端器件,为了能有效控制MOBILE的输出,通常需要加入高速的三端器件作为输入分支[10-12].在时序电路设计中,常用高电子迁移率晶体管(high electron mobility transistor, HEMT)[13].通过HEMT与负载管或驱动管直接并联,以控制相应管子并联区域的波峰电流大小.图3所示的是一个反相器,其中x为HEMT的栅极输入端.在图3中,HEMT控制驱动管并联区域的波峰电流大小;且当x输入低电平时,驱动管并联区域的波峰电流比负载管小,电路y输出高电平;当x输入高电平时,驱动管并联区域的波峰电流比负载管大,电路y输出低电平.

图3 反相器Fig.3 Inverter

2 D触发器设计

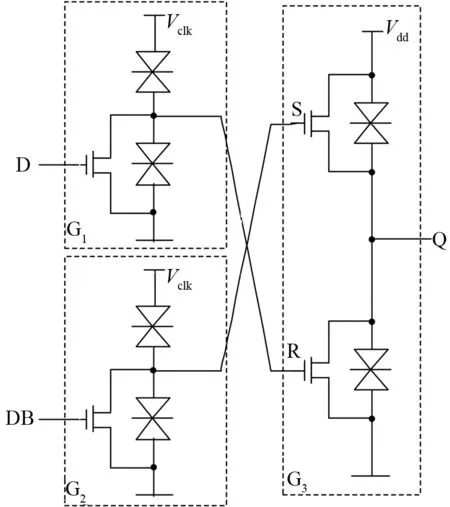

MOBILE的双稳态和自锁特性,在设计时序电路时,能使电路结构变得简单.当偏置电压Vclk上升时,电路输出有效电平,且Vclk保持高电平时,电路输出保持不变.但是当Vclk为低电平时,电路输出也变为低电平.为了使Vclk在低电平时,电路输出保持不变,就需要通过另外的锁存器电路进行弥补.图4(a)为文献[14]中提出的一种D触发器.

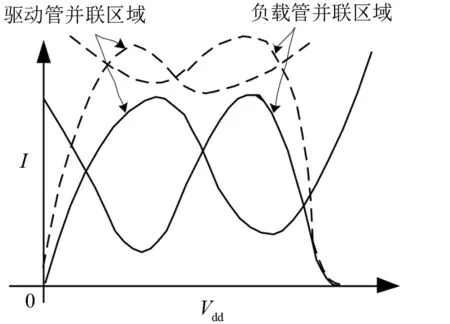

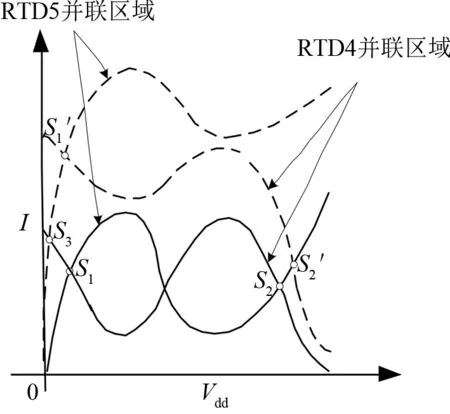

该D触发器电路由电路G1、G2、G3三部分组成,输入端D、DB(D的反相信号),输出端Q,时钟信号Vclk,高电平信号Vdd.电路G1、G2都是反相器,电路G3是SR锁存器,SR锁存器原理如图4(b)所示.图中实线表示S、R输入低电平时,负载管并联区域和驱动管并联区域的电流电压特性曲线;虚线表示S、R输入高电平时,负载管并联区域和驱动管并联区域的电流电压特性曲线.由于电路G1、G2只能组合输出3种状态10、01、00,故整个电路实现了D触发器功能.

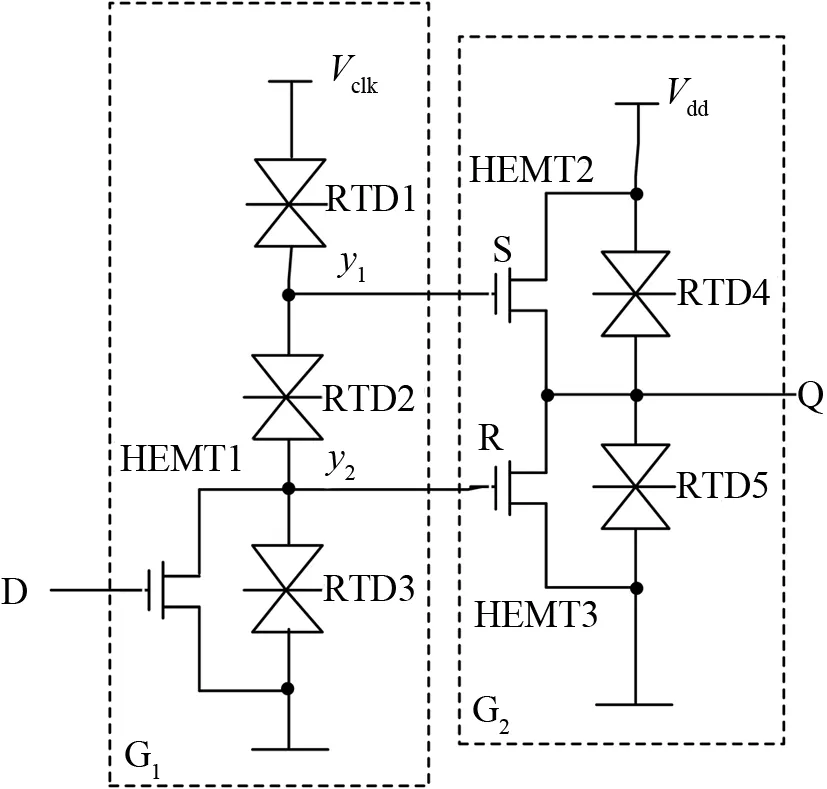

上述D触发器中有2个缺陷: (1) S、R信号是通过2个反相器得到的,且DB信号需要通过额外的电路提供,这些都会增加D触发器电路的复杂度;(2) D和DB信号的不匹配或2个反相器输出延时差异都会导致输出错误的S、R信号.本文提出的D触发器如图5所示,能有效解决上述2个缺陷,且具有良好的功耗、D-Q的上升延时和下降延时.

(a) 文献[14]提出的一种D触发器

(b) SR锁存器特性曲线图4 文献[14]中的D触发器分析Fig.4 D flip-flop analysis in [14]

图5 本文提出的D触发器Fig.5 The D flip-flop proposed in this paper

图5中,整个电路只由G1、G2两部分电路组成.电路G1由3个RTD串联而成的MOBILE及1个HEMT组成.当时钟电压Vclk从低电平变化到高电平,且D输入低电平时,RTD1、RTD2和RTD3并联区域的波峰电流满足:IPRTD1>IPRTD2>IPRTD3-Parallel.此时,RTD3并联区域从第1正阻区进入负阻区,呈现高阻状态,RTD1和RTD2仍然工作在第1正阻区,呈现低阻状态,y1、y2输出高电平.当时钟电压Vclk从低电平变化到高电平,D输入高电平时,由于HEMT1控制RTD3并联区域的波峰电流,此时RTD1、RTD2、RTD3的波峰电流满足:IPRTD1>IPRTD3-Parallel>IPRTD2,RTD2从第1正阻区进入到负阻区,呈现高阻状态,RTD1和RTD3仍然工作在第1正阻区,呈现低阻状态,y1输出高电平、y2输出低电平,如表1所示.

表1 G1的真值表

Table 1 Truth table of G1

电路G2是一个类SR锁存器,HEMT2控制RTD4并联区域的波峰电流,HEMT3控制RTD5并联区域的波峰电流,工作原理如图6所示.

图6 类SR锁存器的特性曲线Fig.6 Characteristic curve of similar SR latch

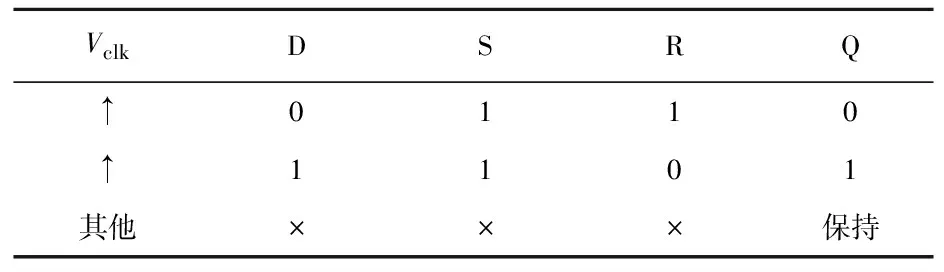

表2 G2的真值表

Table 2 Truth table of G2

表3 D触发器的真值表

Table 3 Truth table of D flip-flop

3 HSPICE仿真及分析

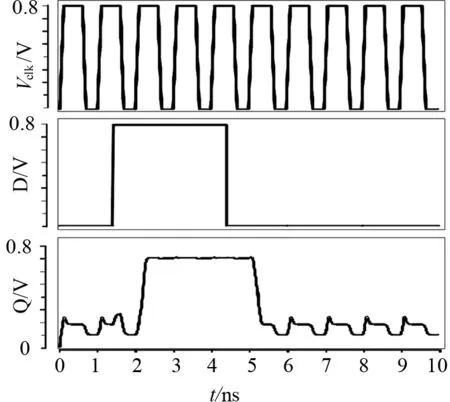

对所设计的D触发器进行HSPICE仿真,RTD采用文献[15]中介绍的模型,其中RTD波峰电压为0.28 V,RTD波峰电流密度为9 kA·cm-2,每μm2的电容为4 fF,HEMT采用增强型和耗尽型晶体管,阈值电压分别为0.4 V和-0.1 V.仿真结果如图7所示.

图7 D触发器的仿真波形Fig.7 Simulation waveform of D flip-flop

其中,工作电压Vdd和时钟电压Vclk幅值均为0.8 V,Vclk频率为1 GHz,输入D,输出Q.从仿真波形中可以看出,所设计的D触发器逻辑功能正确,且为时钟上升沿触发.

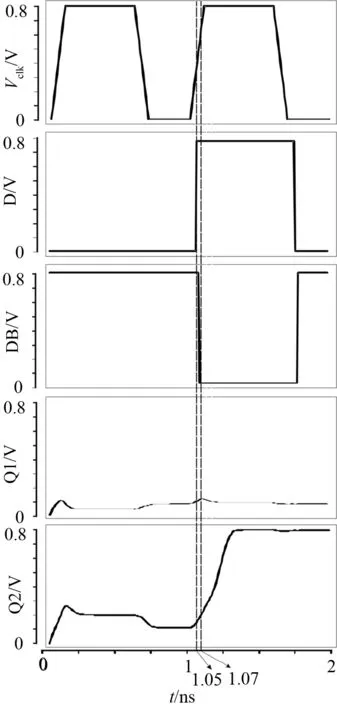

图8 2种D触发器的仿真波形Fig.8 Simulation waveform of two D flip-flops

由于文献[14]中的D和DB信号,在实际电路中经过各自相连的反相器到达S、R端,可能存在输出延时差异.为了更好地比较所设计的D触发器和文献[14]中D触发器的输出稳健性,假设DB相对于D延迟0.02 ns输入,图8为两者的仿真波形.其中,Q1为文献[14]中的D触发器输出,Q2为本文D触发器输出.从图8中可以看出,D在1.05 ns发生电平翻转,而DB在1.07 ns发生电平翻转,导致当时钟Vclk在1 ns跳变到高电平时,Q1未能跟随D信号电平输出高电平.而本文设计的D触发器则不会出现这种错误,当时钟Vclk在1 ns跳变时,Q2能跟随D信号电平输出正确的高电平.

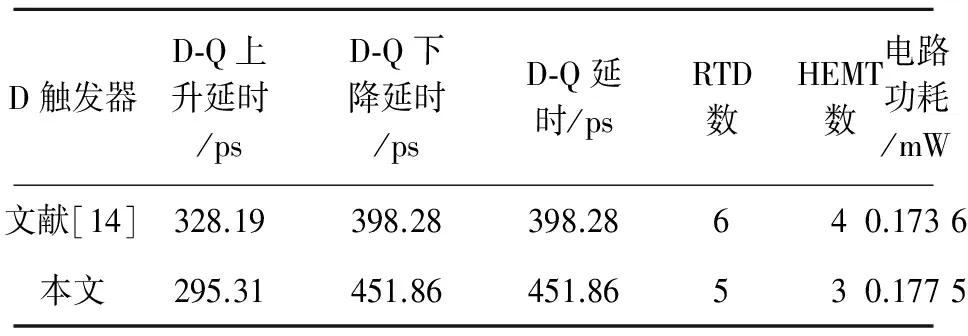

表4为上述2种类型D触发器的性能比较.触发器延时值均在Q输出端接100 fF电容下测得,并取D-Q上升延时和下降延时的最大值;电路功耗均在输入数据率α=20%时测得.由表4可知,所设计的D触发器与文献[14]的D触发器两者在D-Q延时和电路功耗上相差不大,但本文设计的D触发器在RTD和HEMT器件数量上各减少了1个.

表4 2种D触发器的性能比较

Table 4 Performance comparison of two D flip-flops

通过上述2种D触发器的仿真及分析可以看出,所设计的D触发器与文献[14]的D触发器在电路功耗和触发器D-Q延时上相差不大,但本文的D触发器设计所用的RTD和HEMT数都少了1个,且不用额外的电路提供DB信号,能更好地降低电路的额外开销;也不会因为S、R信号的延时差异出现错误输出,其输出更稳健.

4 总 结

RTD器件作为一种新型量子器件和纳米电子器件,具有的各项优秀特性使其在时序电路设计上具有比CMOS电路更加明显的优势.当RTD器件组成MOBILE时,其各项特性均能得到很好的表现.因此,时序电路的设计亦围绕MOBILE展开.文中所设计的D触发器采用3个串联RTD的MOBILE来提供S、R信号,并设计了类SR锁存器,使得在时钟电压为低电平时输出电压保持不变.相较于以往的设计,该D触发器具有更稳健的输出,且电路结构和设计方法更简单.

[1] IWAI H. Future of nano CMOS technology[J].Solid-StateElectrorics, 2015, 112: 56-67.

[2] GHALLAB Y H, ISMAIL Y.CMOS based lab-on-a-chip: Applications, challenges and future trends[J].IEEECircuits&SystemsMagazine, 2014, 14(2): 27-47.

[3] NARENDRA S G.Challenges and design choices in nanoscale CMOS[J].ACMJournalonEmergingTechnologiesinComputingSystems, 2005, 1(1): 7-49.

[4] MAZUMDER P, KULKARNI S, BHATTACHARYA M.Digital circuit applications of resonant tunneling devices[J].ProceedingsoftheIEEE, 1998, 86(4): 664-686.

[5] ZHENG Y, HUANG C.Complete logic functionality of reconfigurable RTD circuit elements[J].IEEETransactionsonNanotechnology, 2009, 8(5): 631-642.

[6] AVEDILLO M J, QUINTANA J M, PETTENGHI H, et al.Logic models supporting the design of MOBILE-based RTD circuits[C]//Proceedingsofthe16thInternationalConferenceonApplication-SpecificSystems.Samos: IEEE, 2005: 254-259.

[7] GAN K J, TSAI C S, HSIEN C W, et al.Design of monostable-bistable transition logic element using the BiCMOS-based negative differential resistance circuit[J].AnalogIntegratedCircuits&SignalProcessing,2011, 68(3): 379-385.

[8] POPP M, THIESSEN T, ZORN C, et al.On the functionality of RTD MOBILE circuits-A geometric approach[C]//IEEEInternationalSymposiumonCircuits&Systems. Melbourne: IEEE ISCAS, 2014: 1251-1254.

[9] CHEN K J, MAEZAWA K, YAMAMOTO M.InP-based high performance monostable-bistable transition logic elements (MOBILEs) using integrated multiple-input resonant-tunneling devices[J].IEEEElectronDeviceLetters, 1996, 17(3): 127-129.

[10] DIXIT N K, KUMARI V.A XOR threshold logic implementation through resonant tunneling diode[J].InternationalJournalofVlsiDesign&CommunicationSystems, 2012, 3(5): 137-146.

[11] YAO M Q, YANG K, XU C Y, et al.Design of a novel RTD-based three-variable universal logic gate[J].FrontiersofInformationTechnology&ElectronicEngineering, 2015, 16(8): 694-699.

[12] ZHENG Y, HUANG C.Reconfigurable RTD-based circuit elements of complete logic functionality[C]//Asia&SouthPacificDesignAutomationConference. Virginia Tech: IEEE Computer Society Press, 2008: 71-76.

[13] CHO J, LI Z, BOZORG G E, et al.Improved thermal interfaces of GaN-diamond composite substrates for HEMT applications[J].IEEETransactionsonComponentsPackaging&ManufacturingTechnology, 2013, 3(1): 79-85.

[14] ZHANG H, MAZUMDER P, YANG K.Resonant tunneling diode based QMOS edge triggered flip-flop design[C]//InternationalSymposiumonCircuitsandSystems.Vancouver: IEEE,2004, 3(3): 705-708.

[15] SCHULMAN J N, SANTOS H J D L,CHOW D H. Physics-based RTD current-voltage equation[J].IEEEElectronDeviceLetters, 1996, 17(5): 220-222.

FENG Jie, YAO Maoqun

(HangzhouInstituteofServiceEngineering,HangzhouNormalUniversity,Hangzhou311121,China)

DesignofDflip-flopbasedonRTDandHEMT.Journal of Zhejiang University (Science Edition),2017, 44(6): 718-723

The resonant tunneling diode (RTD) as a new quantum device and nano-electronic device, has many attributes, including negative resistance, low power consumption, high frequency, bistability and self-latching. It can be used to break through the physical limits of CMOS process size, and also has a broader space for the development of digital integrated circuit. According to the characteristics of the RTD, a D flip-flop is designed based on RTD and HEMT(high electron mobility transistor). The D flip-flop uses the monostable-bistable transition logic element (MOBILE) with three RTDs in series and the similar SR-latch. Compared with the D flip-flop in other studies, the designed D flip-flop can effectively reduce the device number and complexity of the circuit.What is more, it also can eliminate the interference of delay difference between the signals of S and R with a more robust output.

RTD; HEMT; MOBILE; D flip-flop

2016-04-13.

浙江省自然科学基金资助项目(LY15F010011);国家自然科学基金资助项目(61771179,61471314,61271124).

冯杰(1991—),ORCID: http://orcid.org/0000-0001-7726-1944,男,硕士生,主要从事数字集成电路研究.

*通信作者,ORCID: http://orcid.org/0000-0001-6484-4972,E-mail:yaomaoqun@163.com.

10.3785/j.issn.1008-9497.2017.06.011

TN 432

A

1008-9497(2017)06-718-06