探析高速数字电路中信号反射的分析与对策

2017-11-30孟海涛

孟海涛

(太原理工大学,太原 030024)

探析高速数字电路中信号反射的分析与对策

孟海涛

(太原理工大学,太原 030024)

当前我国微电子技术发展迅猛,人们对数字系统的工作频率要求不断提高,然而在数字系统工作频率不断提升的情况下,信号的完整性成为了一个关键性问题。对此,本文分析了信号反射噪声的形成,以及相应的解决方法。

高速数字电路;信号反射;反射噪音;对策分析

1 引言

通常来说,高速数字电路指的就是当工作频率到达一定数值,且占有数字系统一定份额的电路。在实际中,仅仅通过频率去判断某一电路是否是高速数字电路是不科学的。除了频率外,还应该将信号传输的延迟时间和信号上升的时间纳入判断标准。通常来说,当频率符合高速数字电路要求,且信号传输延迟时间大于信号上升时间的20%即为高速数字电路。从目前来看,我国在电子系统设计中已经全面进入高速、高频设计领域,并且随着我国IC技术工艺的发展,在高速数字系统中我国驱动器的上升沿和下降沿已经开始步入ps量级。在这种前提下,电路信号反射噪声问题便成为了一个关键性问题。

2 信号的完整性

简单来说,信号的完整性实质上指的就是信号在电路中传输的质量,信号的传输路径可以是金属线、光学器件、或者其他媒介物质等。当信号完整性良好时,信号在需要的时候具备其需要达到的电压电平均值。但在实际中,信号往往会受到各种因素影响,从而造成信号完整性变差。其中最为常见的信号完整性问题便是信号反射噪音问题。

3 高速数字电路信号反射噪音的形成

在高速数字电路中,信号的传输是在PCB上沿着传输线进行传输。当信号在传输中受阻,导致信号传输不连续时,部分能量会沿着传输线从受阻点或不连续点沿着传输线返回,也就是信号反射。信号反射的大小与信号在传输中所受阻抗失配程度有关,通常来说,失陪阻抗的大小与信号反射的大小是呈正相关关系,阻抗失配越大,信号反射越大;阻抗失配越小,信号反射越小。[1]当信号在传输中受阻产生信号反射时,往往都会导致上冲、下冲、以及振铃现象,从而造成信号反射噪音。

4 端接技术

在高速数字系统中,传输线与阻抗不匹配极易造成反射噪音的出现,而要解决之一问题,最有效的方法就是根据传输线的阻抗特性,对传输线的发送端或接收端进行阻抗匹配,通过阻抗匹配,从而使传输线反射系数归零。通常来说,传输线的阻抗匹配主要具有两种短接方式,一是并行端接方式、二是串行短接方式。

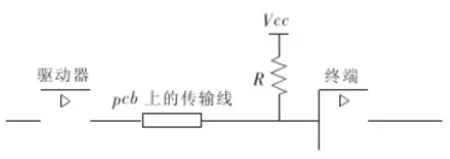

4.1 并行端接

并行端接是解决传输线阻抗不匹配最简单的处理方法,该端接方法主要是通过电阻R将传输线的末端接地或接至Vcc。这种端接方式,可以使返回通路吸收的电流超过电源提供的电流。[2]而将传输线接地主要是为了将终端匹配到地,从而利用地上的吸收能力,降低电路信号反射噪音。而将传输线终端匹配到Vcc主要是为了增强驱动器的功能,从而利用驱动器来消除或减少反射噪音。如图1所示。

图1 并行端接匹配示意图

4.2 串行端接

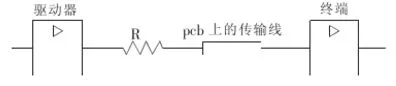

串行端接同样是一种解决传输线阻抗不匹配问题的常用方法,该法主要是将一个电阻R连接在驱动器输出端和信号线之间,相当于为驱动器增加了一个电阻元件。相对于并行电阻匹配技术来说,这种电阻匹配技术消耗的功率是最小的,一方面采用串行端接不会导致信号线与地线之间出现额外电阻,另一方面端接匹配技术也不会为驱动器造成额外直流负载。因此,从效果上看,串行端接较并行端接是具有一定的优势的。如图2所示。

图2 串联端接匹配示意图

5 拓扑结构

5.1 总线结构

总线结构是一种最为常见的信号连接方式,它是一种将驱动器和负载按照一定的顺序连接在信号线上。在总线结构中,信号线的分支要求尽可能短。在总线结构中,离驱动器越近的信号,受到的干扰越严重中,因此离驱动器越近的信号反射干扰也就越严重。而离驱动器较远的信号,由于受到的干扰较小,因此信号反射干扰也较小。究其原因来说,近端信号受干扰程度较高主要是由于近端信号是多点反射,因此,近端信号受到的反射干扰是多点反射综合的结果。

5.2 星形结构

星形结构是将负载分布在驱动器周围,并将负载和驱动源直接连接的一种连接方式。采用该种连接方式,可以降低传输线原阻抗,其作用和串行端接类似。

总的来说,不同的拓扑结构对信号波形具有较大的影响,合理的拓扑结构往往能够使信号的波形保持在一个较好的状态。信号的波形与连线的总长度有关,连线越长,离驱动源越近的信号波形就越差。在这种情况下,应尽量将采用缓冲器件将电路系统中的高速电路和低速电路分开。另外,信号反射与驱动器的驱动能力有关,通常来说低输出电阻,高输出电流的驱动器造成的信号反射较为严重。因此,想要解决信号反射问题还需要合理的选择驱动器。

6 结束语

综上所述,信号反射噪音在高速数字电路中是一个较为常见的现象,想要解决之一问题需要对造成信号反射的原因进行分析,其主要原因在于造成高速数字电路信号反射的原因多种多样,只有找到造成信号反射噪音的源头,才能够有效地解决之一问题。通常来说,造成高速数字电路信号反射的原因与传输线的阻抗特性以及采用的拓扑结构有关,想要解决电路信号反射问题,需从以上两个方面进行解决。

CA Technologies首席执行官在CA World’17发表主题演讲

2017年11月16日,CA Technologies首席执行官Mike Gregoire宣布CA World ’17开幕并发表主题演讲。他强调创造力对于发掘转型机遇的重要性,并鼓励企业和IT界高管将创新力和执行力结合在一起,并寻求类似CA这样的合作伙伴,通过先进的软件解决方案加速实现商业价值,帮助企业激发创造力。

CA Technologies在CA World’17上展示了超过20余种产品创新和提升,这些解决方案为广大公司提供了适应和响应变革、以及推动现有科技投资以实现未来成功的能力。从内部部署到云计算,以及两者之间的所有服务,CA可以提供业界领先的产品、解决方案和专业技能,帮助企业移除阻碍,在竞争中一马当先、出奇制胜。

[1] 李双力.基于高速数字电路中的信号完整性分析[J].信息通信,2016(8):231-232

[2] 吴华娟.基于高速数字电路设计中信号完整性分析与研究[J].工程技术:文摘版,2016(8):00179-00180密技术

10.3969/J.ISSN.1672-7274.2017.11.007

TN79,TP331.2

1672-7274(2017)11-0025-02