基于FPGA的快速图像采集系统的设计

2017-11-15许乐灵

许乐灵

(池州职业技术学院 图文信息中心,安徽 池州 247000)

基于FPGA的快速图像采集系统的设计

许乐灵

(池州职业技术学院 图文信息中心,安徽 池州 247000)

面对图像采集系统要能够达到高帧率、快速实时显示图像的要求,常见的设计方案多为 FPGA+DSP+PC 机,但该方案成本过高,实现复杂。随着 FPGA 的不断发展,文中设计了一种将图像的采集、处理、显示集成于一片FPGA 芯片的系统。该系统可用于运动物体的图像采集,能够实现高帧率实时图像的显示,且简化了系统结构、降低了成本。同时,该系统设计灵活,适当地修改后即可适用于多种领域。

图像采集;高帧率;FPGA

由于半导体技术的发展,现场可编程门列阵FPGA(Field-Programmable Gate Array)技术也得到了飞速发展。随着FPGA内部越来越强大的处理能力以及并行处理机制,伴随着计算机在处理图像方面智能化技术的飞速发展趋势,FPGA 的应用已经不仅仅局限于通信领域,数字信号处理、图像处理等领域越来越多使用 FPGA 开发。[1]

图像传感器CCD (Charge Coupled Devices),是一种集成了光电转换、电荷储存及转移的半导体器件,具有集成度高、性能稳定、响应速度快、分辨率高、抗干扰能力强等优点。

目前图像采集处理系统的主流设计方案是DSP+FPGA,数字信号处理器DSP(Digital Signal Processing)具有强大的数据处理能力和高运算速度等特点,文献[2-4]等都是基于此方案的系统设计,问题是这个方案,实现比较复杂,成本过高,主要是DSP由于是整个系统中最核心最关键的电子器件,其性能对整个系统的性能起决定性作用,要对大量数据进行处理,就必须进行大量复杂而高精度的快速计算,由此对DSP芯片的性能要求很高,性能高意味着成本高。[2]针对此问题,本文在兼顾分辨率和满足行频需求的情况下,选择东芝公司的TCD2566 线阵 CCD 传感器,利用 FPGA 并行处理机制的方案,[5]设计了集成图像采集、处理与显示于一体的系统。

1 系统方案设计

整个系统主要由三个部分组成:图像采集子系统、数据处理子系统、图像显示子系统。

选择了ALTERA公司的飓风系列FPGA芯片作为系统的核心控制器,该系列芯片足够整个系统的图像采集与显示的逻辑设计,同时低廉的价格很好地控制了成本。

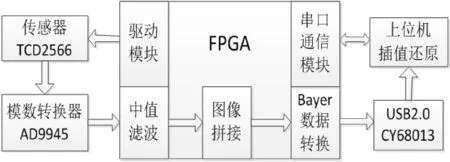

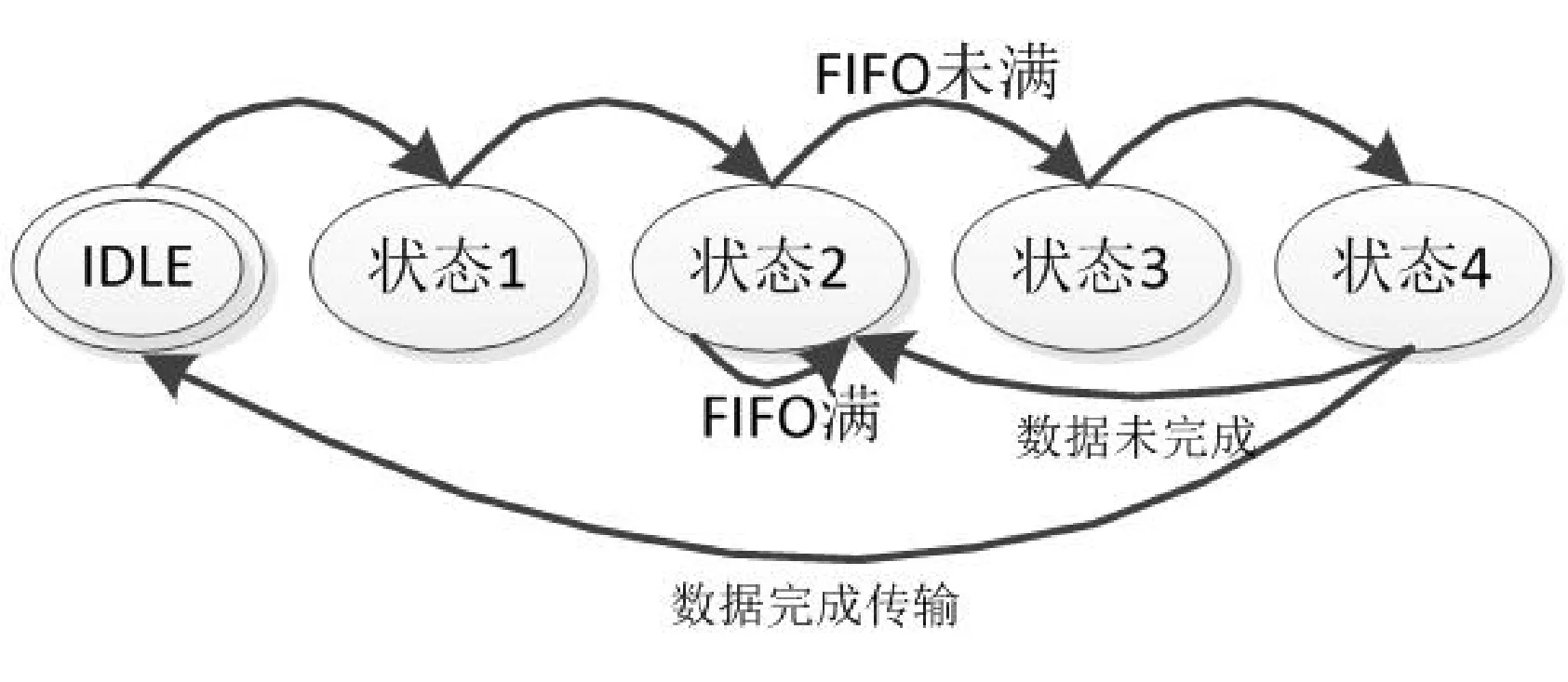

图像采集子系统包含了传感器、模数转换器驱动模块;传感器缓冲放大模块;RS485串口通信模块等。数据处理子系统包括了图像数据预处理模块、Bayer数据转换模块。图像显示子系统包括了SDRAM数据存储模块、USB2.0 数据传输模块以及上位机显示模块。图像采集系统框图如图 1 所示。

2 图像采集子系统设计

2.1传感器逻辑设计

TCD2566 线阵 CCD 工作频率最高 35MHz,横向分辨率最大为 5340 个像素点,最大行频可达 6250fps。[6]

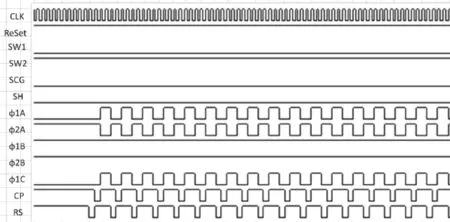

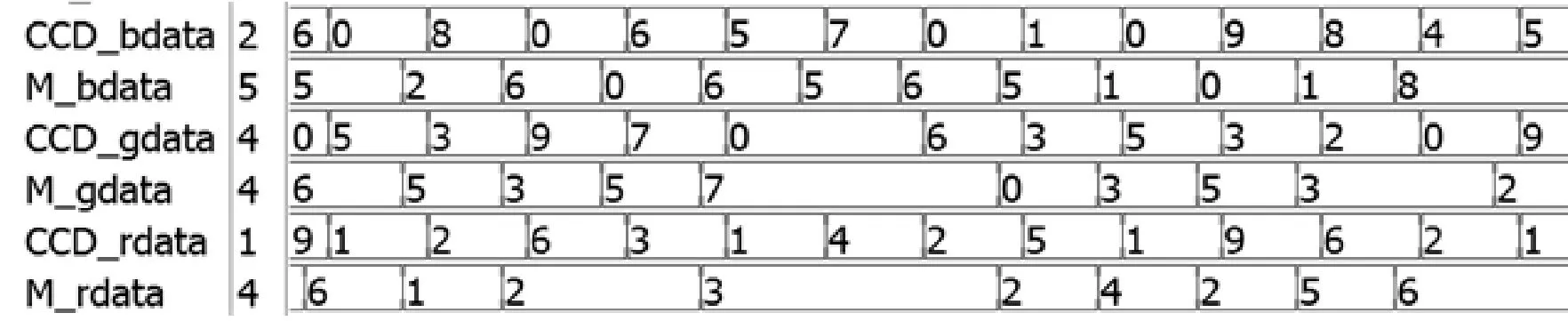

在 FPGA 产生传感器驱动信号时,通过内部锁相环 PLL 设定一个全局时钟,再对全局时钟进行分频来得到传感器所需要的驱动信号。这样不容易出现时序混乱,同时对于传感器工作频率的修改更加简便,只需要修改全局时钟即可。以传感器正常工作 30MHz为例,FPGA 外部接入晶振 50MHz,通过 FPGA内部 PLL 倍频得到全局时钟 120MHz,通过分频计数来得到所有的驱动信号。传感器正常工作时,所需的信号包括:SW1,SW2 模式选择信号,SCG存储脉冲电压清除信号,SH转移脉冲信号,ф1A,ф1B,ф2B,ф1C 时钟脉冲信号,RS复位脉冲信号,CP 钳位脉冲信号。传感器驱动时序仿真图如图 2 所示。

图1图像采集系统整体框图设计

图2传感器驱动时序仿真图

2.2模数转换逻辑设计

为了后续对图像数据进行处理,我们必须将传感器采集到的模拟信号转化为数字信号。本文选择了AD9945 高速处理芯片。[7]

AD9945 是一款具有相关双采样、直流偏置、增益可调等功能的模拟信号处理芯片,其工作频率可达 40MHz。[8]

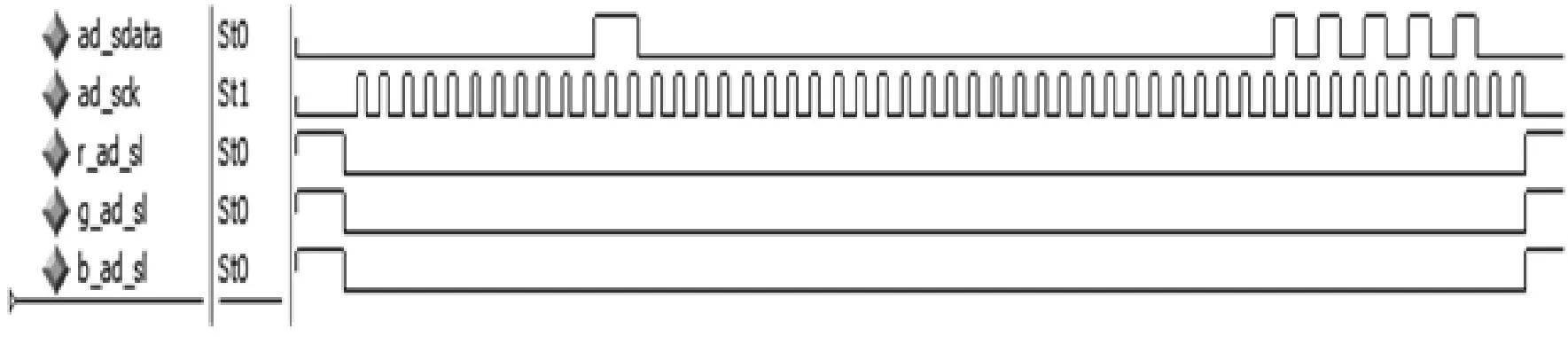

AD9945 的正常工作需要配置内部寄存器和外部时序。内部寄存器由 SCK、SDATA、Sl 三线串行配置,开始配置时,将 SL 拉低,在数据写入时钟 SCK 上升沿配置数据,寄存器初始地址配置完后,连续写入 4 个寄存器值。AD9945 内部配置时序仿真图如图 3 所示。

图3 AD9945 内部配置时序仿真图

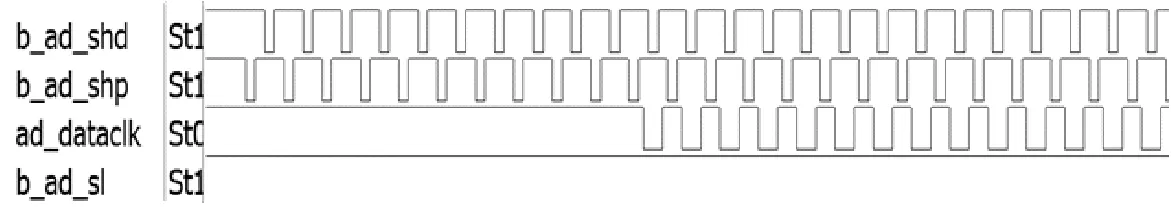

外部时序 驱动由SHP 、 SHD信号及DATACLK 输出信号组成。数据采集使用相关双采样的采集方式,在 SHP、SHD 的上升沿分别采集模拟信号的复位噪声电平及像元信号电平,通过两次采样的差值,有效地消除噪声的干扰,得到准确、低噪声的数字信号。延时10个像素时钟后,在 DATACLK 信号上升沿输出数据。AD9945 数据采集时序仿真图如图 4 所示。

图4 AD9945数据采集时序仿真图

2.3RS485串口设计

为了能够对系统进行配置,选择了抗干扰能力强、传输距离远的 RS485 通讯接口。RS485串口以协议简单、传输距离远、误码率低、抗干扰能力强等优点得到了广泛的应用。系统中 RS485 串口通信可以完成对模数转换芯片、传感器工作模式的控制等功能。

3 数据处理子系统设计

在图像数据的采集过程中,常常会有一些随机噪声影响图像数据,这些噪声会导致图像拼接、图像处理算法的准确度,为了能够有效地消除随机噪声对图像数据的影响,本系统设计采用了中值滤波的方法。

中值滤波能够在消除随机噪声的同时有效地保留图像的轮廓,不会影响后续的图像处理算法的准确性。[9]

由于系统采用的是线阵 CCD 传感器,为了能够达到实时显示与后期实时处理图像数据的要求,系统简化了普通中值滤波处理算法,将 3×3 数据模板简化为 1×3 数据模板,先对每行 R、G、B 数据进行中值滤波后再进行图像拼接。原理为每行数据中相邻的三位数据作为数据模板,取其中间值作为当前模板的数据输出。中值滤波数据仿真图如图5所示。

图5 中值滤波仿真图

Bayer数据转换系统选用了彩色线阵 CCD 传感器,传感器输出的数据为 R、G、B 三路数据,由于采用 USB 数据通信的设计,需要压缩数据量。选择了 Bayer 数据格式,Bayer数据格式是非常常见的像素分布格式,它能够将一个单平面数据转化为彩色图像数据。[10]

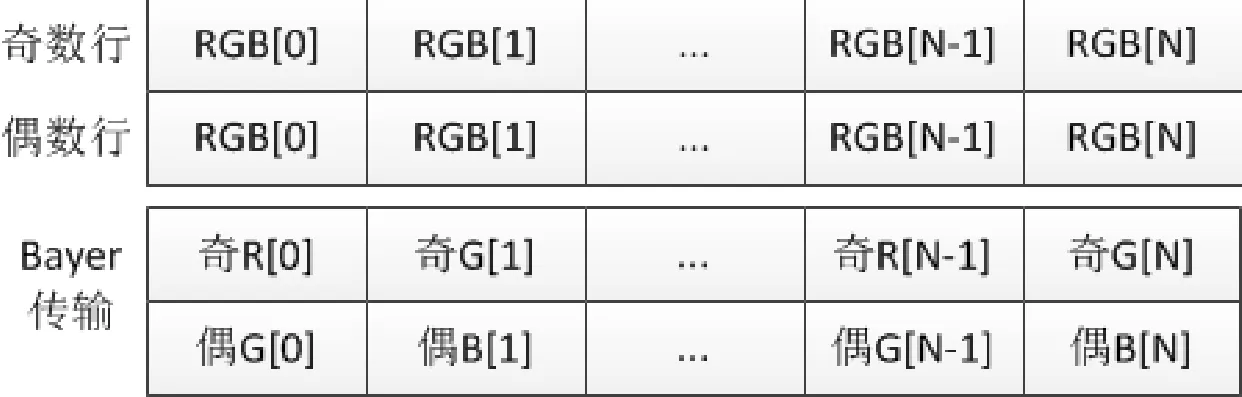

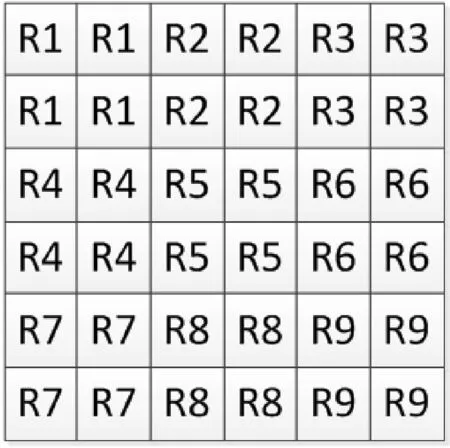

Bayer 数据格式中,红色数据分类与蓝色数据分量的采样率各为 25%,绿色数据分量采样率为 50%,奇数行保留 RGB 数据格式中的红色、绿色数据,偶数行保留蓝色、绿色数据。Bayer 数据转化方式如图 6 所示。

图6 Bayer数据转化方式

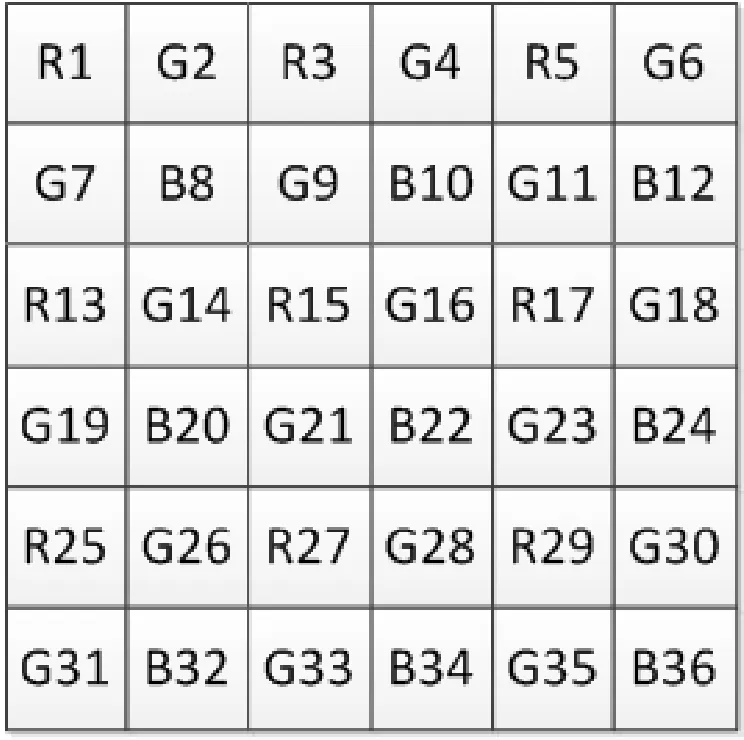

经过拼接后的 Bayer 格式下图像的数据阵列如图 7 所示。

通过 USB 传输到上位机中的 Bayer 数据,为了能够在上位机中显示图像,需要将其再次转化为 RGB 数据格式。

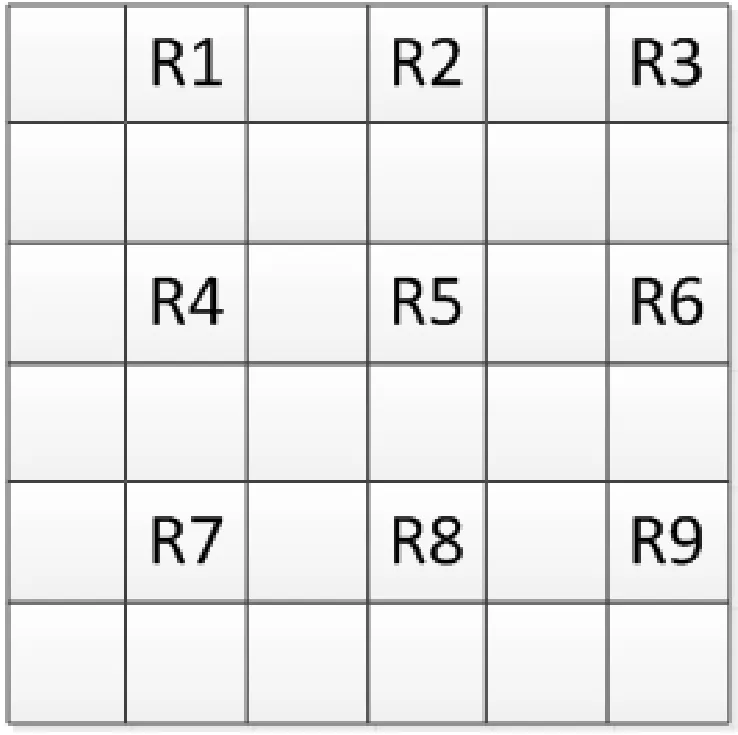

系统选用了邻近插值还原设计,[11]邻近插值还原算法的时间复杂度、空间复杂度都很小,易于硬件中实现同时节约逻辑资源。邻近插值还原算法将 Bayer 格式中的三种颜色分开还原。其中,红色分量与蓝色分量的还原方法一致。例如红色分量的还原,首先除去Bayer 数据格式中的蓝色、绿色数据分量,得到只有红色数据分量的数据流。如图 8 所示。

将整幅图像数据分割成 2×2 数据格式,每个 2×2 数据模板里仅有一个红色分量数据,其余三个数据都为空值。将空值全部插值为当前 2×2 数据模板中红色分量数据。插值后的图像数据流如图 9 所示。

图7Bayer格式下图像的数据阵列Bayer插值还原

图8红色数据分量数据流

图9插值后红色分量数据流

图10 插值前后绿色分量数据流

对于绿色分量数据的还原,将除去红色、蓝色数据分量的整幅图像数据分割为 1×2数据格式,每个模板中仅有一个绿色数据分量,将空值中插入当前模板中绿色数据分量。插值前后的图像数据如图 10 所示。

4 数据传输系统设计

由于系统对数据传输速度要求较高,选择了理论传输速度能达到 480Mb/s 的 USB2.0通信接口。经过 Bayer 数据转换后,USB2.0接口完全能够满足系统图像数据传输的要求。

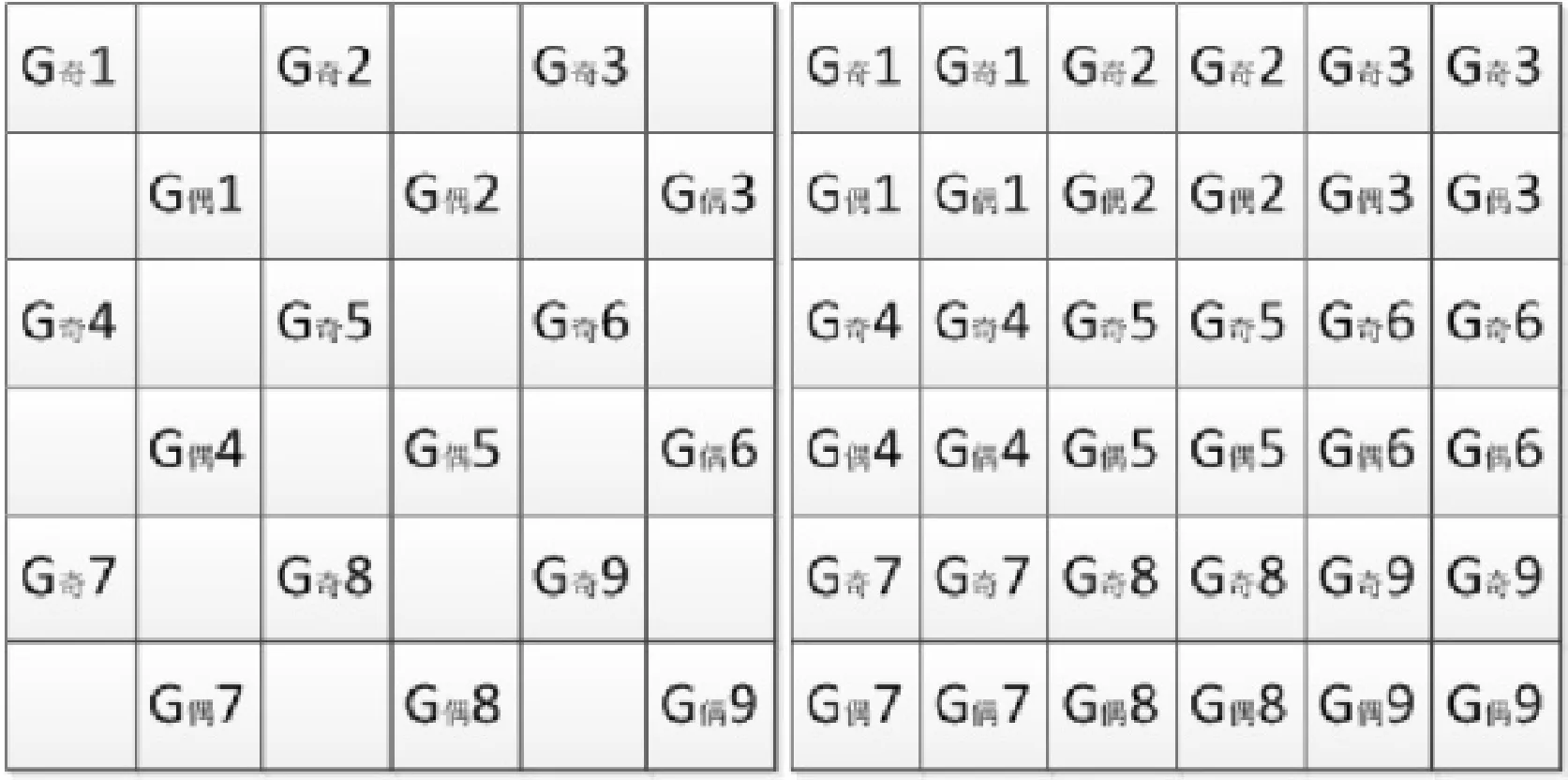

USB 接口芯片选择了Cypress公司的CY68013A 系列芯片,该芯片内部嵌入了微处理器增强型 8051,大大简化了对程序设计的要求,仅需要将寄存器和存储器配置好即可,是一款性价比极高的 USB 接口芯片,在满足系统快速数据传输的同时降低了系统开发成本,也提高了数据传输的可靠性。[12]

CY68013A 芯片的工作模式有 GPIF 模式、 Slava FIFO 模式、Ports 模式三种。系统设计选择采用 Slava FIFO 工作模式,该工作模式下数据传输模式如图 11 所示。

Slava FIFO 模式将外部设备作为主机,芯片作为从机,支持同步传输、异步传输。

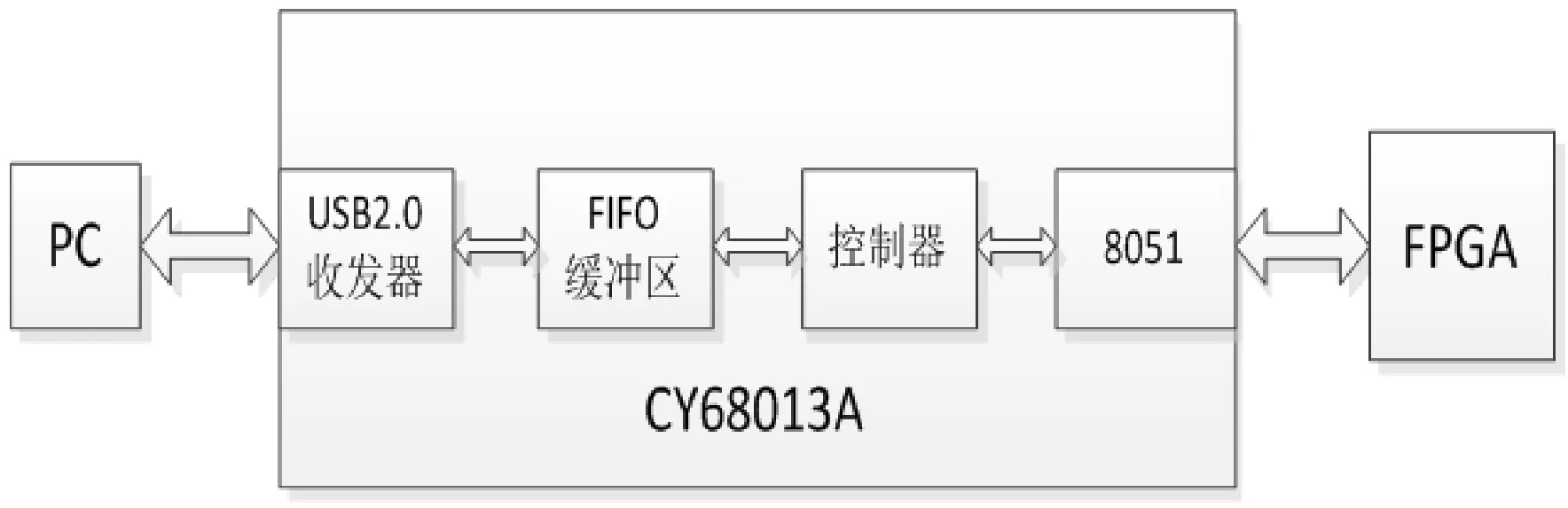

系统选择了同步 FIFO 传输模式。写请求发生时,进入状态 1;当FIFOADR指向需要的地址时,进入状态 2;当 FIFO 满状态时,在当前状态等待,无 FIFO 满状态时,进入状态 3,开始写入数据;写信号 SLWR 有效时,将数据传输到数据线上,持续一个IFCLK 时钟周期,若重复写入数据,重新进入状态2,否则进入状态 IDLE。Slava FIFO 同步传输状态机如图 12 所示。

图11USB数据传输模式

图12USB2.0传输设计示意图

5 实验结果与总结

图13 实时采集的彩色图像转化为灰度图像

本文详尽地介绍了基于FPGA 的快速图像采集系统的整体设计、逻辑设计、数据处理以及通信接口设计。逻辑设计中,系统选择了全局时钟控制,减少了异步信号的发生。实验测试结果表明,基于FPGA 的快速图像采集系统在高频率工作下数据传输稳定,图像质量清晰。能够满足多种领域都与动态图像实时显示与处理的需求。

实时采集的彩色图像转化为灰度图像如图 13 所示。

[1] 罗林.基于FPGA的快速图像处理算法的研究与实现[D].重庆:重庆交通大学计算机科学学院,2015.

[2] 孙昌君,李立京,郑帅,等.基于DSP和FPGA的被动声探测实时采集系统设计[J].传感器与微系统,2017(6):105-107,111.

[3] 陈春宁.DSP+FPGA结构图像处理系统的FPGA动态配置[J].计算机技术与发展,2014(3):42-45.

[4] 康康.基于双通道DSP+FPGA的数字信号处理系统[D].西安:西安电子科技大学研究生院,2014.

[5] 樊辉,郑力新.基于FPGA的高速工业相机的设 计与实 现 [J].微型机与应用,2014(6):77-80.

[6] TOSHIBA Semiconductors: TOSHIBA CCD Linear Image Sensor TCD2566 BFG [Z].

[7] 刘伟,齐美彬,许建平,等.基于FPGA的高速彩色线阵CCD实时图像采集系统[J].仪表技术与传感器,2017(5):91-94.

[8] Analog Devices Inc.Complete 12-Bit40MHz CCD Signal Processor AD9945 REV.B[Z].2003.

[9] 朱祥路,丁捷.基于 FPGA 实现的图像中值滤波算法[J].电子世界,2016(4):151-154.

[10] 王渊博.基于 FPGA 的 Bayer 格式实时彩色恢复系统研究[D].北京:中国科学院研究生院,2013.

[11] 王健,应骏.基于邻近插值法还原 Bayer RGB 的 FPGA 实现[J].上海师范大学学报(自然科学版),2016,45(4):411-416.

[12] 安荣,任勇峰,李圣昆.基于FPGA 和 USB2.0 的数据采集系统[J].仪表技术与传感器,2009(3):49-51.

DesignofHighSpeedLinearCCDImageAcquisitionSystemBasedonFPGA

XU Le-ling

(Document Information Center,Chizhou Vocational and Technical College,Chizhou 247000,Anhui,China)

Face the image acquisition system requirement of high frame rate, high-speed real-time, the common design using FPGA + DSP + PC, but the program cost too high and complexity. With the continuous development of FPGA, this paper has designed a kind of image acquisition, processing, display integrated in a FPGA chip system. The system can be used for image acquisition of moving objects, can realize high frame rate real-time image display, and simplify the system structure with reducing the cost. At the same time, the system has been designed to be flexible and can be applied to a variety of areas.

image acquisition; high frame rate; FPGA

2017-08-09

2017-09-20

许乐灵 (1960— ),男,安徽贵池人,池州职业技术学院图文信息中心副教授。

TP39

A

2096-2371(2017)05-0093-05

[责任编辑:张永军]