基于FPGA开发平台的H.264视频编码系统设计*

2017-11-09,,

,,

(东北大学 信息科学与工程学院,沈阳 110819)

基于FPGA开发平台的H.264视频编码系统设计*

李贞妮,李晶皎,荣超群

(东北大学 信息科学与工程学院,沈阳 110819)

针对传统基于嵌入式平台或DSP构建的H.264编码系统编码性能差,可扩展性低的缺点,提出基于FPGA开发平台设计的H.264视频编码SoC系统。本文主要介绍了其中最重要的熵编码模块。实验结果表明,与传统的基于嵌入式处理器的编码系统相比,基于FPGA开发平台的编码系统可以实现视频采集、实时编码和存储,编码后视频播放流畅,无数据丢失或数据出错等情况,系统各项功能运行良好,并且系统具有很好的可移植性与可配置性,占用资源少、速度快、具有广泛的应用前景。

FPGA;SoC;H.264;熵编码;Zynq

引 言

H.264以其优异的性能在实时网络视频通信、数字广播电视及高清视频存储播放等方面获得广泛应用,其目标是高视频分辨率,提高图像质量,并能够覆盖所有低带宽和高带宽的应用[1]。但是由于H.264编码算法比较复杂、计算量大,需要处理的数据量也比较大,因此基于传统的嵌入式处理器平台所实现的H.264编码系统,其主要核心算法依然通过软件实现,编码系统性能较差,很难达到高实时性的要求。而基于专用编码芯片或视频编码DSP所实现的编码系统,虽然编码性能较好,但系统接口和功能固定,可升级性和可扩展性较差。

因此,本文提出基于FPGA平台的H.264编码系统设计方案,利用FPGA平台,通过设计构建基于片上系统(System on Chip,SoC)的完整的H.264编码系统,其编码性能高,可编程性强,弥补了上述编码系统的不足。

1 SoC和Zynq7000 FPGA

SoC是系统级芯片的简称,系统不仅包含了处理器内核、存储器等硬件系统,而且还含有相应的嵌入式软件,是一个真正的软、硬件均具备的完整体系。利用SoC设计方法可以将一个复杂的系统集成到单一芯片中,并具有低功耗、低成本及高速性的特点。与利用ASIC实现的SoC相比,利用FPGA实现的SoC具有可配置性的特点,因此具有更好的可扩展性和可移植性。[2-3]

Zynq-7000系列是Xilinx公司提出的一款高性能和低功耗的处理器平台,是灵活和可扩展的解决方案。Zynq-7000 AP SoC平台采用ARM+FPGA的体系结构。Zynq-7000系列包含了完整的ARM处理子系统,每一颗Zynq-7000系列的处理器都包含了双核的Cortex-A9处理器,而且处理器子系统中集成了内存控制器和大量的外设,使Cortex-A9的核在Zynq-7000中完全独立于可编程逻辑单元。另外,可编程逻辑部分紧密地与ARM处理单元相结合。FPGA用于扩展子系统,具有丰富的扩展能力,有超过3 000个内部互连,连接资源非常丰富,可提供100 Gb/s以上的内部带宽。

2 H.264编码系统结构设计

本文提出的H.264编码系统在结构设计上分为三个层次,分别为SoC系统及外设硬件设计、Linux对外设的驱动,以及Linux下的系统应用软件设计。

SoC系统及外设硬件设计主要完成基于ARM Cortex-A9硬核的SoC系统的搭建,以及各处理模块或接口模块与外设器件的连接。Linux对外设的驱动主要完成的是对底层模块的驱动和访问。系统应用软件设计是在底层模块的驱动下实现各模块之间的数据传输,并编写QT GUI界面。系统结构设计图如图1所示。

图1 H.264编码系统系统结构图

3 H.264编码算法的IP核设计

本文提出了一种将H.264编码算法作为IP核的设计方法,也是基于FPGA的H.264编码系统的SoC设计的核心部分。依据H.264的编码框架,采用模块化设计方式,根据具体的数据流向将H.264帧内编码IP核划分为如下具体模块:帧内亮度预测模块(Intra4×4)、帧内色度预测模块(Intra8×8Chroma)、整数DCT变换模块(DCT)、哈达玛变换模块(DCHadamard)、量化模块(Quantisation)、逆整数DCT变换(iDCT)、逆量化模块(deQuantisation)、CALVC熵编码(CALVC)、重建模块(Reconstruction)、位转字节模块等。同时,AXI Stream接口和存储RAM数据宽度为32位,因而总线接口数据宽度也限制为32位。H.264编码IP核设计框架图如图2所示,后面主要讨论熵编码模块的设计实现。

3.1 熵编码模块的设计实现

CALVC熵编码模块是本设计的核心内容,为了使熵编码处理速度更快,采用将残差数据进行逆Zigzag扫描的方法。在CALVC熵编码模块外需要一个RAM来存储一行40个宏块的NC(Number Current)值,这里选取的RAM大小为512×5位。而在CALVC熵编码模块内部建立含有8个5位寄存器的寄存器组,来分别存储左侧亮度宏块和色度宏块的NC值。在整个编码模块中,首先要获得的是统计信息,即编码一个4×4块前先得到该块的非零系数数目和拖尾系数数目,同时也需要获得计算后的NC值,用来判断查找表。

图2 H.264编码IP核设计框架图

经过16个时钟周期,经过逆Zigzag扫描后的4×4块系数串行读入到CALVC编码器的寄存器中。与此过程中,幅值计数器分别判断输入的系数值是0还是非0值。如果输入的系数是非0值,则存入到幅值寄存器中。在此同时,拖尾系数计数器、非零系数计数器和零值个数计数器将在每读入一个系数时更新一次。16个时钟周期扫描结束后,将根据查表序号寄存器获得查找表的地址,然后输出查表后得到的码字。

熵编码模块主要划分为如下小模块:统计模块、NC计算模块、编码coeff_token、编码trailingone_sign、编码levels和编码totalzeros。由于待编码系数数据块有4×4和2×2两种,输入的数据数有16、15、4三种情况,统计模块通过计数输入的有效数据数目maxcoeffs来判定当前处理的是4×4块还是2×2块。如果maxcoeffs为4,则当前处理的是2×2块,那么在对coeff_token和totalzeros进行编码时,需要选择直流编码表格。

计算模块根据当前4×4块的位置确定使用NC的来源,计算结果暂存在NC寄存器中。coeff_token的码字从4个变成表和一个定长表中获得,totalcoeffs和trailingones是表的索引。如果使用H.264的标准表,码字最长为16位,在构建码表时需要设计数据位数为16位的ROM区,会浪费较多的资源。通过对4个变长表进行研究,发现码字的构成都是若干个0作为前缀,后缀为“有意义”的码字,而后缀长度均不超过6位。因此,本文对原有的码表进行了改造。并且,为了减少逻辑资源,用判断NC高位是否为零代替判断NC的取值范围。trailingone_sign编码码字由统计模块完成,码字的长度等于trailingone。totalzeros的编码通过查表完成,同样为了节省硬件资源,对该码表进行了精简改造。

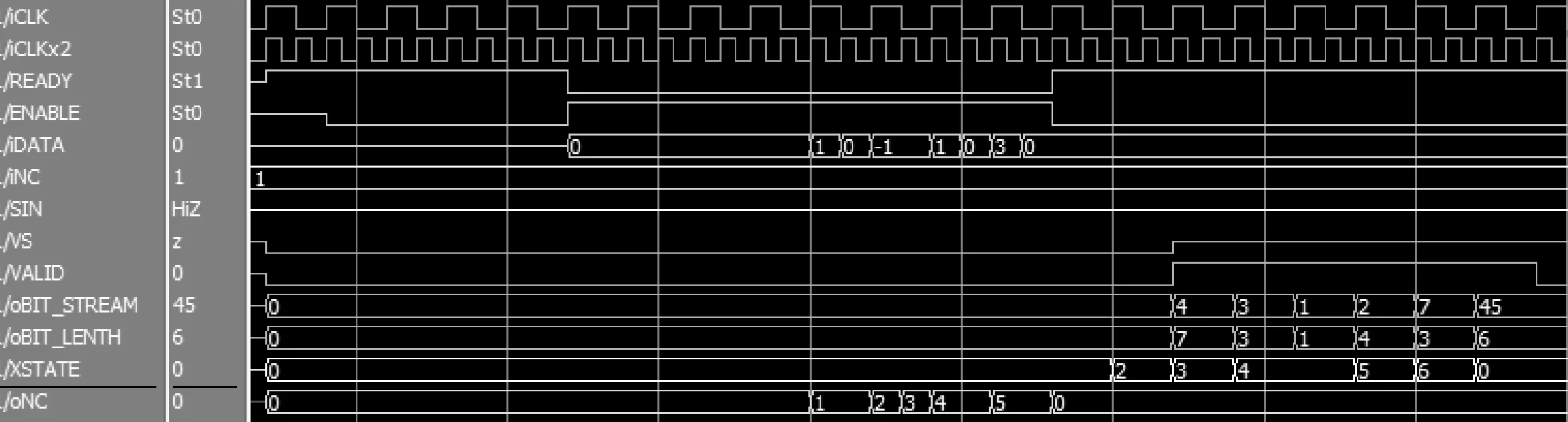

图3 CAVLC熵编码模块仿真图

用查表法计算Exp-Golumb熵编码,会占用较多的硬件资源。通过归纳总结Exp-Golumb熵编码的编码规律,通过使用构造码字的方式计算码字。对于ue(v),设定编码后码字的比特串格式为“前缀+后缀”,从而有:

① 后缀=codeNum+1。如codeNum=3,则后缀值为4,后缀的比特串为100。

② 前缀的比特数较后缀的比特数少1,且前缀的各位比特为0,如codeNum=3,则最终编码所得的比特串为00100。

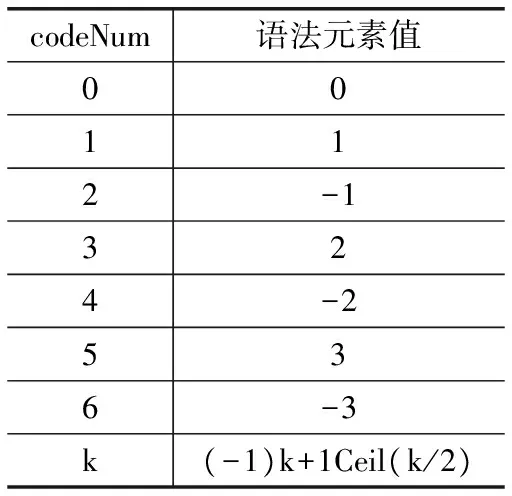

表1 语法元素值与codeNum关系

对于se(v),则按照表1进行转换 ,其中Ceil()函数表示向上取整。

① 语法元素值为负数,则乘2取反,转换成 “;”。

② 语法元素值为正数,则乘2减1,转换成“。”。

然后按ue(v)编码规则进行编码。

因而,对于16位的有符号语法元素signNum[15:0],若最高位为0,则语法元素值为正,那么后缀suffix=signNum×2-1+1=signNum×2,通过右移1位完成;若最高位为1,则语法元素值为负,那么后缀suffix=-signNum×2+1, signNum的负值使用减法器完成,将结果右移1位,并将最低位置1。得到后缀suffix后,再确定码字的长度codelenth,并将高位补零。码字长度的确定方法如下:码字的长度一定是奇数,而且是后缀长度suffixlenth的两倍加1。通过判断suffix高位零的个数就可以得到suffixlenth。如果suffix[15:1]均为零,那么suffix只可能是0或者1,因而suffixlenth=1,没有前缀,codelenth=1;如果suffix[15:2]均为零,那么suffix只可能是2、3,因而suffixlenth=2, codelenth=3;其他高位为零的判断情况类似。高位为零的判断使用优先级选择器。

4 实验结果

4.1 熵编码模块的仿真测试结果

针对实现的熵编码模块,使用ModelSim 10.0a对其进行功能仿真,并使用Xilinx ISE测试模块的最大工作频率Fmax。

根据表1可知,0的有符号Exp-Golumb熵编码后的码字是1’b1,;1编码后的码字是3’b010,码字长度为3;-1编码后的码字是3’b011,码字长度为3;2编码后的码字是5’b00100,码字长度为5;-2编码后的码字是5’b00101,码字长度为5。Exp-Golumb熵编码仿真图如图4所示。

图4 ExpGolumb熵编码模块仿真图

4.2 H.264编码系统的性能测试结果

测试采用的硬件开发平台为FPGA Zynq-7000,开发环境为Xilinx ISE 14.4 (64位)。使用Xilinx XPS (Xilinx Platform Studio) 构建SoC系统,将H.264 编码 IP核以及HDMI控制IP核添加到SoC上。为了比较准确地得到测试数据,系统并非实时采集和编码,而是采集完一定帧数后再进行编码过程。同时,由于所实现的编码系统只针对分辨率为640×480的视频,业内并无这样分辨率的标准测试视频,因而无法将本编码系统与其他编码系统直接进行对比测试。为了解决该问题,本文提出采用宏块编码速度,即以宏块为单位来考虑编码系统的性能。宏块编码速度MBencodespeed的定义如下:

MBencodespeed=MBtotal/t=Frametotal×MBnum/t

(1)

其中,MBtotal是编码宏块总数,Frametotal是编码帧总数,而MBnum是编码一帧中宏块总数。MBencodespeed的单位是宏块每秒(mbps)。

为了测试系统的编码性能,在设定QP=28的前提下,使用编码系统对不同场景进行多次编码,并分别计算编码速度、压缩比以及PNSR,以确定编码效率。对比测试对象为在ARM926EJ-S平台实现的H.264编码系统,QP=28。在关闭QT界面下只进行编码测试,编码速度对比测试结果如表2所列。

表2 编码速度对比测试表

可知本系统的平均编码速度能够达到21.69 fps(26 030 mbps),是ARM926EJ-S平台的88.9倍。由于本系统只实现帧内预测编码,并没有实现帧间预测,因而本系统在压缩性能上和ARM926EJ-S平台仍有一定差距,可通过后续添加帧间预测模块来改善。编码后视频Y分量、Cr和Cb分量的平均PSNR分别达到均36.92 dB、39.59 dB和38.06 dB,编码后视频质量良好。

结 语

[1] 罗军,黄启俊,常胜,等. H.264中整数变换与量化的FPGA实现[J].中国图像图形学报,2011,16(5):740-745.

[2] L Pei, Z Jian.A high reliable SoC on-board computer based on Leon3[J].2012 IEEE International Conference on Science and Automation Engineering(SCAE 2011),2012(1):360-363.

[3] H ChunMing, W ChienMing, Y Chih-Chyau, et al.Programmable System-on-Chip (SoC) for silicon prototyping[J].IEEE Transactions on Industrial Electronics, 2011,58(3): 830-838.

H.264EncodingSystemDesignBasedonFPGAPlatform

LiZhenni,LiJingjiao,RongChaoqun

(College of Information Science and Engineering,Northeastern University,Shenyang 110819,China)

The H.264 encoding system based on the traditional embedded developing platform has many disadvantages such as has low encoding performance,low extensibility and so on.In order to solve the problems,the H.264 video encoding SoC system based on FPGA development platform design is proposed.The most important module is the entropy encoding module in the system.The experiment results indicate that,the encoding system can realize the video collecting,encoding,and storage comparing with the H.264 encoding system based on the traditional embedded developing platform.After encoding,the video plays smoothly,without data missing or errors.Furthermore,the system has good portability and configurability,therefore it has a broad application prospects.

FPGA;SoC;H.264;entropy encoding;Zynq

国家自然科学基金资助项目(61370153)。

TP391.41

A

2017-06-07)