Altera MAX V CPLD的工程设计应用及系统开发

2017-11-09,

,

(北京理工大学 机车学院,北京 100081)

AlteraMAXVCPLD的工程设计应用及系统开发

张志明,崔涛

(北京理工大学 机车学院,北京 100081)

本文阐述了Altera MAX V最小系统从硬件原理图到PCB设计、从软件QuartusII编写VHDL到Modelsim-Altera的软件仿真,以及最终的程序下载到开发板上的整个工程设计调试过程,为后续的Altera MAX V工程设计应用提供技术参考和支持。

Altera MAX V;VHDL;仿真;工程调试

引 言

Altera MAX CPLD广泛应用于电子电器行业,几乎可实现所有数字和模拟控制功能,而且容易集成到系统中。采用CPLD器件,可以解决电路板级问题,使设计人员主要精力集中在更复杂的设计难题上。近年Altera的MAX II系列在CPLD市场上占据领导地位,其采用了TSMC成本优化的1.8 V、0.18 μm、6层金属Flash工艺,广泛应用在大批量消费类、通信、工业和计算机行业。目前MAX II系列已停产,Altera推出了MAX V系列,静态功耗低至45 μw,密度在40~2 210个逻辑单元之间,引脚布局中提供更多的I/O和逻辑,提供各种低成本、无卤素封装(EQFP、TQFP、MBGA),满足环境标准要求,对于Altera MAX V进行工程应用的开发设计、调试非常重要。

1 工程设计应用开发整体规划

从Altera官网MAX V型号中选择价格、结构、性能等处于中等的5M570ZT100I5芯片,软件采用Quartus II进行编写,并用Modelsim-Altera进行仿真,硬件电路采用Protel进行设计。Quartus II的软件设计采用VHDL语言编程,因其语言构架类似于C语言,易于理解,在Quartus II中也有全面的VHDL语言模板可以参照,易学易用。

在整个工程设计应用中,先进行硬件电路的设计,在硬件电路制造阶段进行VHDL语言的测例编程和模拟仿真,最终下载到硬件电路中进行验证调试。

2 硬件电路设计

2.1 原理图设计

原理图设计分为供电电路设计、时钟电路设计、程序下载电路设计、普通I/O端口的输入/输出设计。

(1)供电电路设计

根据官网资料介绍,MAX V系列的I/O电压为3.3 V,Core Voltage为1.8 V,因此需选用AMS1117的5 V转3.3 V、5 V转1.8 V两种稳压器,选用SOT-223封装类型,在VCCINT引脚(pin_13)上并联10 μF电容。

(2)时钟电路设计

MAX V系列的I/O口电压为3.3 V,因此要选用3.3 V的有源晶振,在clk引脚(pin_12)和晶振out引脚之间用33 Ω电阻连接。

(3)程序下载电路设计

MAX V系列程序下载电路与MAX II系列的原理相同,选用标准BDM插头,TMS、TDI引脚采用3.3 V供电,2只引脚与3.3 V电源之间串联10 kΩ电阻;TCK引脚与GND之间串联10 kΩ电阻。

(4)普通I/O端口的输入输出设计

普通I/O端口既可以作为信号输入接口,也可以作为信号输出接口。I/O端口的输入/输出电压为3.3 V,无其他电路设计的特殊要求。本次将其直接引出,方便测例的调试验证。

2.2 PCB设计

创建PCB项目文件,首先“选择追加已有文件到项目中”,选择上面所建立的原理图文件,根据已有的原理图文件生成PCB图(如图1所示),重点对时钟信号线、电源线、地线、TCK、TDO、TDI、TMS等进行手工布线和线宽设置,其他线可在元器件摆放完后进行自动布线操作。

图1 PCB图

3 软件设计

3.1 VHDL语言编程设计

MAX V采用Quartus II 12系列版本进行VHDL语言设计,在设计过程中要确保工程名称与文件名称命名一致,创建工程后,新建VHDL 文件,写入测试语句:

library ieee;

use ieee.std_logic_1164.all; use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity qudong570 is

port

(clk : instd_logic; p : out std_logic;

q : outstd_logic);

end entity;

architecture ad of qudong570 is

signal num:natural:=0; signal cut:natural:=0;

signal i:natural:=0; signal vet:std_logic:='1';

signal vvv:std_logic:='1';

begin

process (clk)

begin

if (clk'event and clk='1') then

num<=num+1;cut<=cut+1;

case num is

when 640=> vvv<='0'; when 960=> vvv<='1';

when 2000=> vet<='0';vvv<='0';cut<=0;i<=1;

when 2900=> cut<=0; when 3800=> cut<=0;

when 4700=> cut<=0; when 9200=> cut<=0;

when 16400=> num<=0;vet<='1';vvv<='1';cut<=0;i<=0;

when others=>NULL;end case;

if (cut=1008 and i=0)then

vvv<=vvv xor '1';cut<=960;/*脉宽48 μs*/

end if; end if;

end process; q<=vet; p<=vvv;end ad;

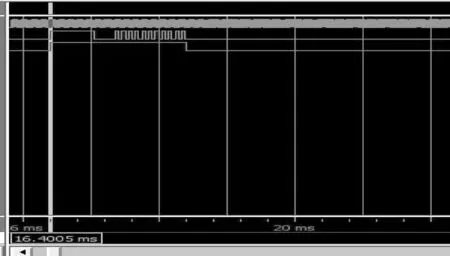

3.2 对VHDL语言程序的仿真

采用Modelsim-Altera对所编程序进行仿真,在仿真之前先用Quartus自动生成测试文件:[processing]-[start]-[start Test Bench Template Writer]。打开生成的测试文件,将时钟设定为500 ns,保存后即可在Quartus中点击[start compilation]进行仿真,仿真结果如图2所示。

图2 PCB仿真波形

4 工程调试

图3 采集真实波形

将编写好的程序下载到开发板上,下载程序过程中,先将下载器与开发板BDM头插接好,再与PC机的USB相连,最后将开发板与5 V直流电源接通,下载程序成功后,将开发板重新上电即可运行程序。将开发板与示波器连接,测试开发板输出信号,信号如图3所示,与Modelsim Altera仿真结果一致,开发板调试成功。

EngineeringDesignandSystemDevelopmentofAlteraMAXVCPLD

ZhangZhiming,CuiTao

(School of Locomotive,Beijing Institute of Technology,Beijing 100081,China)

In the paper,Altera MAX V minimum system is introduced,from the principle diagram of hardware to PCB design, and from a software quartus II writing VHDL to Modelsim-Altera software simulation,and the program downloaded to the development board,that provides technical reference and supports for Altera MAX V engineering design applications.

Altera MAX V;VHDL;simulation;debugging

TP338

A