一种用于水下测试的可扩展高速固态存储系统设计

2017-11-03马游春吴正洋

马游春,姜 德,吴正洋

(中北大学电子测试国家重点实验室,仪器科学与动态测试教育部重点实验室,太原 030051)

一种用于水下测试的可扩展高速固态存储系统设计

马游春*,姜 德,吴正洋

(中北大学电子测试国家重点实验室,仪器科学与动态测试教育部重点实验室,太原 030051)

针对图像数据采集的高速、可靠性等存储要求,设计了一种可扩展高速固态存储系统。系统固态存储单元使用FPGA控制FLASH构建存储阵列,同时结合DDR技术和流水线设计相结合的方法来提高其存储速度。系统接口采用用于高速数据传输的FMC接口,其具有多对吉比特接口信号引脚,结合板间高速视频数据的传输使用FPGA高速串行接口技术(Aurora协议),使系统能扩展多个存储BANK。实验结果表明该系统能可靠的提高系统的存储速度和存储容量并不丢失数据。

可扩展;高速;NAND FLASH;Aurora;FMC

随着遥测数据、空中监测、视频采集等各个领域的快速发展,高速数据的存储对存储系统的存储容量、存储速度和可靠性提出了更高的要求,目前大部分视频采集系统设计都是采用DDR3等高速存储器进行数据缓存,再通过高速接口将数据和上位机板卡进行传输、显示处理[1],这种采集方式具备速度快、操作简单的优势,但由于DDR3、SDRAM掉电容易丢失数据,不利于远距离这种恶劣环境下实验数据的回收,如水下测试、多点爆破数据的采集等,此类实验的高速数据的固态存储显得尤为重要。

本文针对水下视频测试数据固态存储系统的要求,以高速FLASH为存储介质,对大容量的图像数据存储进行了研究。同时针对测试环境和测试要求的多样化,设计了可扩展系统对存储模块进行了通用性的设计,根据具体实验所需要采集数据的速度和大小对固态存储模块进行扩展。与以往的高速固态存储系统[2-4]比较,该系统在FLASH控制和流水线管理上都有了进一步的优化,使其具有灵活性更高,速度更快的优势。

1 高速固态存储系统

本系统实验对象为水下视频测试数据的采集存储,用于监测水下实验目标的动态特征,其技术协议要求为:图像分辨率:1 280 pixel×960 pixel,帧速率:大于等于200 frame/s,记录时间大于10 s,由此可计算系统每秒的传输速率至少达到2.3 Gbit/s,存储数据容量大于2.9 GByte。

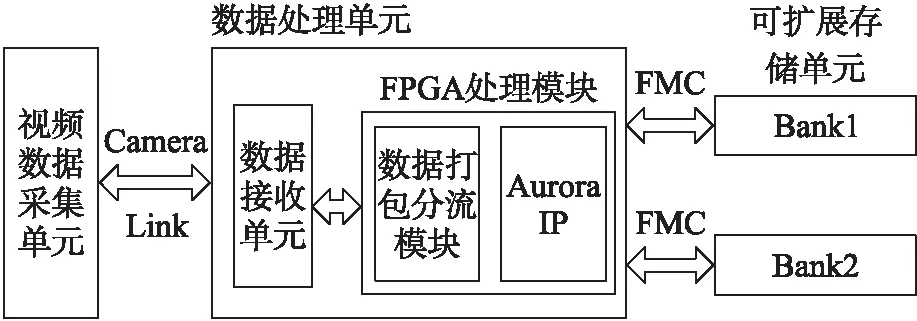

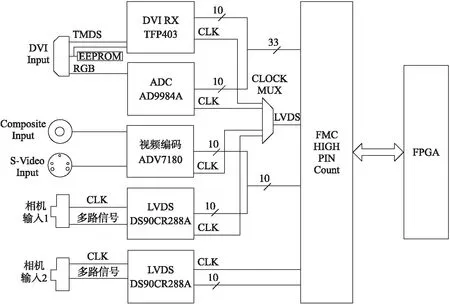

如图1为本文设计的固态存储系统框图,系统一共由三部分组成:数据采集单元:该单元选用acA2000-340Kc的CMOS工业相机作为视频采集器件,相机的分辨率设置为1 280 pixel×960 pixel,传输速率为200 frame/s,像素点的位宽设置为12 bit,相机固定焦距为10 cm。数据处理单元:采用3片DS90CR288A芯片接收Camera Link数据,每片负责接收4路LVDS视频信号和1路LVDS的CMOS相机时钟,将其转换成80位并行的TTL视频数据和3路的TTL相机时钟信号。FPGA作为主控芯片将数据进行分流、打包,通过GTX接口结合Aurora协议传输给存储单元。可扩展存储单元:用于存储处理单元传输的视频数据,通过高速FMC接口与处理单元连接(具体功能见1.3节)。

图1 系统框图

1.1 FMC接口

FMC(FPGA Mezzanine Card)用于连接FPGA引脚和FMC子板的I/O接口,其引脚分为电源信号引脚、吉比特接口信号引脚、普通用户信号引脚、JTAG引脚及时钟信号引脚等[5]。

系统采用400引脚的HPC(High Pin Connector)作为其FPGA的扩展I/O口,排列方式为40行10行,图1中数据采集单元设计为带高速扩展口FMC母座连接器的载卡,可扩展存储单元为带FMC工座的子板。因为信号传输及其时钟信号引脚在FMC中都是按照差分对标准来定义的,设计中其对应的I/O都使用LVDS差分信号驱动。夹卡层与载卡之间的总带宽最高能够达到40 Gbit/s,适合作为高速的扩展口,用于保证信号传输的完整性,硬件电路的设计需要注意在FMC差分口收发端分别加入100欧的阻抗匹配。

如图2 为FMC扩展连接模型,由于其支持多种电气特性,能方便的进行板间的信号稳定传输,本系统扩展的主要通道为GTX接口,利用带20对的吉比特收发器的FMC接口,结合Aurora IP协议,每个独立存储单元绑定2个GTX传输,则可扩展至10个独立存储单元,同时结合FPGA并行处理能力,可灵活的编写出对应的扩展代码,能快速开发出针对不同速度和容量的实验产品。

图2 FMC连接模型

1.2 Aurora协议

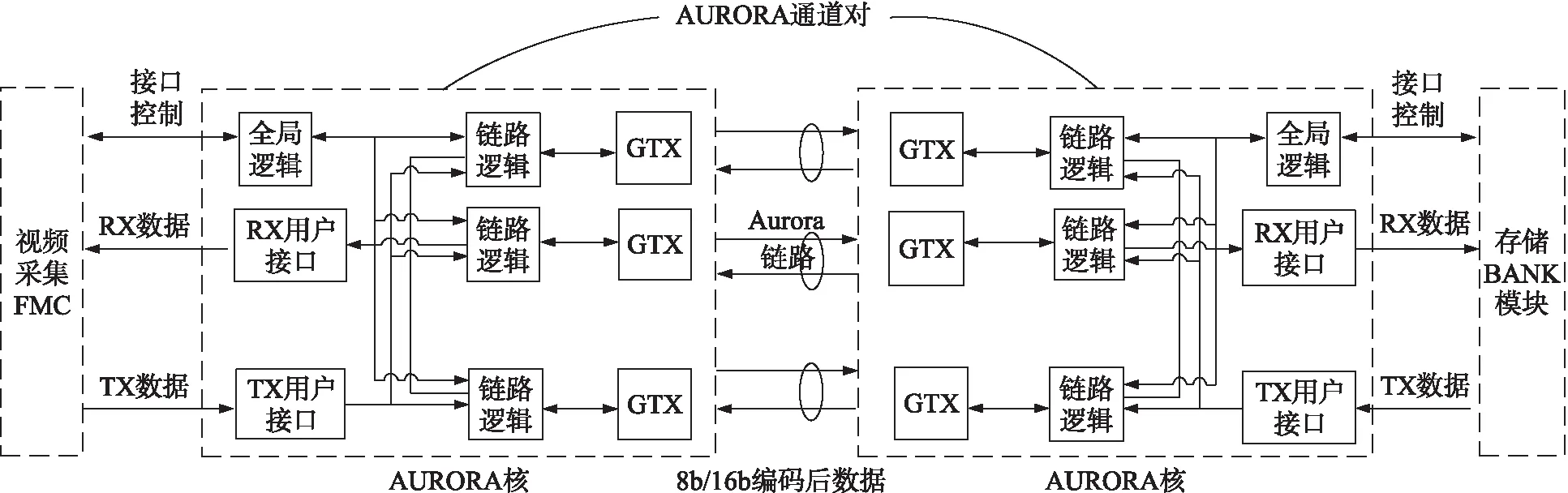

本系统的数据处理单元使用Virtex-6(XCVU190)FPGA作为主控芯片,其具有24个的高速串行GTX收发器,内置高速串并转换、时钟数据恢复、线路编/解码、时钟修正和通道绑定等功能电路,是Aurora协议传输的物理层基础[6-8],Aurora的板间数据交换的结构如图3所示。

图3中的Aurora IP核在GTX的PCS子层内部使用8B/10B对数据进行硬件编码,将8 bit位宽数据转换为5个以上不连续的“1”或“0”的10位比特码[9-12]。GTX外部输入时钟由100 MHz的差分晶振提供,因一个外部时钟能驱动3个通道(4个GTX组成一个通道),而一个通道也能由2个差分时钟驱动,满足系统的扩展功能。Aurora数据采用帧传输模式,定义其传输一帧的长度为图像数据的一行,即一帧有1 280个像素点,共需要960帧来完成一幅图像的传输,同时在图像数据添加了完整的帧标志(EF A5 EF A5)和行计数(DC EF Fx xx)。

图3 Aurora板间数据交换模型

系统所用的Aurora IP发送和接收的位宽设置为16 bit,在图像数据传输过程中,Aurora数据链路层协议制定了相关的顶层UFC模式握手协议[13],来完成扩展BANK自校验,返回rdy_flag信号,系统在检测rdy_flag有效后,开始进行测试数据的传输。一组数据传输中,前960帧为视频数据帧,第961行为信号帧,其中信号帧信息包括命令位域frame[0:15]和校验位域frame[32:63]:命令位域用来一帧数据传输结束的请求,保证其对应的BANK正确进行数据存储,准确进入时钟补偿的计数模块;校验位域用于确定图像数据按固定帧传输计数,判断是否出现丢帧的现象,完成后进入计数延时,准备进行下一帧存储。

图5 FLASH DDR存储模式[15]

该系统在解决时钟补偿不定期引起中断的问题上,采用相机提供的84 MHz的时钟驱动计数模块进行延时补偿,因为每5 000个user_clk时钟需要6个user_clk的时钟补偿,而本系统中一行图像数据传输完成后,其相机本身会产生8个相机输出时钟周期的延迟,即完成1 280个周期后,会自动调入8个周期的DO_CC,然后再进行行切换。

1.3 可扩展存储单元

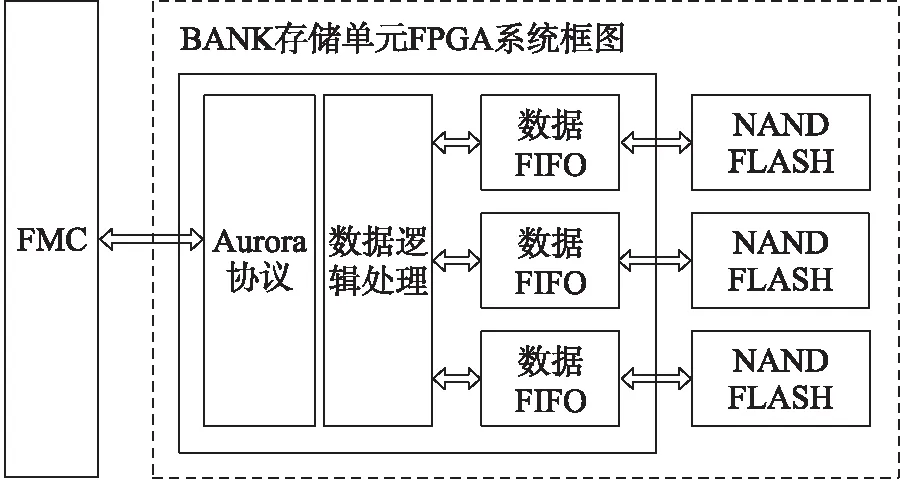

如图4所示,为可扩展存储BANK的系统框图,BANK内FPGA选用资源相对少的Spartan6的 XC6SLX100,其通过自身的GTX硬核模块和Aurora协议对数据采集模块的高速的串行数据进行解码,转换为32位低速的并行数据,经过FIFO后存储到3片FLASH中。

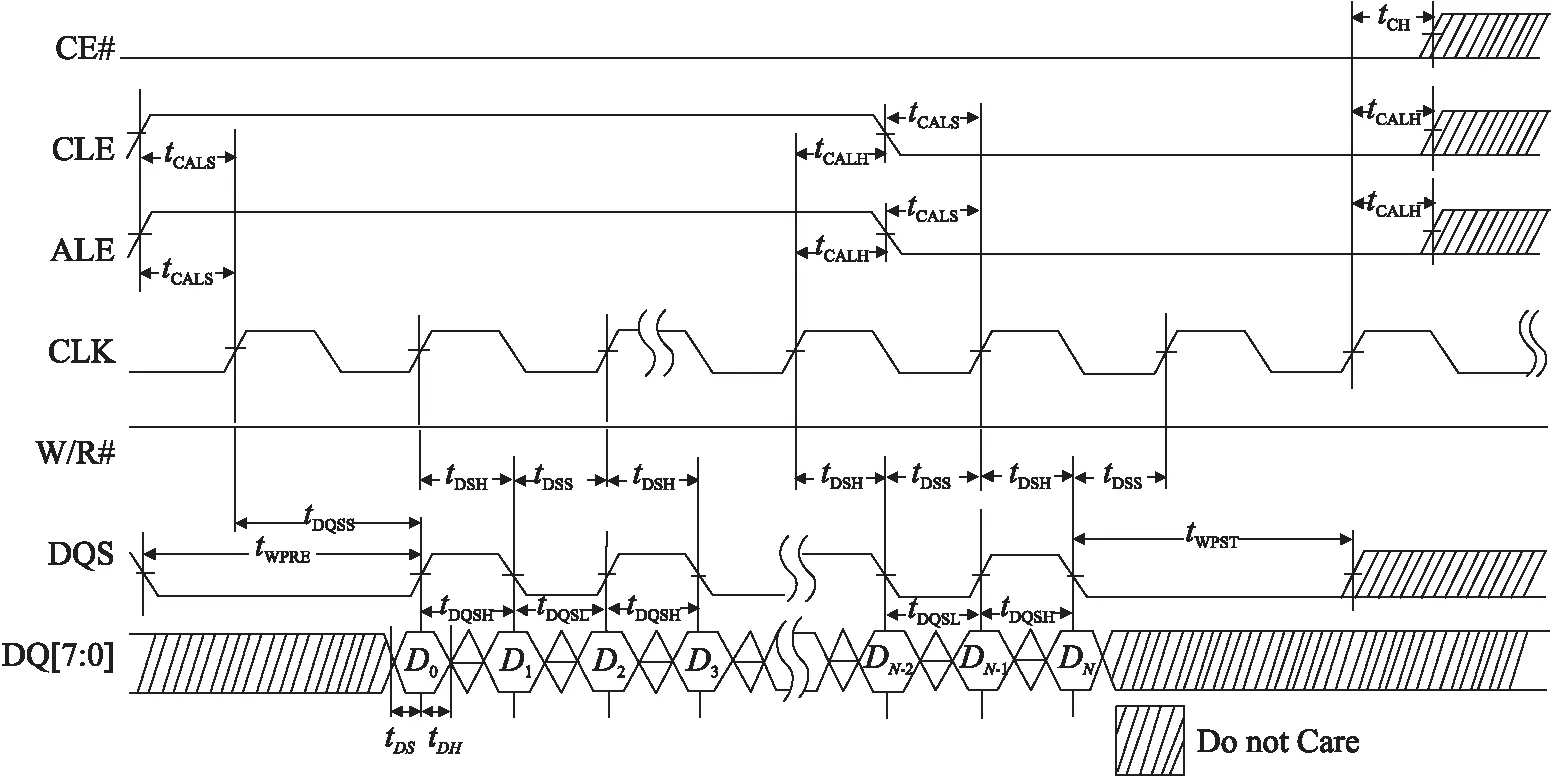

图4 单BANK系统框图

NAND FLASH存储芯片使用镁光的MT29F128G08CECAB,其单片的存储容量为16 Gbyte,具有DDR读取和写入数据的高速传输特性如图5所示,为该型号FLASH的同步DDR存储模式,即在DQS信号的每个上升沿和下降沿都能传输数据[14],因此设计中保持CLK信号和DQS信号同步就能实现使用其同步的DDR存储技术[14]。

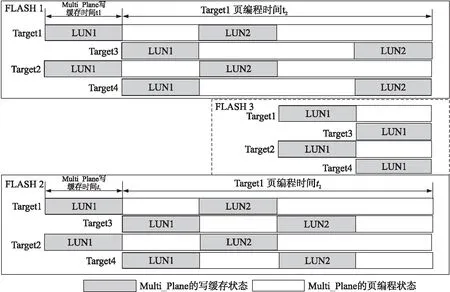

根据FLASH芯片结构的LUN单元和DDR存储技术,使用3片FLASH构建32 bit位宽的流水线存储模式,其逻辑结构如图6所示,FLASH 3为补充页编程时间(230 μs)的空闲状态,使用其中的LUN 1(8 Gbyte)作为补偿存储,主存储模块为FLASH 1和FLASH 2。其坏块管理模式为实时存储坏块信息和自刷新技术;即系统上电的初始化阶段,对FLASH的存储块进行检测,对3个FLASH的坏块地址相与后[16],将坏块信息存储到FLASH 3的LUN 2的存储单元中。在写入数据时按顺序读取LUN 2中的坏块信息进行仲裁,缩短独立进行坏块检测的时间,其速度在单个存储单元测试中可提升到240 Mbit/s,即能完成1.87 Gbit/s连续数据的存储。

图6 FLASH流水线控制示意图

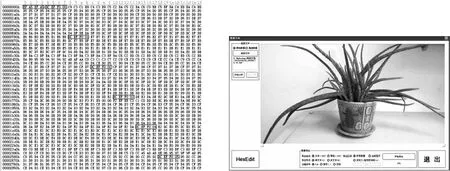

图7 图像数据显示

2 高速数据固态存储实验

根据系统设计要求,对系统进行地面自测环境搭建,主要由数据采集模块、主控FPGA数据处理模块和2个可扩展存储模块组成,完成对CMOS相机高速视频数据的存储(参数配置按照技术协议规定)。系统需要实现大于2.3 Gbit/s的高速视频数据的存储带宽,因此扩展了2个BANK存储单元,构建成64 bit宽度的数据传输带宽。

系统实验环境搭建的数据流传输的过程为:系统对外部传输的串行信号在Aurora IP核中进行解码,通过跨时钟域的FIFO存储到FLASH中。最后,通过地面读数板卡将图像数据进行显示,图7(左)为本次实验一帧图像数据的结果,图7(右)为其对应图像显示,从数据标志可以看出帧标志为“EF A5 EF A5”一行计数为“DC EF F0 00”至第6行计数为“DC EF F0 05”计数连续,没有出现丢数的现象。

3 结束语

本文采用高性能Virtex-6系列FPGA和NAND Flash DDR存储技术构建高速数据可扩展存储系统。板间传输采用了Aurora协议结合FMC接口,保证了高速信号板间传输的完整性的同时,能灵活的实现系统的可扩展性,可根据所需要采集的数据流的大小和速度选择需要扩展的存储BANK数量。

实验结果表明,该高速固态存储系统具有体积小、可靠性高的特点,其可扩展性强能满足大量的高速数据存储需求。

[1] 马游春,王悦凯,丁宁. 基于DDR3-SDRAM的高速视频传输系统[J]. 电子技术应 用,2015(12):69-71.

[2] 吴凡. 基于FPGA的NAND FLASH的嵌入式存储系统设计[J]. 电子科技,2016(3):97-101.

[3] 周仕成,殷科军,舒汀,等. 基于NAND FLASH 的高速海量存储系统设计[J]. 信息技术,2015(12):117-120.

[4] 赵亚慧,金龙旭,等. 基于NAND Flash 的高速大容量存储系统设计[J]. 电光与控制,2016(5):71-75.

[5] Xilinx. I/O Design Flexibility with the FPGA Mezzanine Card(FMC)[Z]. 2009.

[6] 李维明,陈建军,陈星锜. 基于Aurora协议的高速通信技术的研究[J]. 电子技术应用,2013(12):37-40.

[7] 胡谨贤,张英波,黎仁刚. 基于Aurora协议的光传输方案验证[J]. 科学技术与工程,2012(30):8038-8041.

[8] 岳振,吕波,张涌,等. 基于Aurora协议的高速图像传输和通信平台设计[J]. 电子技术应用,2014(8):7-9.

[9] 李林军,王勇. 基于Virtex-5的串行传输系统设计与验证[J]. 电子设计应用,2009(12):43-45.

[10] 武荣伟,苏 涛,洪中英. RocketIO在高速数据通信中的应用[J]. 通信技术,2010(11):9-11.

[11] Xilinx. Aurora protocol specification[Z]. 2007.

[12] Xilinx. Virtex_6 FPGA GTX transceivers user guide UG306[Z]. 2011.

[13] 张鹏飞,杜雨洺. 基于FPGA的高速数据转存系统[J]. 计算机系统应用,2014(2):86-90.

[14] 姜德,马游春,王悦凯,等. 高速数据同步存储系统设计[J]. 电子器件,2016,40(6):1421-1424.

[15] Micron. MT29F128G08AUCBBNAND Flash Memory datasheet[Z]. 2015.

[16] 张胜勇,高世杰,吴志勇,等. 基于FPGA的NAND FLASH坏块处理方法[J]. 计算机工程,2010(6):239-240.

AScalableHigh-SpeedSolidStorageSystemforDataCollectionUnderwater

MAYouchun*,JIANGDe,WUZhengyang

(National Key laboratory for Electronic Measure,Ement Technology,Key Laboratory of Instrumentation Science and Dynamic Measurement of Ministry of Education,North University of China,Taiyuan 030051,China)

A scalable high-speed solid-state storage system is designed for high-speed,reliability and other storage requirements of image data acquisition. The system solid-state storage unit uses the FPGA control FLASH to construct the storage array,simultaneously unifies the DDR technology combined with the pipeline design method to enhance its storage speed. The system interface adopts FMC interface for high-speed data transmission. It has many pairs of gigabit interface signal pins,and transfers high-speed video data between boards using FPGA high-speed serial interface technology(Aurora protocol),so that the system can expand multiple storage BANK. Experimental results show that the system can enhancing the system’s storage speed and capacity stably without dropping date.

scalability;high-speed;NAND FLASH;aurora;FMC

10.3969/j.issn.1005-9490.2017.05.031

2016-09-03修改日期2017-03-09

TP274

A

1005-9490(2017)05-1214-05

马游春(1977-),男,副教授,江苏人,主要研究方向为测试计量技术与仪器,电子测试仪器与系统,879406889@qq.com;

姜德(1992-),男,硕士研究生,山西人,主要研究方向为高速数据采集与存储,电子测试仪器与系统,397735504@qq.com。

项目来源:国家自然科学基金项目(61673129)