2.5 Gbit/s无电感高灵敏度宽动态范围前置放大器设计

2017-11-01朱铁柱莫太山叶甜春

朱铁柱,莫太山,叶甜春

2.5 Gbit/s无电感高灵敏度宽动态范围前置放大器设计

朱铁柱1, 2,莫太山1, 3,叶甜春1, 2

(1. 中国科学院微电子研究所,北京,100029;2. 杭州中科微电子有限公司,浙江杭州,310053;3. 嘉兴禾润电子科技有限公司,浙江嘉兴,314001)

基于0.18 μm RF CMOS工艺设计一种应用于无源光网络光接收机的无电感型2.5 Gbit/s前置放大器。该前置放大器主要包括跨阻放大器、单端转差分运算放大器和输出级电路。跨阻放大器基于3级推挽反相器结构,具有高增益和低噪声的特点,提高前置放大器的灵敏度;分析零点补偿原理,设计位于反馈环路之中的虚零点,提高跨阻放大器的工作速率,增加稳定性。提出一种新的具有自适应功能的自动增益控制技术,使得跨阻放大器在不同光输入功率下保持带宽不变,环路稳定,具有宽动态范围特性。研究结果表明:在误码率为10−10,传输速率为2.5 Gbit/s时,该前置放大器的接收光灵敏度高达−29 dB·m,输入最大光功率为2 dB·m,动态范围达31 dB·m;在1.8 V的电源电压下,芯片功耗为30 mW,芯片总面积为1×0.7 mm2。

光接收机;前置放大器;灵敏度

随着多媒体技术的发展和应用,高速率的数据传输要求通信系统的带宽越来越高,成本越来越低。光通信技术由于其具有低成本和高信道容量特性成为高速数据传输的首选方案。光接收机主要包括前置放大器(preamplifier)、限幅放大器(limiting amplifier,LA)和时钟恢复电路(clock and data recovery,CDR)等。光电二极管(photodiode,PD)监测光信号强度并将其转换为电流。前置放大器将电流信号转换为电压信号,并由限幅放大器放大电压信号至足够大,再输入时钟恢复电路。前置放大器的带宽和灵敏度等关键参数[1]决定了最大数据传输速率和信道损耗,因此,通常也决定了光通信系统的性能。近年来,人们研究了多种前置放大器电路,这些研究主要集中在2个方面:1) 提高前置放大器的带宽,例如电感峰化技术[2−4]、电容弱化技术[5−6]以及调节型共源共栅电路结构[7−9]等。电感峰化技术芯片面积大,并且会引起串扰。电容补偿技术会降低电压放大器的增益。调节型共源共栅结构虽然隔离了光电二极管的寄生电容,增大了电路的带宽,但其噪声性能比电压反馈型跨阻放大器的性能差。 2) 提高前置放大器的灵敏度和动态范围,例如噪声消除技术[10]和自动增益控制电路[11−12]。噪声消除技术增加了电路结构的复杂性。自动增益控制电路的设计则没有考虑输入光功率增大时前置放大器环路的稳定性变化。CMOS工艺具有成本低、功耗低的优点,本文作者基于CMOS工艺设计一种无电感的高灵敏度宽动态范围前置放大器。传统的3级推挽反相器构成的跨阻放大器具有噪声性能好的特性[13],但由于其内部包含3个极点,仅限于千兆及以下跨阻放大器电路[14]。针对此缺点,本文作者设计位于反馈环路中的虚零点,加强了环路的稳定性,将其工作速率提高至2.5 Gbit/s;提出一种新的具有自适应功能的自动增益控制技术,以增大前置放大器的输入动态范围,保持前置放大器在不同输入功率条件下环路的稳定性。

1 前置放大器结构设计

前置放大器芯片结构框图如图1所示,主要包括跨阻放大器(TIA)、单端转差分放大器(single-ended to differential-ended amplifier,S−D amp) 、输出缓冲电路 (driver)、峰值检测电路(peak−value detection,PVD)和直流消失调电路(DC offset cancellation,DOC)等。PD将不同功率的光信号转换为相应电流,跨阻放大器将电流信号转换为电压信号,并通过单端转差分放大器将其转换为差分信号。最后一级为输出缓冲电路,输出电阻为50 Ω。PVD检测前置放大器输出端口电压OP和ON,产生自动增益控制电压AGC。DOC保持前置放大器输入级的直流工作点稳定,输入输出电压相等。

图1 前置放大器结构框图

2 前置放大器电路设计

2.1 高灵敏度跨阻放大器设计

跨阻放大器电路如图2所示。光电二极管原型复杂,简化为寄生电容与理想电流源的并联。图2中,IN为流过光电二极管的电流,CIN包含光电二极管的寄生电容、TIA(transimpedance amplifier)输入管脚Bonding寄生电容、输入晶体管寄生电容等,它限制了电路的最大带宽。晶体管MN1,MN2,MN4,MP1,MP2和MP4构成3级推挽反相器,电阻F与电容F构成反馈电路。3级推挽反相器和反馈电路组成跨阻放大器,输出端口为OUT。第2级和第3级反相器输出节点增加了二极管连接方式连接的晶体管MN3,MP3和MP5,降低了节点阻抗,减小了密勒效应。晶体管MN5,MN6和MN7组成具有自适应功能的自动增益控制电路,提高了电路的输入动态范围。

不考虑补偿电容F的影响,在跨阻放大器电路输入端处,由基尔霍夫定律得:

图2 跨阻放大器电路

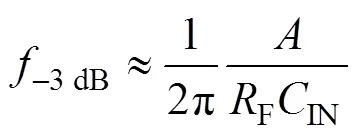

式中:OUT为跨阻放大器输出小信号电压;IN为PD注入电流;为3级推挽反相器的直流增益;F为跨阻;IN为输入节点寄生电容;为函数的自变量。式(1)表明:当>>1时,TIA的中频跨阻增益近似等于跨阻F。

式中:−3 dB为跨阻放大器的−3 dB带宽。在给定传输速率下,要求跨阻放大器−3 dB带宽最优值约为给定传输速率的0.7倍[15](对于2.5 Gbit/s,最佳设计−3 dB带宽约1.8 GHz)。由式(2)可知:对于给定的−3 dB带宽,跨阻RF的电阻决定了3级推挽反相器的直流增益设计指标。为了最小化主通道上寄生电容,提高跨阻放大器的速率,TIA电路主通道上所有晶体管采用最小栅长晶体管。负反馈环路通过跨阻RF提供直流偏置电压,因为没有电流输入,RF两端的电压差几乎为0 V,所以,TIA 的输入输出直流电压相等,为设计TIA 电路增加了1个重要的约束条件。经优化后的电路,第1级推挽反相器的沟道宽度最大,第2级与第3级反相器沟道宽度较小,且两者相等。

对于1个合理的跨阻放大器设计,跨阻放大器的主要噪声是跨阻RF噪声和放大器噪声。由于3级推挽反相器具有高增益的特性,因此,放大器噪声主要取决于第1级输入晶体管的噪声。晶体管的闪烁噪声仅仅在低频时起主要作用,因此,可以忽略不计,可得

式中:为等效输入参考电流噪声密度;k为玻尔兹曼常数;T为温度;gm1为输入级等效跨导。由式(3)可知:输入跨导gm1越大,反馈电阻RF越大,跨阻放大器的等效输入噪声电流越小。3级推挽反相器结构简单,不需要额外的偏置电路,对于给定电流,能提供最大跨导,等效跨导为PMOS和NMOS管跨导的总和。而且对于增益带宽积大于500 MHz的工艺,采用3级等效推挽反相器级联的跨阻放大器等效输入噪声电流最小[16],从而具有最优的噪声性能。增大跨阻RF也可以减小跨阻放大器的等效输入噪声电流,但根据式(2),在保持跨阻放大器带宽不变的前提下,增大跨阻RF需要增加3级推挽反相器的增益A。3级推挽反相器增益A增加引起主极点下降,从而降低环路的稳定性。因此,噪声性能与放大器的负反馈环路稳定性应进行严格折中。优化后的跨阻放大器等效噪声电流密度仿真结果如图3所示。在跨阻放大器的−3 dB带宽范围内,跨阻放大器最小输入噪声电流密度仅为2.2 pA/Hz1/2,平均等效输入噪声电流密度仅为5.4 pA/Hz1/2。

2.2 带宽与稳定性分析

由于3级推挽反相器内部包含3个极点,限制了带宽的提高。二极管连接方式的晶体管MN3,MP3和MP5降低了该节点的输出阻抗,提高了3级推挽反相器的第2级和第3级输出节点的极点频率,使其远远大于第1级输出节点的极点频率和环路−3 dB带宽频率。3级推挽反相器第1级输出节点成为主极点,设其拉普拉斯传输函数为

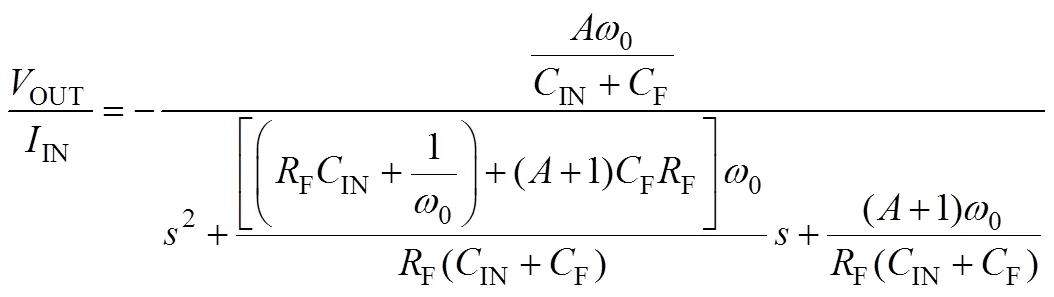

式中:0为放大器的主极点。当放大器输入小信号电流时,晶体管MN5,MN6和MN7关闭。不考虑补偿电容F的影响,跨阻放大器反馈系数为

将式(4)和(5)代入式(6)得

3级推挽反相器主极点0必须大于2/(FIN),跨阻放大器反馈环路才能稳定。由式(2)可知0限制了TIA工作速率的提高。本文提出一种新的补偿方案,不使用电感,在保持跨阻放大器稳定性的前提下,能够最大限度地提高跨阻放大器的工作速率。补偿电容F与反馈电阻F并联,不存在于系统传输函数中,仅存在于反馈网络中。考虑构成虚零点的补偿电容F影响,据式(5),有

补偿电容F构成了位于反馈系数中的零点,称为虚零点。显然,虚零点减小了反馈系数的相位偏移。将式(10)代入式(6),可得

考虑到F<<IN,可得

1—零点补偿;2—无零点补偿。

图4 跨阻放大器的频率响应

Fig. 4 Frequency response of TIA

2.3 自动控制增益设计

如图1所示,自动增益控制电压AGC由PVD根据信号强度产生,依据AGC可以将输入光电流信号分为“非激活”区域、“激活”区域。在“非激活”区域,光电流信号小,AGC保持在最小值,MN5,MN6和MN7处于截止状态,跨阻放大器保持线性工作,输出电压幅度与输入电流信号呈线性关系。而在“激活”区域,输入电流较大,为了避免跨阻放大器进入饱和状态,自动增益控制被激活,AGC变大,MN5,MN6和MN7进入线性区,等效为随AGC增大而变小的可变电阻,实现了大信号时的自动增益控制,保证在“激活”区域,跨阻放大器仍然保持线性工作。在“激活”区域,MN5,MN6和MN7开启,此时,IN并非全部流过跨阻F,其中有一部分交流电流1流过MN5,且AGC越大,则1所占的比例越大。同时,MN5,MN6和MN7也降低了3级推挽反相器总增益。当输入的光功率增加时,式(11)变为

式中:为由反馈电压AGC决定的常数,0≤≤1;ACT为3级推挽反相器在“激活”区域的电压增益。由式(13)可见,等效跨阻变为原来的(1−)倍。不考虑晶体管MN6和MN7的影响,3级推挽反相器构成的增益为

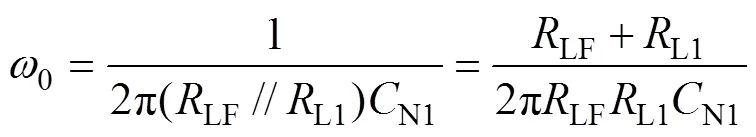

式中:m1,m2和m3分别为第1级、第2级和第3级反相器的等效跨导;L1,L2和L3分别为第1级、第2级和第3级反相器的输出节点电阻;LF为MN5等效线性区电阻,阻值受控制电压AGC控制。放大器的主极点在第一级输出节点,大小为

式中:N1为第1级反相器输出节点的等效电容。

即为1个常数,设其为常数,则有

反馈控制电压AGC/V:1—0.9;2—1.2;3—1.5。

图5 跨阻放大器在不同自动增益控制电压下的频率响应

Fig. 5 Frequency response of TIA at different auto-gain control voltages

3 测试结果

前置放大器采用0.18 μm RF CMOS 工艺设计并流片。芯片版图如图6所示,面积为1×0.7 mm2。前置放大器测试时将与光电二极管封装在一起,通过接收光信号完成测试。光电二极管寄生电容为0.65 pF,转换效率为0.9 A/W。

图6 前置放大器版图

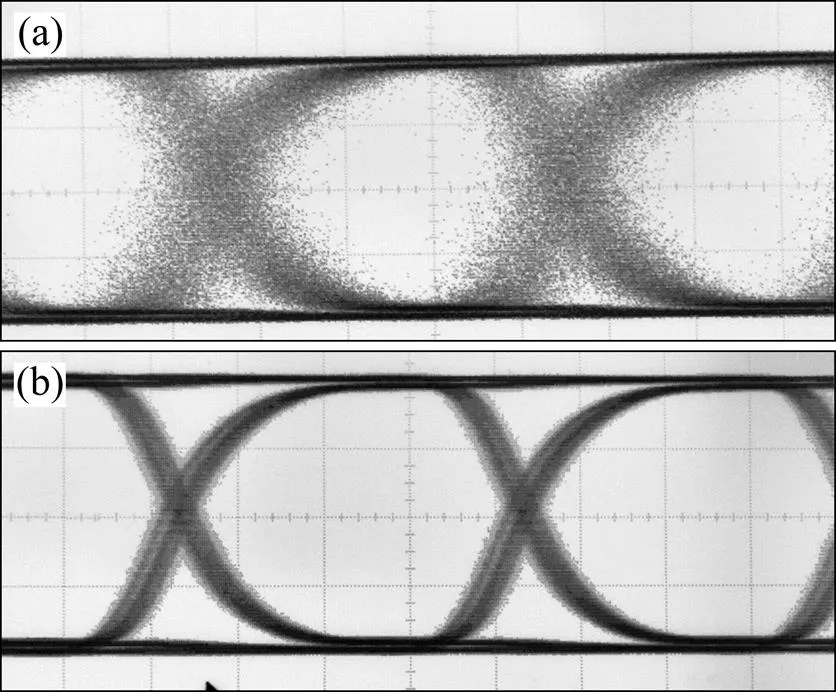

前置放大器的眼图测试通过Advanstest D3186函数信号发生器和Agilent DCA 86100A眼图仪完成测试。函数信号发生器产生速率为2.5 Gbit/s、周期为210−1的伪随机二进制码(PRBS),并通过光模块发射消光比为12 dB的输出激光信号,激光信号经过光衰减器后作为前置放大器的输入。图7所示为前置放大器在−29 dB·m和2 dB·m输入光功率下的输出眼图,眼图清晰,输出电压摆幅为380 mV。

前置放大器灵敏度测试采用Antrisu的MP1763C和MP1764C 比特误差率测试系统。在前置放大器的输入端输入消光比为12 dB、速率为2.5 Gbit/s、周期为210−1伪随机码流测试结果如图8所示。对于常用的数字通信系统,比特误差率一般要求为10−10。前置放大器在此比特误差率的要求下光灵敏度为 −29 dB·m。

该前置放大器的性能见表1。从表1可见:经过本文的优化设计,前置放大器在保持带宽的前提下,有效改善了噪声性能。通过改善噪声性能,在实际测试结果中,前置放大器的灵敏度为−29 dB·m。

输入光功率/(dB∙m):(a) −29;(b) 2

图8 不同光输入功率下的比特误码率

表1 前置放大器性能比较

4 结论

1) 基于0.18 μm RF CMOS 工艺设计了一种应用于光接收机的无电感前置放大器。

2) 采用零点补偿技术,将3级推挽方向器结构的跨阻放大器工作速率提高至2.5 Gbit/s。提出一种具有自适应功能的自动增益控制电路,使前置放大器在不同输入光功率条件下环路保持稳定。

3) 在传输速率为2.5 Gbit/s、误码率为10−10时,前置放大器的光灵敏度达−29 dB·m,输入范围达 31 dB·m。该前置放大器可应用于光接收机之中。

[1] 朱恩, 王志功, 冯军, 等. 2.5~40 Gb/s光收发关键器件芯片技术[J]. 中国有色金属学报, 2004, 14(S1): 369−380. ZHU En, WANG Zhigong, FENG Jun, et al. Transceiver integrated circuit technology for 2.5−40 Gb/s optical-fiber communication[J]. Transactions of Nonferrous Metals Society of China, 2004, 14(S1): 369−380.

[2] JIN Junde, HSU S S H. A 40 Gb/s transimpedance amplifier in 0.18 μm CMOS technology[J]. IEEE Journal of Solid-State Circuits, 2008, 43(6): 1449−1457.

[3] WALLING J S, SHEKHAR S, ALLSTOT D J. Wideband CMOS amplifier design: time-domain considerations[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2008, 55(7): 1781−1793.

[4] LU Zhenghao, YEO K S, MA Jianguo, et al. Broad-band design techniques for transimpedance amplifiers[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2007, 54(3): 590−600.

[5] CHIEN F T, CHAN Y J. Bandwidth enhancement of transimpedance amplifier by a capacitive-peaking design[J]. IEEE Journal of Solid-State Circuits, 1999, 34(8): 1167−1170.

[6] HUANG Beiju, ZHANG Xu, CHEN Hongda. 1 Gb/s zero-pole cancellation CMOS transimpedance amplifier for Gigabit Ethernet applications[J]. Journal of Semiconductors, 2009, 30(10): 105005.

[7] KIM Y H, JUNG E S, LEE S S. Bandwidth enhancement technique for CMOS RGC transimpedance amplifier[J]. Electronics Letters, 2014, 50(12): 882−884.

[8] CHEN Yingmei, WANG Zhigong, FAN Xiangning, et al. A 38 Gb/s to 43 Gb/s monolithic optical receiver in 65 nm CMOS technology[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2013, 60(12): 3173−3181.

[9] XU Hui, FENG Jun, LI Quan, et al. A 3.125 Gb/s inductorless transimpedance amplifier for optical communication in 0.35 μm CMOS[J]. Journal of Semiconductors, 2011, 32(10): 105003.

[10] ATEF M, ZIMMERMANN H. 2.5 Gbit/s transimpedance amplifier using noise cancelling for optical receivers[C]//2012 IEEE International Symposium on Circuits and Systems. Seoul: IEEE, 2012: 1740−1743.

[11] LIU Lianxi, ZHAO Jiao, EN Yunfei, et al. A high gain wide dynamic range transimpedance amplifier for optical receivers[J]. Journal of Semiconductors, 2014, 35(1): 015001.

[12] TAGHAVI M H, BELOSTOTSKI L, HASLETT J W. A CMOS low-power cross-coupled immittance-converter transimpedance amplifier[J]. IEEE Microwave & Wireless Components Letters, 2015, 25(6): 403−405.

[13] del POZO J M G, CELMA S, SANZ M T, et al. CMOS tunable TIA for 1.25 Gbit/s optical gigabit ethernet[J]. Electronics Letters, 2007, 43(23): 1303−1305.

[14] SACKINGER E. Broadband circuits for optical fiber communication[M]. New York: John Wiley & Sons, 2005: 1−50.

[15] PIETRUSZYNSKI D M, STEININGER J M, SWANSON E J. A 50 Mbit/s CMOS monolithic optical receiver[J]. IEEE Journal of Solid-State Circuits, 1988, 23(6): 1426−1433.

[16] JUNG H Y, LEE J M, CHOI W Y. A high-speed CMOS integrated optical receiver with an under-damped TIA[J]. IEEE Photonics Technology Letters, 2015, 27(13): 1367−1370.

(编辑 陈灿华)

2.5 Gbit/s inductorless preamplifier with high sensitivity and wide dynamic range

ZHU Tiezhu1, 2, MO Taishan1, 3, YE Tianchun1, 2

(1. Institute of Microelectronics, Chinese Academy of Sciences, Beijing 100029, China;2. Hangzhou Zhongke Microelectronics Co. Ltd., Hangzhou 310053, China;3. Jiaxing Heroic Technology Co. Ltd., Jiaxing 314001, China)

An inductorless 2.5 Gbit/s preamplifier was designed for the application of optical receivers in passive optical network and fabricated in a 0.18 μm RF CMOS process. The preamplifer consisted of a transimpedance amplifier, a single-ended Ti differential ended amplifier and an output driver. The transimpedance amplifier was based on a three-stage push-pull inverter structure. The special configuration allows for high gain and low noise performance. Phantom zeros technique was analyzed and employed to improve the bandwidth and ensure the stability of the TIA. To achieve a wide dynamic range, an automatic gain control technique with self-adaptive function was proposed to keep the bandwidth constant and stabilize the feedback network. The results show that the optical sensitivity is −29 dB·m and the maximum input optical power is 2 dB·m for 2.5 Gbit/s operation with a bit error rate of 10−10. The dynamic range is 31 dB·m.The chip consumes about 30 mW from a single 1.8 V supply. The chip area is 1×0.7 mm2.

optical receiver; preamplifier; sensitivity

10.11817/j.issn.1672−7207.2017.08.014

TN433

A

1672−7207(2017)08−2073−06

2016−08−08;

2016−10−12

国家科技重大专项(2013ZX02310);中国第二代卫星导航系统重大专项(GFZX030302020205)(Project(2013ZX02310) supported by the Major Project of National Science and Technology; Project(GFZX030302020205) supported by the Major Project of the Second Generation Satellite Navigation System of China)

朱铁柱,博士研究生,从事数模混合集成电路研究与设计;E-mail:jinmulu@163.com