一种基于维特比解码的超高频RFID读写器解码器设计

2017-10-13王俊宇

王 贺,王俊宇

(复旦大学 专用集成电路与系统国家重点实验室,上海 201203)

一种基于维特比解码的超高频RFID读写器解码器设计

王 贺,王俊宇

(复旦大学 专用集成电路与系统国家重点实验室,上海 201203)

车辆管理和生产管理等应用对超高频射频识别(UHF RFID)读写器的灵敏度有很高的要求.读写器数字基带解码器作为接收链路的关键环节,其误码率(BER)性能直接影响读写器的接收灵敏度.维特比解码是一种广泛应用于卷积码的解码算法,利用卷积码中码元间的相互联系实现纠错解码.本文首次将维特比解码移植应用于UHF RFID系统中的FM0编码的解码算法中.该解码器利用FM0编码的记忆性,结合维特比解码的纠错能力来降低误码率.仿真结果表明,该解码器在信噪比(SNR)为7.3dB的条件下,可以将误码率降至10-5.相对于最优接收机结构,该解码算法有2.5dB的信噪比优势.

射频识别; 读写器; 维特比; 解码器

射频识别(Radio Frequency Identification, RFID)是一种非接触式自动身份识别和信息获取技术(Auto Identification and Data Collection, AIDC).在RFID系统中,标签被附着在物品上,通过固定或手持式的读写器对标签携带的物品信息进行识别和读取,读写器和标签之间通过射频信号进行通信.该技术具有通信距离远、稳定性高、设备使用寿命长、损耗小等优点,广泛应用于物品定位、医疗、物流管理等领域中[1-3].近年来,随着RFID技术的快速发展,尤其是超高频(Ultra-High Frequency, UHF)RFID技术的不断推广,对于读写器的灵敏度要求也不断提高.读写器数字基带解码器的性能对其灵敏度有直接的影响,在同等接收信号信噪比的条件下,解码器的误码率(Bit Error Rate, BER)越低,读写器灵敏度则越高.

在UHF RFID读写器数字基带解码器设计上,前人采用的算法可分为基于跳变沿检测和基于最优接收机结构2种.

在基于跳变沿检测的算法中,文献[4-5]中作者将接收到的信号整形成矩形波,再对矩形波进行过零跳变检测.通过跳变沿之间的时间间隔长度对比来进行解码.在文献[6]中,作者将FM0编码的码元符号重新分类成4种具有不同占空比的基本波形,将接收信号整形成矩形波后,用自定义的基本码元波形进行解码.然而在低信噪比环境下,较强的幅度噪声会导致跳变沿位置产生偏移,从而转化为相位噪声.该相位噪声对于跳变沿之间的时间间隔长度以及码元符号的占空比都会造成严重影响,进而导致解码算法误码率提高.因此该类算法对于强噪声干扰的抵抗能力较弱.

在基于最优接收机结构的算法中,文献[7]提出利用匹配滤波器对接收信号的每个码元进行相关操作,根据相关值的大小关系进行解码判决.文献中论述并证明了基于匹配滤波器的解码算法相对于基于跳变沿检测的解码算法在性能上的优势.在文献[8]中,同样提出了基于相关操作的解码算法,但是在其解码判定时,仍然根据码元相关值之间的大小关系进行解码判决.这种判决方式忽略了FM0编码中相邻码元间的编码联系[9],即FM0编码的记忆性,且只利用相关值之间的大小关系而不是相关值的数值本身,因而未能充分利用接收信号中携带的全部信息,在解码性能上还有优化的空间.

维特比解码是一种广泛应用于卷积码的解码方法,其特点是能够利用编码时不同码元之间的约束关系,通过接收到的多个后方码元的波形共同确定前方某个码元的最大似然译码结果,从而纠正前方码元解码时可能产生的解码错误.本论文提出了一种基于维特比解码的RFID基带解码器设计方法,充分利用了FM0编码的记忆性以及接收信号中携带的全部信息,可有效地实现对FM0编码的前向纠错解码,与同类解码器相比,信噪比性能提升2.5dB.

1 解码器算法设计

1.1FM0编码的编码规则及特性

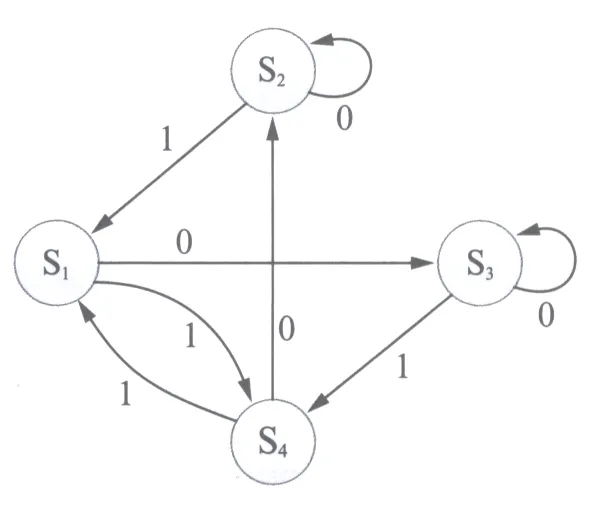

FM0是一种双相间空编码,其对于数据0和数据1的基本符号波形相互正交,这一特性使得当应用匹配滤波器对码元进行相关操作时,不同数据的编码后码元相关值差距明显.图1所示为FM0编码的4种基本波形,其中数据0和数据1各有2种基本波形且互为反向.在编码过程中,将这4种基本波形视为4个编码状态S1~S4,其状态跳转规则如图2所示.由该状态图可以得知,对于任意2个相邻比特,其编码后波形在码元交界处必须进行一次相位翻转.因此每一个数据比特编码后的码元波形必然受前一个码元的影响.

图1 FM0编码的基本波形符号Fig.1 Basic waveforms of FM0 code

图2 FM0编码状态跳转图Fig.2 State transition diagram of FM0 code

1.2维特比算法在FM0解码中的应用分析

维特比算法是一种应用于卷积码解码的最大似然解码算法.在卷积码编码中,每一个k比特长的输入序列对应一个n比特长的输出序列,即对于单个比特信息来说,其编码后的波形受附近k-1个比特信息的影响,该特性为卷积码的有限记忆性.维特比算法则利用此有限记忆性,通过当前码元之后多个码元的波形判定当前码元的最大似然解码结果.

由上一节的分析可知,FM0编码的相邻码元波形之间存在着制约关系,通过与卷积码的类比,可以发现在原理上维特比算法同样能够优化FM0解码算法的性能.

在实际算法实现中,由于FM0编码的每个基本波形只包括2个单位电平,组成(1,1),(1,0),(0,1)或(0,0)4种基本波形,如果直接采用卷积码解码中衡量接收码元与理想码元之间距离的方式,即仅依靠2个单位电平的判决结果进行分支度量的话,其分支度量精度则只有两位,无法充分发挥维特比解码算法的纠错能力.因此,本文中将采用对每个接收到的码元与理想基本波形进行相关操作,再将获得的相关值进行多位量化并与理想量化值做差的方式来获得更高精度的分支度量结果.在该分支度量结果的基础上,便可将维特比解码算法移植应用到FM0解码中.

1.3维特比解码器在RFID读写器中的作用

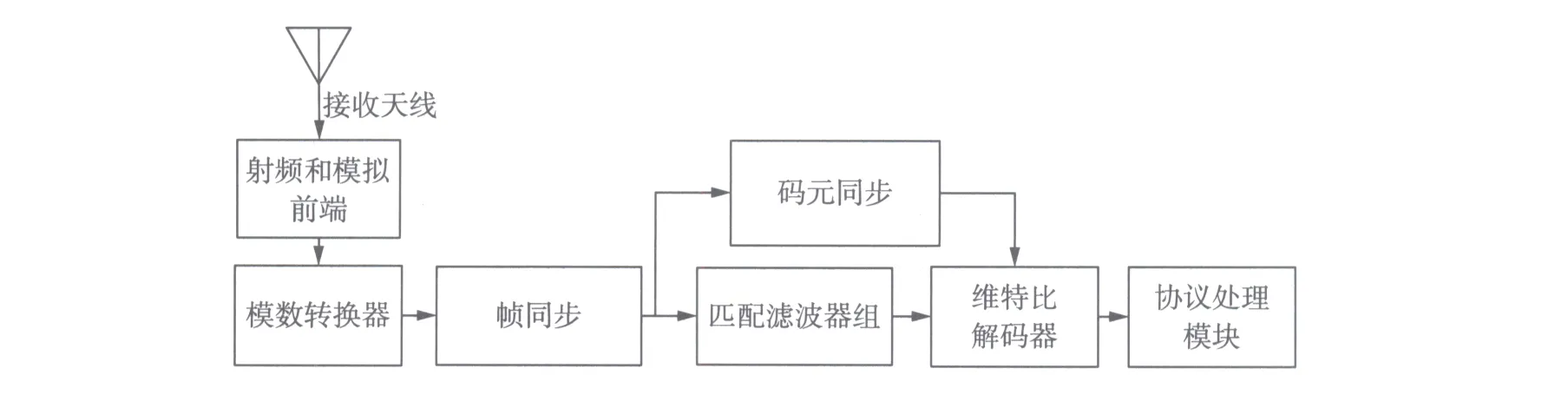

RFID读写器接收机的架构以及维特比解码器在其中的作用如图3所示.标签返回的信号被天线接收后,经过射频和模拟前端电路的处理变为模拟基带信号.该信号由模数转换器转换为数字信号后,进入数字基带.在数字基带中,帧同步模块负责检测帧头编码序列并确定数据编码段的起始位置.码元同步模块负责确定每个码元的边界并在码元结束时向维特比解码器提供解码使能信号.匹配滤波器组负责向维特比解码器提供分支度量所需的相关值.维特比解码器在解码使能信号的控制下,根据每个码元与理想基本波形的相关值进行解码操作.协议处理模块负责根据解码输出以及标准协议的规定,对该标签返回的信号做出响应.

图3 RFID读写器接收机架构Fig.3 Structure of the RFID reader receiver

1.4维特比解码器算法流程

为了阐述维特比解码算法应用在FM0解码时的算法流程,将FM0编码的状态跳转图转化为图4所示的状态网格表.维特比算法将沿着该状态网格表执行.在图4中,Si(i=1,2,3,4)代表4种基本波形状态,实线代表因接收数据1引起的状态跳转,虚线代表因接收数据0引起的状态跳转.参数n代表接收到的码元的序号,Di(n)(i=1,2,3,4)代表第n个码元相对于理想基本波形Si的欧几里得距离,Ai(n)(i=1,2,3,4)代表第n个码元处理后状态Si的累积距离.

图4 FM0编码的状态网格表Fig.4 Trellis diagram of FM0 encoding

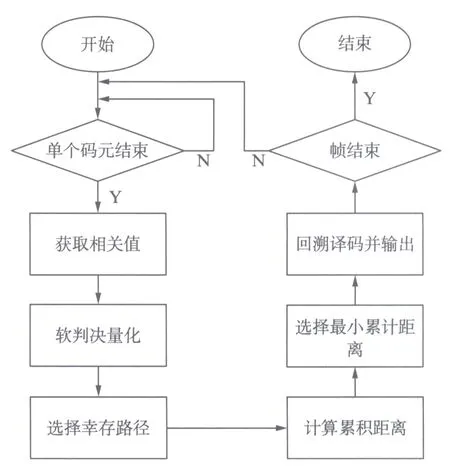

在该状态网格表的基础上,维特比算法将按照图5所示流程进行.当解码器接收到解码使能信号时,代表单个码元接收结束,解码算法将按照以下6个步骤进行:

图5 维特比算法流程Fig.5 Workflow of the Viterbi algorithm

1) 首先,解码器将从匹配滤波器组中获得当前码元与4种基本波形的相关值.

2) 然后,将该相关值进行4位软判决量化,量化的最大值对应的相关值为理想波形与本地基本波形匹配得到的相关值.将量化后的码元相关值与理想相关值做差,便得到了该码元量化后的欧几里得距离,即为网格表中的Di(n).

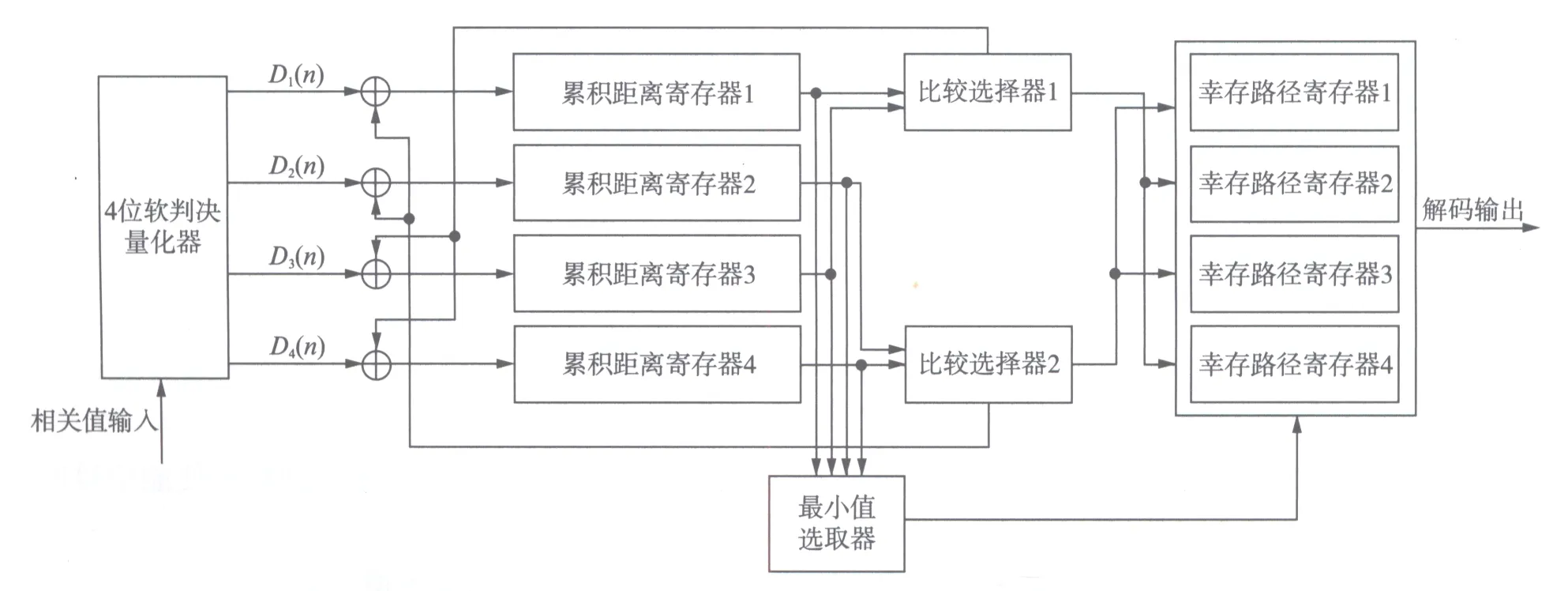

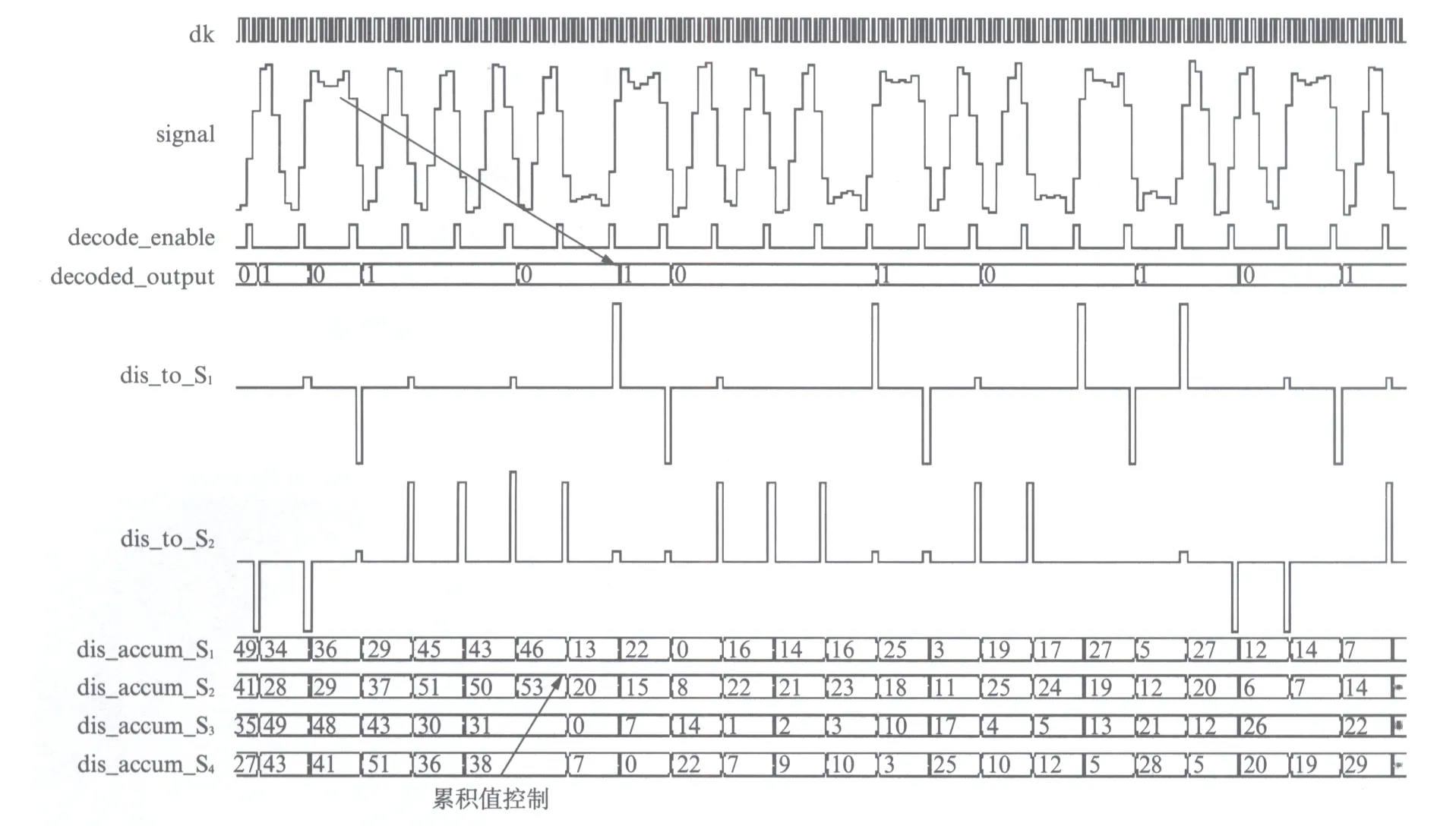

3) 对于每一种编码状态Si,都有2条通向该状态的路径,比较这2条路径的上游状态的累积距离,选取累积距离较小的一条路径作为该状态的幸存路径.例如,在n=3时,对于状态S1来说,如果A2(2) 4) 确定幸存路径之后,将该路径的上游状态的累积距离与当前码元的欧几里得距离相加,得到当前处理状态的累积距离.对于上一个例子来说,即将A2(2)与D1(3)相加作为n=3时S1的累积距离. 5) 在计算完成每一种编码状态的累积距离后,从中选取累积距离最小的状态. 6) 最后,沿着该累积距离最小的状态的幸存路径开始固定长度的回溯译码,回溯过程中,每经过一条实线说明该码元的译码结果为1,每经过一条虚线说明该码元的译码结果为0.当回溯完成时最后一个码元的译码输出即为该码元的最大似然译码结果,解码器将该结果输出给协议处理模块. 对于约束长度为2的卷积码来说,回溯长度为5时即可获得理想的解码精度[10],该结论对于FM0编码同样适用.如果当前处理码元是一帧信号的最后一个码元,则回溯过程中的所有译码结果将作为最后6个码元的译码结果同时输出. 在解码过程中,如果某个码元受到了较强噪声的影响,导致其与正确的理想基本波形的相关值小于与错误的理想基本波形的相关值,此时仅仅根据两种相关值的大小关系进行解码判决就会产生误码.但是在维特比解码算法中,虽然该码元相对于理想基本波形的欧几里得距离较大,但是如果其后面接收到的数个码元没有被强噪声干扰,依然可以凭借后面接收的码元较小的欧几里得距离获得正确的幸存路径,从而实现前向纠错解码的功能. 2.1维特比解码器电路结构 为了实现第一节阐述的维特比解码算法,本文设计的解码器电路结构如图6所示.从子模块划分上来看,该电路分为软判决量化器、累积距离存储器、比较选择器、最小值选择器、幸存路径寄存器. 图6 维特比解码器电路结构Fig.6 Hardware architecture of the Viterbi decoder 软判决量化器负责对从匹配滤波器组获取的相关值进行4位量化,获得当前码元与4种理想基本波形之间的欧几里得距离. 累积距离存储器负责存储属于每个FM0编码状态的累积距离值,该累积值在每处理完一个码元后会得到更新,更新值取决于比较选择器的选择结果.比较选择器选取两个输入值中的较小值与量化器产生的相应欧几里得距离相加,即为该编码状态的累积距离更新值.在实际设计过程中,随着接收码元个数的增加,累积距离将不断的增长,其累加操作的位数也将不断增加.为了避免当帧长度较大时累加操作的硬件消耗过大,电路中设置了幅值控制逻辑,即当4个编码状态的累积距离中的最小值达到某阈值时,将所有累积距离值减去该阈值.这样既能将累积距离值控制在一定范围内,又不会改变各个累积距离值之间的相对关系. 最小值选取模块将从更新后的4个累积距离中选取最小值,并将其状态序号输出给幸存路径寄存模块,用来控制解码器的解码输出. 幸存路径寄存模块既负责存储每个编码状态对应的一定长度的幸存路径,也负责根据最小值选取模块提供的4个累积距离中最小值的序号产生解码输出.该模块中设有4个分别属于4种编码状态的长度为6的幸存路径寄存器,其中存储了以该状态为起点,回溯深度为5的幸存路径.每当一个码元接收完成,幸存路径将被更新,获得最小累积距离值的编码状态对应的幸存路径寄存器所移出的解码结果将作为解码器的解码输出. 2.2电路硬件实现 图7 维特比解码器版图实现Fig.7 Layout of the Viterbi decoder 本文所设计的维特比解码器在SMIC 0.13μm工艺下由Design Complier进行了逻辑综合.该解码器的硬件实现参数为时钟频率5.12MHz,逻辑综合后面积为20486μm2,等效门数4.2kEGs,功耗6.53μW.与文献[11]中实现的整个数字基带对比,在相同工艺下,该解码器所消耗的硬件面积仅为整个数字基带面积的4.9%.考虑到该解码器能够带来的解码性能提升,该解码器在硬件消耗上是高效的.设计中的时钟频率设定为协议规定的标签返回信号最高数据率的8倍,在此设定下,每个码元将包含8个采样点供解码器分析处理. 该电路在SMIC 0.13μm工艺下通过Astro后端设计软件进行芯片实现.其版图照片如图7所示,版图中单元面积为21000μm2,核心面积为22100μm2,核心利用率为95%.该版图通过了相应的Layout Versus Schematic(LVS)和Design Rule Checking(DRC)验证. 2.3电路功能验证 对于电路的解码功能验证仿真在Modelsim软件平台上进行,仿真图像如图8所示.图中所示测试信号为加入了高斯白噪声的FM0编码信号.图中第3行为外部输入的解码使能信号,第4行为解码输出.如图中上方箭头所示,由于解码器的回溯深度为5,所以相对于输入信号,解码输出有5个码元的解码延迟, 第5~6行分别为当前码元相对于编码状态S1(1,1)、S2(1,0)的欧几里得距离,从图中可以看出,接收码元波形与理想基本波形差距越大时,其欧几里得距离也越大. 第7~10行分别为4种状态的累积距离值,从图中可以看出累积距离呈上升状态,当累积距离最小值超过阈值时,所有累积值将同时减小,如图中下方箭头所示. 从仿真结果可以看出,该解码器在功能上实现了维特比解码算法流程,且解码结果正确. 图8 解码器功能验证仿真图Fig.8 Function verification waveforms of the Viterbi decoder 为了衡量该维特比解码器的解码性能,在Matlab软件平台上进行了误码率仿真.在仿真中通过在理想FM0编码序列中加入可控强度的高斯白噪声,获得一定信噪比下的测试信号,解码该测试信号并统计相应信噪比下的误码率性能. 仿真结果及性能对比如图9所示.按照图中曲线标注的顺序,第1条和第3条曲线对应的解码算法基于跳变检测实现,但是在跳变检测前采用的波形整形算法不同.第2条和第4条曲线采用最优接收机结构的解码算法,其中第2条曲线采用的采样率较高因而性能较好.第5条曲线采用维特比解码算法获得,为了便于对比,该曲线与第4条曲线采用相同的采样率.从图9中可以看出,采用最优接收机结构的算法性能优于基于跳变检测的算法,同时维特比算法的性能优于最优接收机结构,这与理论分析的结果相符合.本文采用的解码算法能够在信噪比为7.3dB时将误码率控制在10-5,相比于最优接收机结构,达到相同误码率时所需的信噪比整体低2.5dB. 图9 在不同信噪比下误码率性能仿真结果Fig.9 Simulation results of the BBER with different RSNR 本文设计并实现了一种应用于UHF RFID读写器数字基带中的维特比解码器.该解码器将维特比解码方法移植应用于FM0编码的解码算法中,利用FM0编码的记忆性,实现前向纠错解码从而降低误码率.该解码器在信噪比为7.3dB的条件下,可以将误码率控制在10-5,相对于最优接收机结构有2.5dB的信噪比优势. [1] JIAN M, TAKAHASHI Y. Low cost design of HF-band RFID system for mobile robot self-localization based on multiple readers and tags [C]∥International Conference on Robotics and Biomimetics(ROBIO), Zhuhai, China: IEEE Press, 2015: 194-199. [2] JAYAWARDANA D, KHARKOVSKY S, LIYANAPATHIRANA R. Measurement system with a RFID tag antenna mounted on structural members for infrastructure health monitoring [C]∥Instrumentation and Measurement Technology Conference(IMTC). Pisa, Italy: IEEE Press, 2015: 7-12. [3] PAYDAR S, ENDUT I R, LAJEVARDI A. Environmental determinants of RFID adoption in retail supply chain, a binary logistic regression analysis [C]∥RFID-Technologies and Applications(RFID-TA). Johor Bahru, Malaysia: IEEE Press, 2013: 1-6. [4] ZHANG F N, WANG X A, YONG S S,etal. A multi-bit encoder and FM0/Miller decoder design for UHF RFID reader digital baseband [C]∥Solid-State and Integrated Circuit Technology(ICSICT). Xi'an, China: IEEE Press, 2012: 1-3. [5] ANGERER C, RUPP M. Advanced synchronization and decoding in RFID reader receivers [C]∥Radio and Wireless Symposium(RWS), San Diego, USA: IEEE Press, 2009: 59-62. [6] BAUTISTA N F B, MARCIANO J J S. Enhanced FM0 decoder for UHF passive RFID readers using duty cycle estimations [C]∥RFID-Technologies and Applications(RFID-TA).Sitges, Spain: IEEE Press, 2011: 306-312. [7] LUO X, SUNG HO C. A RFID decoder using a matched filter for compensation of the frequency variation [C]∥Wireless Communications, Networking and Mobile Computing(WiCom). Beijing, China: IEEE Press, 2009: 1-5. [8] WEI P, LI B, YANG Y Q,etal. Synchronization with timing recovery loop in UHF RFID reader receivers [C]∥International Conference Electronics, Circuits, and Systems(ICECS). Athens, Greece: IEEE Press, 2010: 1148-1151. [9] EPCTMglobal. EPCTMRadio-frequency identity protocols generation-2 UHF RFID protocol for communications at 860 MHz-960 MHz Version 2.0.0[D/OL].(2008-10-23)[2016-05-06]. http:∥www.gs1.org/sites/default/files/docs/epc/uhfc1g2_2_0_0_st-andard_20131101.pdf. [10] VITERBI A, STIFFLER J. Performance of N-orthogonal codes(Corresponding.) [J].IEEETransactionsonInformationTheory, 1967,13(3): 521-522. [11] GUO Z Y, WANG X A, YONG S S,etal. Design and realization of UHF RFID reader digital baseband [C]∥Solid-State and Integrated Circuit Technology(ICSICT). Guilin, China: IEEE Press, 2014: 1-3. Abstract: The applications on the vehicle management and the production management of the ultra-high frequency(UHF) radio frequency identification(RFID) system have high requirement on the sensitivity of the reader. The decoder in the digital baseband is a crucial part of the receive link, the bit error rate(BER) of which has a direct influence on the sensitivity of the reader. The Viterbi decoding is a decoding algorithm widely used in the convolutional code decoding, taking advantage of the interaction of different encoded bits and realizing the forward error correcting. As far as what we learnt from the literature, it is the first time that the Viterbi decoding algorithm is applied to the FM0 decoding in the UHF RFID system. Based on the error correcting ability of the Viterbi decoding, the decoder decreases the BER by exploiting the memory property of the FM0 code. Simulation results show that the Viterbi decoder achieves a BER of 10-5under the Singnal to Noise Ratio(SNR) of 7.3 dB. Compared with the traditional optimal receiver structure, the Viterbi decoder has an SNR benefit of 2.5 dB. Keywords: radio frequency identification; reader; Viterbi; decoder ADecoderDesignforUHFRFIDReaderBasedontheViterbiDecodingAlgorithm WANG He, WANG Junyu (StateKeyLaboratoryofASIC&System,FudanUniversity,Shanghai201203,China) TN402 A 0427-7104(2017)03-0321-07 2016-06-06 国家科技支撑计划(2015BAK36B01) 王 贺(1988—),男,硕士研究生;王俊宇,男,教授,通信联系人,E-mail: junyuwang@fudan.edu.cn.2 解码器电路实现

3 性能仿真与分析

4 结 论