一种全数字正交发射机中数字前端电路的设计

2017-10-13沈逸磊张宏广洪志良

叶 峰,沈逸磊,薛 盼,张宏广,洪志良

(复旦大学 专用集成电路与系统国家重点实验室,上海 201203)

一种全数字正交发射机中数字前端电路的设计

叶 峰,沈逸磊,薛 盼,张宏广,洪志良

(复旦大学 专用集成电路与系统国家重点实验室,上海 201203)

本文设计了一种应用于全数字正交发射机的数字前端电路(DFE).DFE主要由I/Q 2路插值倍数为24的高速升采样数字滤波器构成,将基带带宽为20MHz的信号从100MHz升采样至2.4GHz,同时能够有效滤除镜像信号.其中第1级滤波器采用转置结构实现,并通过对过渡带的优化而将滤波器阶数从41降低至18.后3级半带滤波器则通过结构的变换,巧妙地将插值与滤波器过程结合起来,降低了部分单元的工作频率,优化了功耗;另外,在高频部分,为了满足时序要求,对关键路径进行流水线处理,并使用低阈值管提高工作频率.此外,在DFE中还增加了低功耗的串行外设接口(SPI)可配置的预失真查找表,从而实现数字预失真(DPD)的功能,并通过对称性将查找表存储量优化17×17.DFE的总体版图面积为0.34mm2,包括时钟分频模块在内的总功耗估算为34.8mW,其中数字预失真表部分的功耗为3.5mW.仿真结果表明,本文带有预失真查找表的DFE能够将发射机的误差矢量幅度(EVM)从31.6%降低至3.26%.

数字前端; 插值滤波器; 数字预失真; 误差矢量幅度

随着经济社会的快速发展,信息化脚步的加快,无线通信技术已经开始广泛地应用于人们生产生活的各个方面.而作为通信系统的关键模块,发射机则面临更高的设计要求.CMOS工艺的发展为数字电路带来了更多优势,与传统的模拟发射机相比,数字发射机可以充分发挥数字电路按比例缩小的优点,减少芯片面积和功耗.而且采用数字电路容易集成复杂的算法,以替代复杂的模拟元件,并且具有更好的灵活性[1-3],同时可以降低发射机对工艺的敏感度.因而全数字的发射机架构在近几年的研究中成为一大热点.

随着发射机的数字化,发射机中数字前端部分集成的功能在不断增加,设计难度也在不断增大.由于发射机的载波频率一般都在GHz级别,这意味着数字前端电路(Digital-Front-End, DFE)的工作频率也可能达到GHz级.另外随着频分复用等更高效的发射机带宽调制技术的发展,数字前端电路对带外噪声(Out-of-Band-Noise)的要求也越来越高[4].对于非线性全数字发射机而言,数字前端在实现所需的性能要求之外,还要求能够尽量节省面积,便于片上集成,并尽量降低功耗[5-6].

同时,开关功放(Digital Power Amplifier, DPA)同线性功放一样存在非线性效应[4].过去的功放线性化技术主要包括功率回退、包络消除与恢复技术、非线性器件线性化(Linear Amplication using Non-Linear Components, LINC)技术、以及预失真技术.其中预失真技术更适合通过数字方法实现,根据其工作频率的不同,又可以分为基带数字预失真(Digital Pre-distortion, DPD)、中频数字预失真以及射频数字预失真.在这3种实现方式中,由于基带数字预失真技术具有较低的复杂度和设计成本,并且能够取得较好的线性化结果,因而具有最高的性价比.另外,以往对数字预失真技术的研究常将预失真功能放在片外处理[7-8],或者将AM-AM和AM-PM失真独立处理[9],而对非线性进行二维处理且片上集成的研究不多.另外,预失真查找表(Look-Up-Table, LUT)的大小和功耗也是一个需要考虑的重点,例如文献[9]虽然进行了片上集成,但是其多达32×32项的查找表及其功耗依然值得优化.

针对宽带全数字正交发射机中数字前端电路越来越高的工作频率和带宽要求的问题,本文设计了一种宽带,高速,且能够使用数字流程实现的插值滤波器.另外,针对数字发射机的非线性问题,本文在数字前端电路中设计了一种便于片上集成的低功耗数字预失真器.

1 数字预失真器

图1所示为数字正交发射机的系统框图,其中数字前端电路包含数字预失真器(Digital Pre-distorter)以及插值滤波器(Interpoaltion Filter)2部分,本节先介绍数字预失真器的设计,第2节则重点介绍高速插值滤波器的设计.

预失真技术的本质其实就是在功率放大器的前面增加一个具有和功放非线性特性互逆的非线性单元,将功放的非线性与预失真器的非线性的逆函数互补,最终达到发射机输入输出线性化的技术,其原理如图2所示.

图1 数字正交发射机系统框图Fig.1 Diagram of digital quadrature transmitter system

图2 预失真实现原理图Fig.2 Principle of pre-distortion

同模拟预失真方案一样,数字预失真技术也是对输入的基带信号进行处理,从而达到发射机系统输出线性化的目的.但是数字预失真技术通常在数字域完成.同模拟预失真技术相比,数字预失真方案具有许多优点,例如灵活性好、可移植性好、易于实现高复杂度的算法,且随着工艺技术的发展,更低的功耗,更小的芯片面积也是数字预失真技术的优势.

对于数字预失真器而言,设计的重点在于查找表存储空间的优化.虽然全面的查找表内容可以提高数字预失真的性能,但同时也会增加硬件的开销.以正交I/Q 2路分别输入12bits数据为例,其对应的查找表地址组合为212·212,那么查找表模块将会变得十分复杂,甚至难以满足设计所需的时序要求.另外从电路设计的角度来看,我们需要将芯片面积以及功耗等考虑在内.采用查找表与线性插值相结合的设计使得二者之间有一个折衷.例如,文献[4]中虽然对查找表内容进行了很大的优化,但仍使用了多达32×32的存储空间.而本文利用对称性,将查找表的存储量进一步降低.并且在查找表中集成了片外可读可写的串行外设接口(Serial Peripheral Interface, SPI),从而可以进一步对查找表的内容进行优化更新.

图3为数字预失真器的设计框图.其各个部分的主要功能如下:

图3 数字预失真模块设计框图Fig.3 Diagram of digital pre-distorter

前置旋转变换(FwdConv)&后置旋转变换(BwdConv): 对前置旋转变换模块而言,输入信号是有符号数,且I/Q 2路数据组成的二维向量是分布在4个象限内的.由于正交发射机4个象限近似呈中心对称,因此,当输入信号不属于第一象限时,需要进行旋转变换,将其转换到第一象限.而后置旋转变换模块则将计算完成的I/Q 2路数据变换到原来的象限.通过象限的变化,可以使查找表规模低至原来的1/4,从而降低芯片硬件消耗,也降低了功耗.

查找表与SPI(LUT&SPI): 查找表的作用是通过输入信号的高位找出表中所存值.查找表为一个17×17的矩阵,查找过程是通过M、N作为矩阵的2个维度的索引,得到P所在的方格点及其相邻格点ABCD的坐标,并取出格点所存的值.而SPI的作用是使得查找表内容可配置,这样我们可以通过测试得到的结果更新查找表中的数据.SPI可以通过PCLK、PSEL、PDI、PDO 4个端口进行配置,采用8-bit地址控制位,总共可以对256个24bits的寄存器单元进行读写控制.

系数生成(Coeff): 系数生成模块的作用是求出线性插值过程需要的插值因子.

MUTIPLY&ADDER: 将主要计算过程进行两级流水处理,以满足时序要求.

数字模块采用TSMC 65nm GP工艺进行DC综合,预失真模块的时钟频率设计在100MHz,并留有一定裕度;SPI模式PCLK的工作频率设计在10MHz.并使用Synopsys的ICC系统布局布线,该模块的I/O口较多,需要谨慎处理I/O的排布,以便利于PAD环的布局,模块端口的摆放策略同样对布局布线的效果有影响.通过对系统芯片以及输入输出管脚布局的优化,确定版图的总体布局;通过对功耗的预估确定电源网络的布局,以满足电阻压降(IR-drop)要求.

2 插值滤波器

根据系统的设计要求,基带输入信号的采样频率限制在100MHz左右,基带信号带宽小于20MHz,升采样后采样频率为2.4GHz,从而升采样率为24.我们知道,时域离散的数字信号的频谱是以采样频率为周期,呈周期性扩展的,因此,在对信号进行升采样时,还需要对其前级的镜像信号进行抑制.另外,滤波器的设计必须满足量化噪声的要求,因此在滤波器建模的过程中,需留一定裕度.

对于一个采样率达24的升采样滤波器来说,如果使用1级滤波器实现,那么滤波器的阶数将会非常高,其中的计算单元将会非常复杂,因此本文采用级联的多级滤波器的方式来实现.考虑到滤波器的采样频率在逐级提高,后级滤波器应该以硬件消耗以及时序约束为主,而前级滤波器则以性能优先.综合以上,我们将升采样滤波器分成4级实现,第1级使用一般的低通有限脉冲响应(Finite Impulse Response, FIR)滤波器实现3倍插值,后面3级则使用半带FIR滤波器各实现2倍插值.

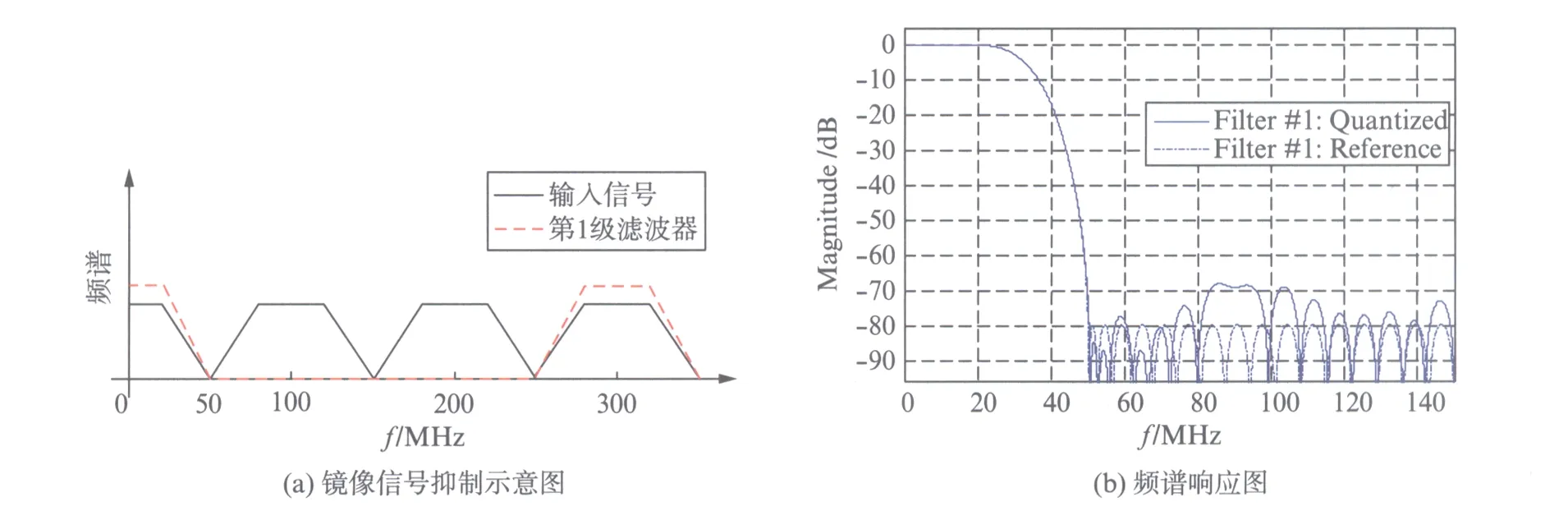

首先考虑第1级滤波器.输入信号的采样频率是100MHz,那么在±100MHz,±200MHz等处都存在输入信号的镜像信号.该信号在经过3倍插值之后输入给第1级滤波器,采样率变为300MHz.那么按照第1级滤波器需要抑制输入信号在100MHz,200MHz出的镜像信号的要求,我们便可以得出第1级滤波器的几个指标:fpass=20MHz,fstop=50MHz.如图4(a)所示,而Apass和Astop分别设为0.02dB和78dB,以留出一定的裕度.但是按照这个指标采用等纹波法设计出的滤波器频谱响应如图4(b)所示,阶数高达41,而且将系数量化为12bits后,阻带衰减大约为68dB.虽然这样可以提高滤波器性能,但是硬件开销会更大,于是我们需要对该滤波器进行优化.

图4 第1级滤波器的设计Fig.4 Design of first stage filter

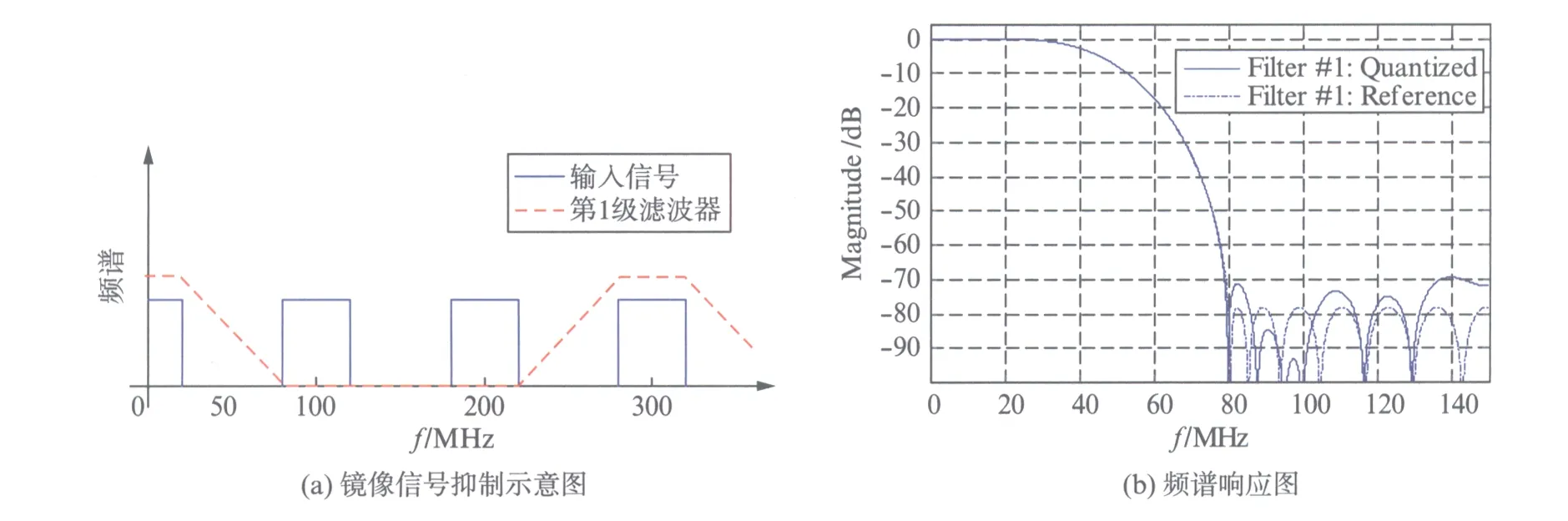

实际上,输入信号是从基带产生的,且一般通用的协议信号在信号频带以外的泄漏很小,如图5(a)所示.基于这一点,我们可以降低第1级滤波器的设计要求.我们将通带频率定为20MHz,而阻带频率定为80MHz,按照与上述设计同样的方法,重新优化出的滤波器的阶数为18,其频谱响应如图5(b)所示.将系数量化为12bits后,阻带衰减恶化到了70dB,仍能满足设计要求.另外,将过渡带展宽的一个好处是可以保留更多的预失真后留下的有用谐波.

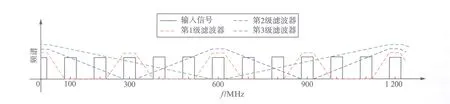

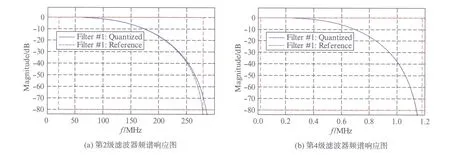

根据数字信号频谱周期性拓展的原理,可以得到图6所示的各级滤波器的频谱响应图.其中第1级滤波器插值比为3,抑制的是(N×300±100)MHz频段上的镜像信号;第2级滤波器插值比为2,抑制的是(N×600±300)MHz处的镜像信号;第3级滤波器插值比为2,抑制的是(N×1200±600)MHz处的镜像信号;同样可以推算出,第4级滤波器可以抑制(N×2400±1200)MHz处的镜像信号.于是,我们可以得出如表1所示的各级滤波器的设计指标.

图5 优化后的第1级滤波器Fig.5 First stage filter after optimization

图6 各级滤波器频谱分布图Fig.6 Spectrum of each filter

滤波器f采样/MHzf通带/MHzf阻带/MHz通带纹波阻带衰减/dB滤波器结构总体240020 800.02-70多级第1级30020800.02-70FIR第2级600205800.02-70HBFIR第3级12002011800.02-70HBFIR第4级24002023800.02-70HBFIR

根据表1中的设计指标,可以设计出3个半带滤波器.其中第2级和第4级滤波器量化前后的频谱响应分别如图7(a),(b)所示.事实上,3个半带滤波器在将系数量化为6bits之后具有形同的设计结果,且滤波器阶数为6.

图7 半带滤波器频谱响应Fig.7 Spectrum of the half-band filter

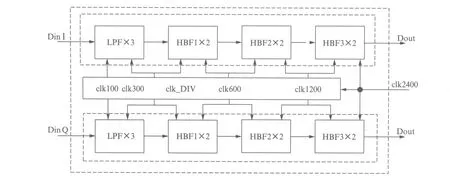

插值滤波器模块包括级联的4级滤波器,同时,由于系统包含正交的2路数据,因此滤波器链路也包括I/Q 2路.另外,由于在升采样的过程中需要用到多个时钟,我们还需要一个时钟分频模块,将输入的最高频时钟进行分频,以提供各个模块所需的时钟,如图8所示.事实上,对于升采样滤波器的设计而言,也可以采用使能信号代替分频时钟,但考虑到采用使能方法,时钟树的工作频率将会更高,从而增大时钟树部分的功耗,并且由于该设计工作频率较高,使用使能信号的方法难以满足时序,故采用分频时钟来实现.

图8 DFE模块设计框图Fig.8 Diagram of DFE

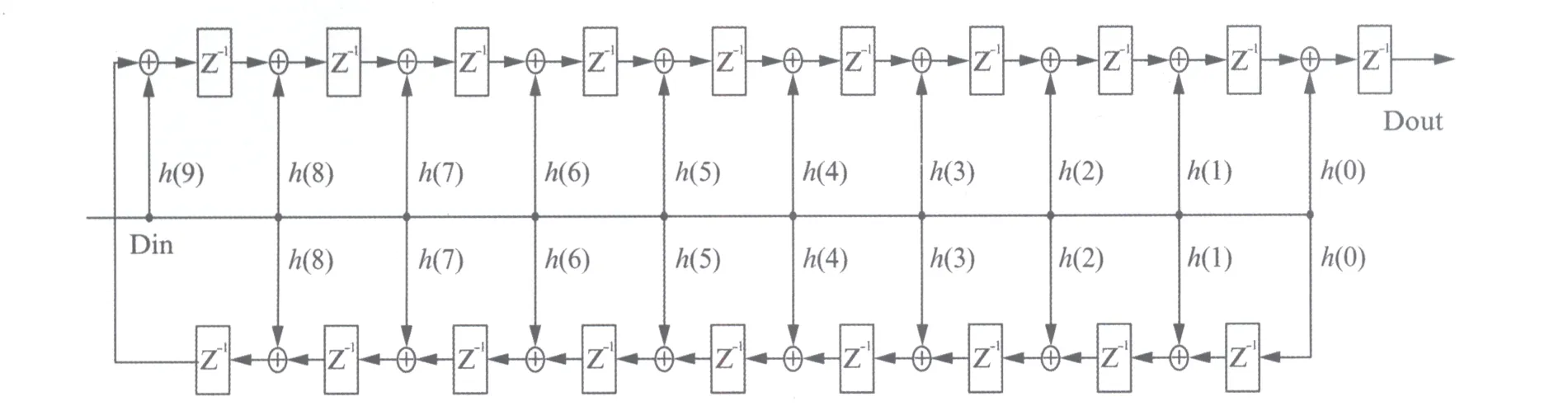

第1级滤波器为低通FIR滤波器,滤波器阶数为18,长度为19,其系数具有偶对称特性,其转置结构的寄存器传输(Register Transfer Lever, RTL)级结构图见图9.滤波器的系数采用12bits的量化精度,输入为12bits,输出为13bits.另外,由于滤波器的系数是确定的,因此系数的乘积用移位相加的方法实现,从而避免了大量的乘法运算.

图9 第1级滤波器结构Fig.9 Structure of the first stage filter

后3级半带滤波器的阶数均为6,当将其系数量化到6bits之后,三者具有相同的系数.由于半带滤波器在升采样之后,工作频率开始逐渐增加,3级滤波器的输出采样频率分别为600MHz、1.2GHz、2.4GHz,因此我们不仅要考虑滤波器的功能实现,还需要对时序以及硬件消耗等因素进行优化.设其系数分别为h(0)~h(6),且具有对称性,其中h(6)=h(0),h(4)=h(2),并且h(5)=h(1)=0.于是,通过将滤波器的延迟单元进行重新组合,可以将乘法单元进行复用.其中,h(4)比h(2)多延迟2拍,h(6)比h(0)多延迟5拍,我们可以将2拍的延迟合并成一个寄存器,并使用升采样前的时钟域进行处理,从而既完成了内插的功能,又实现了乘法单元的复用.优化后的滤波器结构如图10(a)所示.系数的乘法计算同样采用移位相加的方法,以降低关键路径的延迟.

图10 本文提出的半带滤波器的优化结构Fig.10 Structure of the proposed half-band filter

通过DC的逻辑综合发现,工作在600MHz和1.2GHz 2个时钟域的HBF2,以及工作在1.2GHz和2.4GHz的HBF3难以满足时序要求.对于HBF2,我们采取对关键路径部分插入1级寄存器,进行流水线处理的措施即可.而对HBF3而言,在2.4GHz工作频率处时序依旧难以满足,因此还需要进一步插入流水线,如图10(b)所示,然而仅仅依靠插入两级流水线并不能解决在各个工艺角下的时序要求,而进一步的增加流水线会导致硬件消耗的不断增大,同时导致功耗的不断增加,因此我们选择在2级流水线的基础上采用低阈值管实现,以满足各个工艺角下的时序要求.同时需要在后端的布局布线以及时钟树设计阶段进行优化,以减小芯片面积和功耗.

3 版图与仿真结果

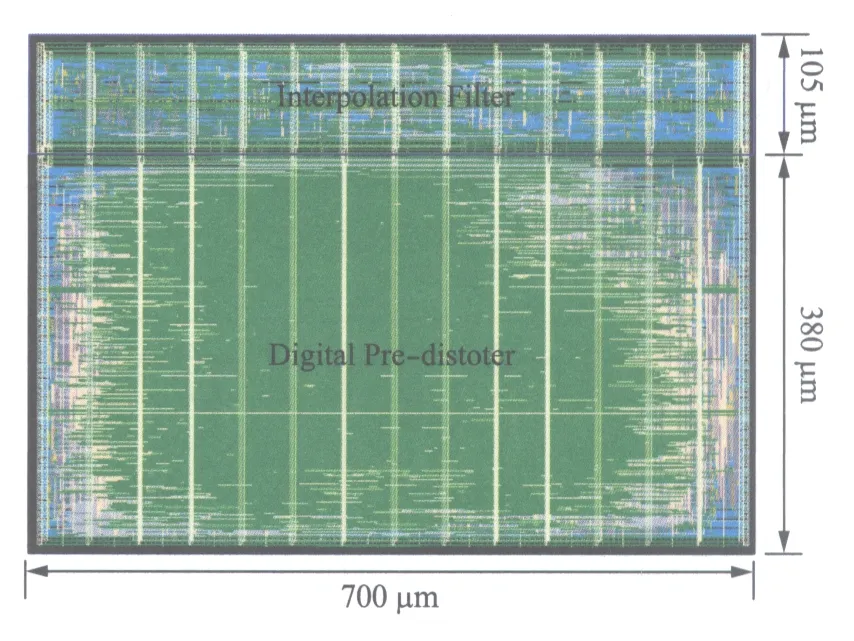

图11 数字前端总体版图Fig.11 Layout of the DFE

图11为正交发射机系统的数字前端总体版图,采用TSMC 65nm GP工艺设计实现.其中数字预失真器的面积为700μm×380μm,寄存器总数为7240个,采用正常阈值管实现以降低漏电流;而插值滤波器的面积为700μm×105μm,除时钟分频器以外的寄存器个数为946,采用的是低阈值管实现,以提高工作频率.使用Prime Time中基于时序仿真的策略进行功耗分析,结果表明,在输入基带带宽为20MHz的正交LTE信号,且预失真开启的情况下,数字预失真器模块的总功耗为3.469mW,其中漏电功耗为59μW;插值滤波器在工作模式下总功耗为31.3mW,其中漏电功耗约为0.6mW.插值滤波器中时钟分频及时钟树部分的功耗占主要部分,约17.1mW,这主要是因为部分时钟树工作在2.4GHz,且需要对时钟有较高的设计要求.数字预失真器虽然面积更大,但由于查找表中的寄存器在通过SPI写入完成后是静态的,不会带来动态功耗;而其查找运算过程的最高工作频率为100MHz,因而动态功耗相比之下要小得多.想比之下差值滤波器虽然寄存器个数少,但其中有些工作在1.2GHz甚至2.4GHz,并且更加严格的时序要求会引入更多的工作在高频率下的缓冲器,因而功耗相对较大.

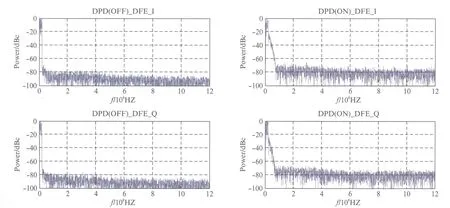

图12所示的是基带信号经过数字预失真器和升采样插值滤波器的输出频谱图,数字部分采用布局布线后的网表结合Prime Time得到的最坏条件下标准延迟文件进行数字电路版图后仿真.其中图12(a)为数字预失真关闭的仿真结果,而图12(b)为数字预失真打开时的仿真结果.对比图12(a)可知,数字预失真模块提供了部分非线性分量,并能够在升采样插值滤波之后提供有效预失真效果.

图12 DFE的输出信号频谱(Fs=2400MHz)Fig.12 Spectrum of DFE output(Fs=2400MHz)注: Fs为采样频率.

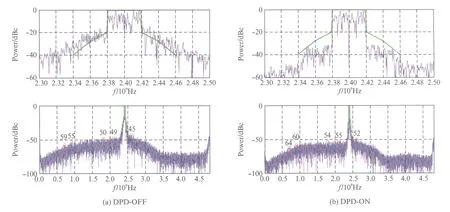

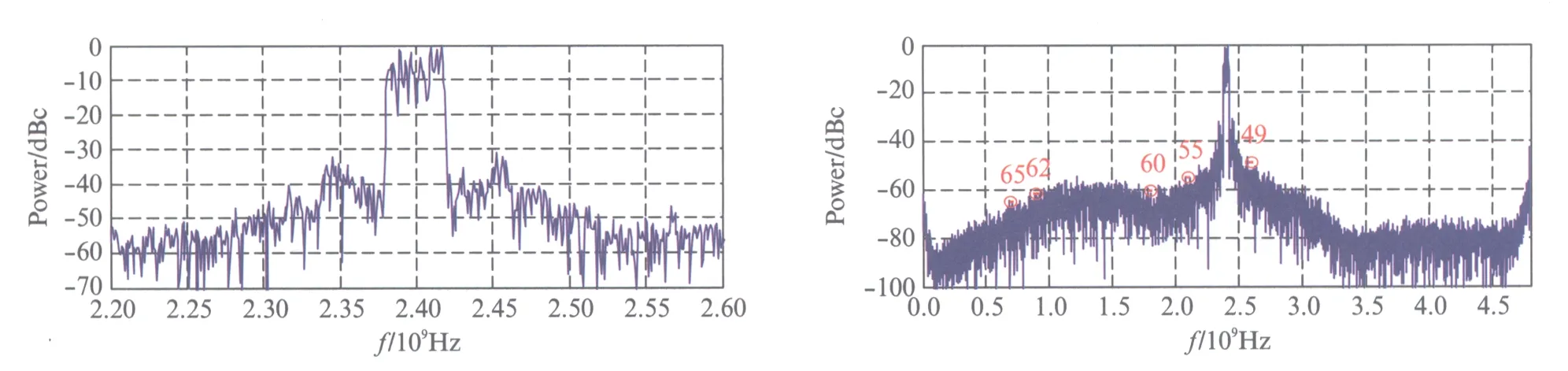

图13(a)和(b)分别为发射机预失真开启前后的输出结果,其中DFE的仿真条件与图12中相同,且查找表是通过对晶体管级的DPA(不包括混频器和驱动电路)进行非线性扫描得到的,而混频器和DPA采用晶体管级电路进行仿真.可以看出预失真开启之后,发射机的邻近信道泄露降低了6dB左右,并且能够满足频谱罩的要求,误差矢量幅度(Error Vector Magnitute, EVM)可以由原来的0.316降低至0.062 9.同时由于此时带外噪声主要受DPA及其阻抗匹配网络的限制,该二维数字预失真对带外噪声的抑制也有所帮助.

图13 发射机的输出频谱1)Fig.13 Spectrum of the transmitter output

而图14的仿真则基于对DPA混频器以及混频和驱动电路的版图提参后的网表进行非线性扫描得到的预失真查找表,同时,DFE部分的仿真条件与前面相同,即都采用数字电路后仿真流程,且为worst case下的仿真结果.而包括混频器与驱动电路在内的DPA则采用版图提参后的网表进行仿真.可以发现,发射机带内线性度可以降低至0.032 6,这说明该二维数字预失真器对混频和驱动等电路的造成的非线性同样有效.预失真前后性能总结如表2所示.

图14 发射机的输出频谱2)Fig.14 Spectrum of the transmitter

工作模式ALCR/dBMASKEVM/dBEVM/%OOBN/dB900MHz1.8GHz2.6GHzDPD-OFF-26不满足-10.0031.60-50-49-45DPD-ON1)-32满足-24.026.29-54-55-52DPD-ON2)-31满足-29.743.26-60-55-49

注: 1) 预失真查找表通过对DPA进行非线性扫描得到;2) 预失真查找表通过对DPA以及混频和驱动电路进行非线性扫描得到.

4 总 结

本文设计了一种应用于全数字正交发射机的数字预失真器及数字前端电路.通过仿真表明,所设计的高速升采样数字滤波器能够将基带信号从100MHz升采样至2.4GHz,同时能够有效滤除镜像信号,并且能够保留部分数字预失真器的非线性分量;而带有数字预失真器的数字前端能够将正交发射机的带内线性度从0.316提升至0.032 6,并能够对邻近信道抑制以及带外噪声有所抑制.同时,本文在TSMC 65nm GP工艺下使用数字电路流程进行设计,通过对前端RTL级以及后端布局布线的优化,低功耗数字预失真器采用正常阈值管进行实现,模块版图面积为0.266mm2,功耗的估算结果约为3.5mW;插值滤波器采用低阈值管实现,模块版图面积为0.073mm2,包括时钟分频模块以及时钟树在内的功耗估算结果为31.3mW.另外,表3中列出了DFE以及发射机性能与其他论文的对比.

表3 不同设计的性能对比

注: *包含时钟分频模块.

[1] LU C, WANG H, PENG C H,etal. A 24.7 dBm all-digital RF transmitter for multimode broadband applications in 40 nm CMOS [C]∥ISSCC 2013. Digest of Technical Papers. San Francisco, USA: IEEE Press, 2013: 332-333.

[2] JIN H D, KIM D S, JIN S S,etal. Efficient digital quadrature transmitter based on IQ cell sharing [C]∥ISSCC 2015. Digest of Technical Papers. San Francisco, USA: IEEE Press, 2015: 168-169.

[3] YE L, CHEN J, KONG L K,etal. Design considerations for a direct digitally modulated WLAN transmitter with integrated phase path and dynamic impedance modulation [J].IEEEJournalofSolid-StateCircuits, 2013,48(12): 1-18.

[4] WANG H, PENG C H, CHANG Y,etal. A highly-efficient multi-band multi-mode all-digital quadrature transmitter [J].IEEETransactionsonCircuitsandSystems-I:RegularPapers, 2014,61(5): 1321-1330.

[5] HEZAR R, DING L, HUR J,etal. A 23 dBm fully digital transmitter usingSigma-Deltaand pulse-width modulation for LTE and WLAN applications in 45 nm CMOS [C]∥Proceeding IEEE Radio Freq Integr Circuits Symp(RFIC). Tampa, FL, USA: IEEE Press, 2014: 217-220.

[6] ZHAO Y, SHEN Y L, XUE P. An all-digital Gigahertz class-S transmitter in a 65-nm CMOS [J].IEEETransMicrowTheoryTech, 2016,24(4): 1402-1410.

[7] BHAT R, KRISHNASWAMY H. A watt-level 2.4 GHz RF IQ power DAC transmitter with integrated mixed-domain FIR filtering of quantization noise in 65 nm CMOS [C]∥Proceeding IEEE Radio Freq Integr Circuits Symp(RFIC). Tampa, FL, USA: IEEE Press, 2014: 414-416.

[8] ALAVI M S, STASZEWSKI R B, VREEDE L C N. A wideband 2×13-bit all-digital I/Q RF-DAC [J].IEEETransMicrowTheoryTech, 2014,62(4): 732-751.

[9] CHOWDHURY D, YE L, ALON E,etal. An efficient mixed-signal 2.4-GHz polar power amplifier in 65-nm CMOS technology [J].IEEEJournalofSolid-StateCircuits, 2014,49(7): 1796-1809.

[10] WANG H, PENG C H, CHANG Y P,etal. A highly-efficient multi-band multi-mode all-digital quadrature transmitter [J].IEEEJournalofSolid-StateCircuits, 2014,61(5): 1321-1330.

Abstract: A Digital-Front-End(DFE) in all-digital quadrature-transmitter is designed. The DFE consists of I/Q quadrature high speed digital filter with interpolation rate of 24, up-sampling 20 MHz baseband signal from 100 MHz to 2.4 GHz, and depressing image signal as well. The first stage filter is designed with transposed architecture, and the order of the filter is reduced from 41 to 18 after optimization of transition band. The function of interpolation and filter of the latter 3 stage filters are combined together to reduce frequency for part of the filter, thus reduce power consumption; what’s more, the filter is designed with LVT MOST and the critical path is pipelined to meet the timing requirements. A low power Serial Peripheral Interface(SPI) configurable Look-Up-Table(LUT) is added in DFE to realize the function of digital pre-distortion(DPD), and it is reduced to 17×17 terms with symmetry principle. The total area of DFE is 0.34mm2, and the power consumption is about 34.8mW with clock division part included, with which the power consumption of DPD is only 3.5 mW. Simulation result indicates that, the proposed DFE can reduce EVM from 31.6% to 3.26% with digital pre-distorter turn on.

Keywords: digital front end; interpolation filter; digital pre-distortion; error vector magnitute

DesignofaDigitalFrontEndinAll-DigitalQuadrature-Transmitter

YE Feng, SHEN Yilei, XUE Pan, ZHANG Hongguang, HONG Zhiliang

(StateKeyLaboratoryofASIC&Systems,FudanUniversity,Shanghai201203,China)

TN47

A

0427-7104(2017)03-0336-10

2016-06-09

国家自然科学基金(61376030)

叶 峰(1990—),男,硕士研究生;洪志良,男,教授,通信联系人,E-mail: zlhong@fudan.edu.cn.