数字频率计的系统设计与仿真研究

2017-09-11谢晓斌谢晓玲安雅丽

苗 军,谢晓斌,谢晓玲,安雅丽

(1.甘肃电器科学研究院,甘肃天水741018;2.甘肃省高低压电气研发检测技术重点实验室,甘肃天水741018)

数字频率计的系统设计与仿真研究

苗 军1,2,谢晓斌1,2,谢晓玲1,2,安雅丽1,2

(1.甘肃电器科学研究院,甘肃天水741018;2.甘肃省高低压电气研发检测技术重点实验室,甘肃天水741018)

数字频率计是一种基本的测量仪器,被广泛应用于航天、电子、测控等领域。采用等精度频率测量方法具有测量精度保持恒定,不随所测信号的变化而变化的特点。利用等精度测量原理,通过FPGA运用VHDL编程,利用FPGA(现场可编程门阵列)芯片设计了一个8位数字式等精度频率计,该频率计的测量范围为0MHz-100MHz,利用QUARTUSⅡ集成开发环境进行编辑、综合、波形仿真,并下载到CPLD器件中,经实际电路测试,仿真和实验结果表明,该频率计有较高的实用性和可靠性。

VHDL语言;频率测量;数字频率计

1 引言

随着IC技术的发展,电子设计自动化(Electronic Design Automation,EDA)己经逐渐成为重要的设计手段,被广泛应用于模拟与数字电路系统等许多领域。在电子技术设计领域,可编程逻辑器件(如CPLD、FPGA)的应用,为数字系统的设计带来了极大的灵活性[1]。EDA技术的出现,极大地提高了电路设计的效率和可操作性,FPGA能提供良好的滤波器设计,而且能完成DSP高级数据处理功能,因而FPGA在现代通信领域方面获得广泛应用。VHDL主要用于描述数字系统的结构、行为、功能和接口。这种将设计实体分成内外部分的概念是VHDL系统设计的基本点[2]。数字频率计是数字电路中的一个典型应用,随着复杂可编程逻辑器件(CPLD)的广泛应用,以EDA工具作为开发手段,运用VHDL语言将使整个系统大大简化,提高整体的性能和可靠性。采用VHDL编程设计实现的数字频率计,除被测信号的整形部分、键输入部分和数码显示部分外,其余全部在一片FPGA芯片上实现。整个系统非常精简,且具有灵活的现场可更改性[3]。

本研究利用VHDL在FPGA器件上实现一种8位数字频率计测频系统,能够用十进制数码显示被测信号的频率,不仅能够测量正弦波、方波和三角波等信号的频率,而且能对其他多种频率信号进行测量。具有体积小、可靠性高、功耗低的特点。

2 频率测量

2.1 数字频率计工作原理

数字频率计的设计原理实际上是测量单位时间内的周期数。该方法免去了实测以前的预测,同时节省了划分频段的时间,克服了原来高频段采用测频模式、低频段采用测周期模式的测量方法中存在换挡速度慢的缺点[4]。采用一个标准的基准时钟,在单位时间(1s)里对被测信号的脉冲数进行计数,即为信号的频率。直接测频法只适合测量频率较高的信号,不能满足在整个测量频段内的测量精度保持不变的要求[5]。为解决低频段测量的不准确问题,采用门控信号和被测信号对计数器的使能信号进行双重控制,大大提高了准确度。

2.2 等精度测频及误差分析

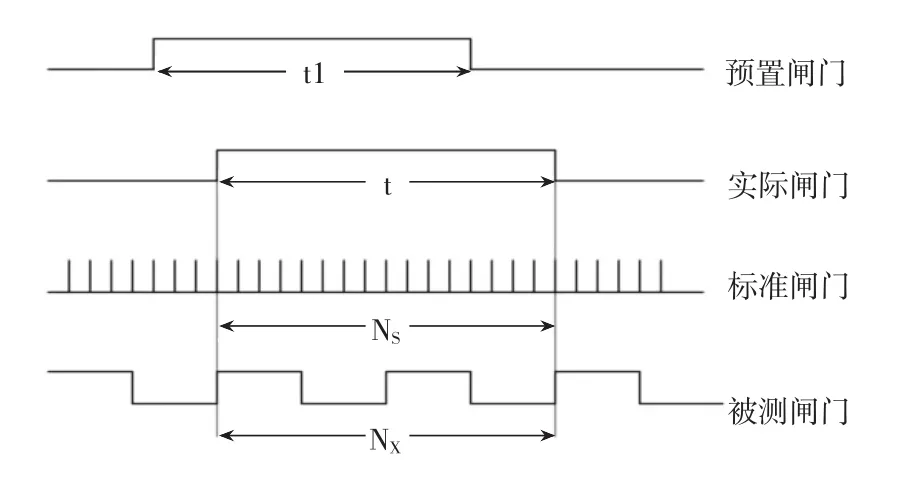

等精度测频方法是在直接测频方法的基础上发展起来的。它的闸门时间不是固定的值,而是被测信号周期的整数倍,即与被测信号同步,因此,避除了对被测信号计数所产生±1个字误差,并且达到了在整个测试频段的等精度测量[6]。其测频原理如图1所示。在测量过程中,有两个计数器分别对标准信号和被测信号同时计数。

图1 等精度测频原理波形图

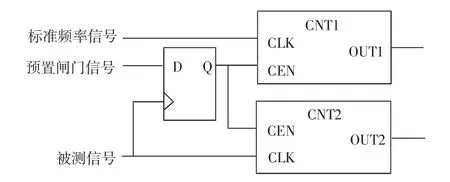

等精度测频的实现方法可简化为图2所示。CNT1和CNT2是两个可控计数器,标准频率信号从CNT1的时钟输入端CLK输入;经整形后的被测信号从CNT2的时钟输入端CLK输入。在预置门时间和常规测频闸门时间相同而被测信号频率不同的情况下,等精度测量法的测量精度不变。

图2 等精度测频实现原理图

在误差分析方面,测量频率的相对误差与被测信号频率的大小无关,仅与闸门时间和标准信号频率有关,即实现了整个测试频段的等精度测量[7]。闸门时间越长,标准频率越高,测频的相对误差就越小。标准频率可由稳定度好、精度高的高频率晶体振荡器产生,在保证测量精度不变的前提下,提高标准信号频率,可使闸门时间缩短,即提高测试速度[8]。

3 数字频率计的系统设计与仿真

3.1 系统的总体设计

数字频率计的系统框图如图3所示。主要由5个模块组成,分别是信号源模块、控制模块、计数模块、锁存器模块和显示器模块。

图3 数字频率计的系统框图

根据数字频率计的系统原理,cnt控制信号发生器,reg32b为锁存器,Cnt10为十进制计数器,display为七段译码显示驱动电路,可以将频率计数的结果译成能在数码管上显示的相对应的阿拉伯数字,便于读取测量的结果。为了实现系统功能,测频控制信号发生器testctl、计数器Cnt10、锁存器reg32b存在一个工作时序的问题,设计时需要综合考虑[9]。8位数字频率计的顶层框图设计包括信号源模块(F1MHz、CNT)、频率计模块(FREQ)和显示模块(display)三大模块。

3.2 信号源模块

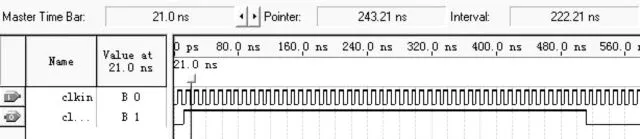

信号源是为了产生1MHz的门控信号和待测的定频信号,而对输入系统时钟clk(50MHz)进行分频的模块,设计源代码PIN1MHz.VHD对输入系统时钟clk(50MHz)进行分频产生1MHz信号。PIN1MHz封装如图4所示,图中CLKIN为接入的100MHz信号,图中CLKOUT为接到CNT的CLK的1MHz的信号。

图4 PIN1MHz封装图

PIN1MHz的工作时序仿真图如图5所示:

图5 信号源模块仿真图

从PIN1MHz的工作时序仿真图可以看出,由系统时钟提供的100MHz的输入信号,经过信号源模块,通过100分频产生1MHz的时钟信号,达到了设计所需的预期效果[10]。

3.3 分频器

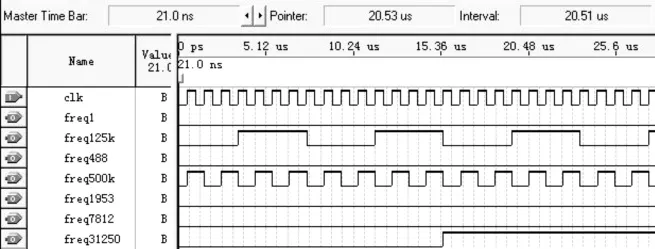

CNT的封装如图6所示,图中CLK为PIN1MHz输入的1MHz信号,freq1为输出给控制信号发生器的1Hz信号,7812Hz的输出频率freq7812被作为显示模块的时钟输入,freq488、freq1953、freq31250、freq125K、freq500K作为待测信号。CNT的工作时序仿真图如图7所示。

图6 CNT封装图

图7 CNT的时序仿真图

当1MHz频率波形输入后,分别产生了设计所需要的500kHz的输出频freq500k,125kHz的输出频率freq125k,31250Hz的输出频freq31250,7812Hz的输出频率freq7812,1953Hz的输出频率freq1953,488Hz的输出频率freq488,1Hz的输出频率freq1。

3.4 测频控制信号产生器

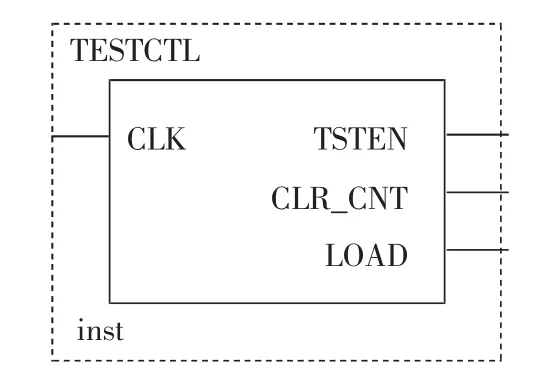

控制模块的作用是产生测频所需要的各种控制信号[11]。控制信号的标准输入时钟为1Hz,每两个时钟周期进行一次频率测量。该模块产生的3个控制信号,分别为 TSTEN、LOAD、CLR_CNT。测频控制产生器如图8所示,图中CLK接CNT的FREQ1的1Hz的信号,TSTEN为计数允许信号,接计数器CNT10的ENA,CLR_CNT信号用于在每次测量开始时,对计数器进行复位,接计数器CNT10的CLR,LOAD接锁存器的LOAD。

图8 TESTCTL的封装图

测频控制信号发生器TESTCTL的工作时序图,控制模块的几个控制信号的时序关系图如图9所示。

图9 TESTCTL的时序仿真图

从图中可看出,计数使能信号TSTEN在1s的高电平后,利用其反相值的上跳沿产生一个锁存信号LOAD,随后产生清0信号上跳沿CLR_CNT。为了产生这个时序图需首先建立一个由D触发器构成的二分频器,在每次时钟CLK上升沿到来时令其翻转[12]。其中,控制信号时钟clk的频率取1Hz,而信号TSTEN的脉宽恰好为1s,可以用作闸门信号。此时,根据测频的时序要求,可得出信号LOAD和CLR_CNT的逻辑描述。由图知,在计数完成后,计数使能信号TETEN在1s的高电平后,利用其反相值的上跳沿产生一个锁存信号LOAD,0.5s后,CLR_CNT 产生一个请零信号上跳沿[13]。

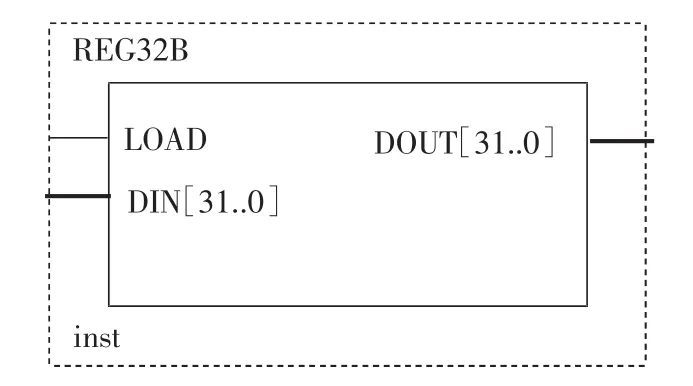

3.5 锁存器

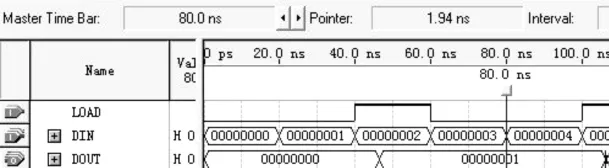

锁存器模块在测量模块测量完成后,在load信号的上升沿时刻将测量值锁存到寄存器中,然后输出到显示模块[14]。锁存器REG32B的封装如图10所示,图中LOAD接控制测频产生器TESTCT的 LOAD,而 DIN[31..0]接计数器 CNT10 的 CQ[3..0],DOUT[31..0]接显示器 display的 in 端。32 位锁存器REG32B的工作时序图如图11所示。

图10 REG32B的封装图

图11 REG32B的时序仿真图

本程序是用来实现锁存器模块的功能,但它的程序相当简单,在锁存信号load的上升沿到来时,锁存器将测量值锁存到寄存器,然后输出到显示模块[15]。但从仿真图11中可以明显地看出,锁存输出并不是立即进行的,而是经历了一个短暂的延时,这是由于硬件引起的。

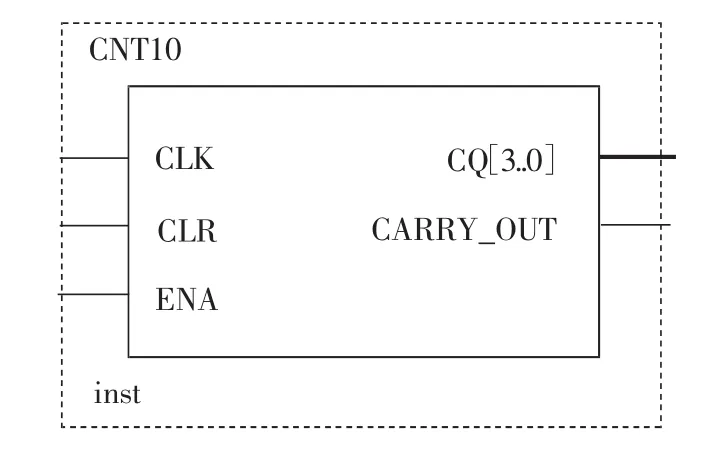

3.6 十进制计数器

计数器模块是由8个带有异步清零端,进位信号输出的模为10的计数模块级连而成。通过(freq.vhd)进行元件例化实现。此十进制计数器的特点是,有一时钟使能输入端ENA,用于锁定计数器。当高电平计数允许,低电平时计数禁止。计数器模块用于对输入信号的脉冲进行计数,该模块必须有计数允许、异步清零等端口,以便于控制模块对其进行控制[16]。

CNT10的封装如图12所示,其中CLR为复位接TESTCTL的 CLR_CNT端,ENA 接 TESTCTL的TSTEN 端,CQ[3..0]接锁存器的 DOUT[31..0]端。

图12 CNT10的封装图

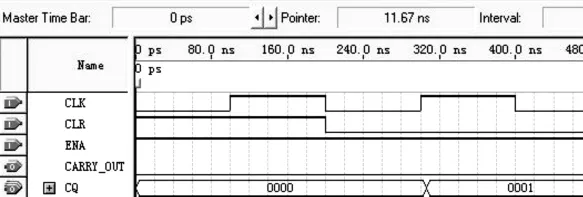

有时钟使能的十进制计数器CNT10的工作时序仿真如图13所示。

图13 CNT10的时序仿真图

此程序模块实现的功能是带使能端的10进制计数。程序要求只有当使能端信号为高电平时计数器才能正常工作,每个时钟的上升沿到来时计数器加1,因为这里要实现的是10进制计数,所以当计数到10时计数器清零,同时产生进位信号,这里的进位信号仅为一个脉冲信号,一旦计数从10变为1,脉冲信号立即变为低电平。同时该计数器也应带有清零信号,一旦清零信号为高电平,计数器立即清零[17]。

3.7 显示模块

3.7.1 显示模块设计

本研究中设计了一个3位的循环计数器,将计数结果输入到译码器,译码结果输出即可依次使能每个LED。display模块的顶层如图14所示。CNT计数产生扫描信号(位码),LED模块用于查表产生LED段码输出。图中in0~in7接锁存器的DOUT[31..0]端。

图14 display的封装图

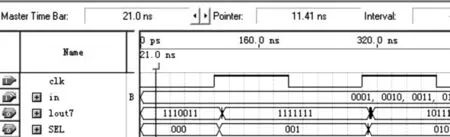

display工作时序图如图15所示。

图15 display工作时序图

用8个LED将待测频率显示出来,将通过十进制计数器的时钟信号CLK,输出为时钟信号计数译码后的显示驱动端,在八段LED译码为对应的八段二进制编码,并由数码显示器显示出来。图15所示为相应二进制编码与相对应的屏显数字[18]。

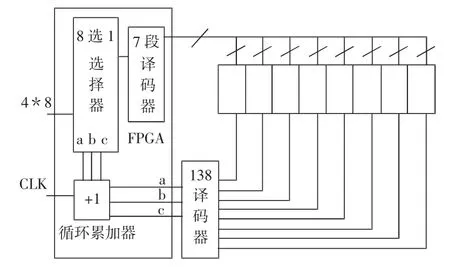

3.7.2 显示电路

图16 display硬件结构图

此部分如图16所示,图中主要由0-7循环累加器、3-8译码器、BCD-7段显示译码器、8选1多路数据开关和8个LED显示器组成的扫描数码显示器[19]。3.7.3 译码器

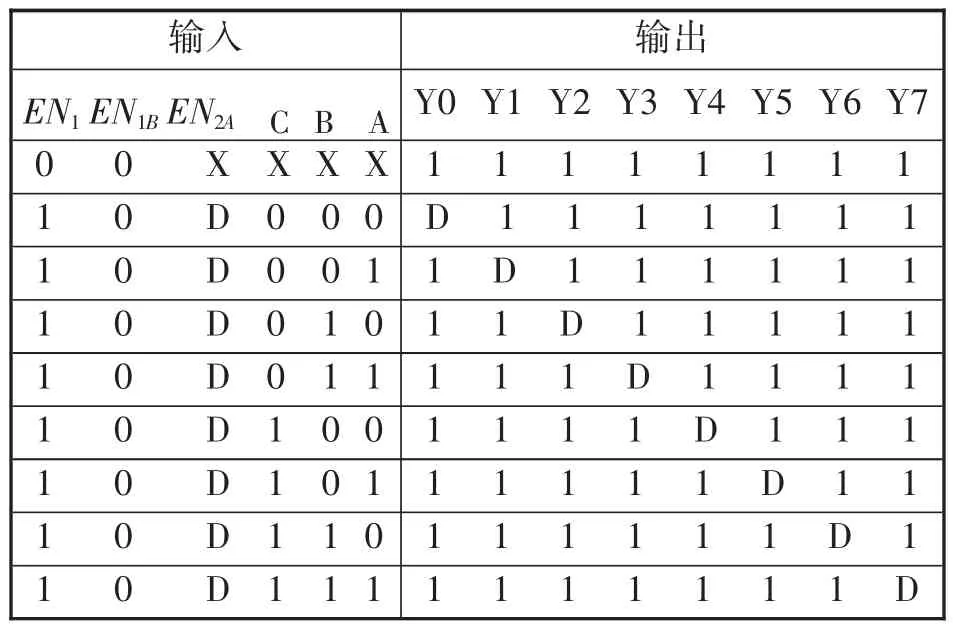

74138译码器作为数据分配器的功能表如表1所示。

表1 74LS138编码器作为数据分配器的功能表

74LS138的3个译码输入C、B、A用做数据分配器的地址输入,8个输出Y0-Y7用做8路数据输出,3个输入控制端中的EN2A用做数据输入端,EN2B 接地,EN1用做使能端[6]。当 EN1=1,允许数据分配,若需要将输入数据转送至输出端Y2,地址输入应为CBA=010,由功能表可得:

而其余输出端均为高电平。因此,当地址CBA=010时,只有输出端Y2得到与输入相同的数据波形。本研究通过运用QUARTUSⅡ集成开发环境对各功能模块进行编辑、综合、波形仿真,对各功能模块的的仿真图及其仿真功能做了设计分析,对本设计的实现起到了主要作用[20]。

4 结束语

本研究对等精度频率计进行了系统的设计。介绍了频率测量的一般方法,着重介绍等精度测频原理并进行了误差分析,利用等精度测量原理,通过FPGA运用VHDL编程,利用FPGA(现场可编程门阵列)芯片设计了一个8位数字式等精度频率计,该频率计的测量范围为0MHz-100MHz,利用QUARTUSⅡ集成开发环境进行编辑、综合、波形仿真,并下载到FPGA器件中,经实际电路测试、仿真和实验结果表明,该频率计有较高的实用性和可靠性,达到预期的结果。和传统的频率计相比,利用FPGA设计的频率计简化了电路板设计,提高了系统设计的实用性和可靠性,实现数字系统的软件化,这也是数字逻辑设计的趋势。

[1]潘 松.EDA实用技术教程[M].北京:科学出版社,2003.

[2]潘 松.EDA技术与VHDL[M].北京:清华大学出版社,2013.

[3]黄 任.AVR单片机与CPLD/FPGA综合应用入门[M].北京:北京航空航天大学出版社,2004.

[4]许发翔等.基于FPGA的数字频率计的设计[J].电子制作,2014(23).

[5]熊潇等.高精度频率计的设计与研究[D].武汉科技大学,2014.

[6]唐海斌等.基于FPGA的一种测频方法的研究[J].电子世界,2014(17).

[7]宋万杰等.CPLD技术及应用[M].西安:西安电子科技大学出版社,1999.

[8]刘宝琴等.ALTERA可编程器件及应用[M].北京:清华大学出版社,1995.

[9]亿特科技.CPLD/FPGA应用系统设计与产品开发[M].北京:人民邮电出版社,2005.

[10]杜娟等.基于FPGA的等精度数字频率计设计[J].南阳理工学院学报,2015(04).

[11]求是科技.CPLD/FPGA应用开发技术与工程实践[M].北京:人民邮电出版社,2005.

[12]Electronic design automation(EDA)solutions for ESD-robust design and verification.Dzerzhinsky,MG.Custom Integrated Circuits Conference,2012

[13]任晓东.CPLD/FPGA 高级应用开发指南[M].北京:电子工业出版社,2003.

[14]程云长.可编程逻辑器件与VHDL语言[M].北京.科学出版社,2005.

[15]廖裕评等.CPLD数字电路设计—使用MAX+PLUSⅡ[M].北京:清华大学出版社,2001.

[16]卢毅等.VHDL与数字电路设计[M].北京:科学出版社,2001.

[17]XIE Meng,SHEN Zhong -Ru.The project of frequence based on CPLD.Microc-omputer Information[J],2011,27(4):58-59.

[18]张玉梅等.QuartusⅡ仿真软件在数字电子技术教学中的应用[J].沈阳师范大学学报(自然科学版),2014(01).

[19]MIAO Rong-xia,DAI Bao-hua,WANG Ying-li,WANG Kun.The System of Har -dware Measuring Frequency Based on CPLD.Machinery & Electronics[J],2008(8):55-56.

[20]凌振宝等.多功能数字频率计的设计与研究[J].吉林大学学报(信息科学版),2011(04).

System design and simulation of digital frequency meter

MIAO Jun1,2,XIE Xiao-bin1,2,XIE Xiao-ling1,2,AN Ya-li1,2

(1.Gansu Electric Apparatus Research Institute,Tianshui 741020,China;2.Key Laboratory of High-low Voltage Electrical Apparatus Inspection Technology,Tianshui 741018,China)

The digital frequency meter is a basic measuring instrument.It is widely used in aerospace,electronics,monitoring and other fields.The equal precision frequency measurement can keep constant accuracy which will not change with the variable measured signals.A 8-bit digital frequency meter is designed with the sequal precision measuring principle and using VHDL programming and FPGA (Field Programmable Gate Array) chip.This frequency meter measuring range is 0MHz-100MHz,and which can use QUARTUS Ⅱintegrated development environment for editing,synthesising,simulating and downloading.The actual testing and experimental results show that the frequency meter has high reliability and has good practical value.

VHDL;frequency measurement;digital frequency meter

TM131

A

苗 军(1968-),男,工程师,本科,研究方向为电气设计及电器检测技术。现就职于甘肃电器科学研究院

2017-05-01

1005—7277(2017)02—0035—06