EDA在线阵CCD驱动电路设计教学中的应用

2017-09-08祝世平周富强刘惠兰张永健

祝世平, 周富强, 刘惠兰, 张永健

(北京航空航天大学 仪器科学与光电工程学院, 北京 100191)

EDA在线阵CCD驱动电路设计教学中的应用

祝世平, 周富强, 刘惠兰, 张永健

(北京航空航天大学 仪器科学与光电工程学院, 北京 100191)

CCD(电荷藕合器件)是一种广泛应用的固体成像器件,在CCD应用中的关键问题之一是其驱动电路的设计。在本科生实验课程中开设的CCD驱动电路设计实验能帮助学生巩固所学的模拟电路和数字电路的知识,使学生在分析、设计和动手能力等方面得到提高,使实验教学和课堂教学得到结合。本文给出了在实验课程中采用EDA软件针对线阵CCD TCD2252D驱动电路的几种设计方案。

CCD;驱动电路设计; FPGA;Proteus

0 引言

CCD(Charge Coupled Device)作为一种新兴的固体成像器件, 具有体积小、重量轻、分辨率高、灵敏度高、可靠性好等优点,广泛应用于机器视觉系统、视频监控和安防系统、智能交通系统以及互联网等领域[1-4]。

CCD应用的关键之一是驱动电路的设计。因不同厂家生产的CCD其驱动时序不尽相同,且同一厂家生产的不同型号的CCD其驱动时序也不完全一样,从而使CCD驱动电路设计很难实现规范化,因此用户必须认真面对CCD驱动电路的设计问题[5-10]。随着EDA软件平台的不断进步,在设计CCD驱动电路方面,EDA软件发挥着不可替代的作用。

CCD驱动电路的设计既能充分利用学生现有的数字电路、模拟电路的知识,又具有一定的实用价值。因此我院针对本科生开设了基于线阵CCD的综合实验,使学生熟悉线阵CCD的基本工作原理以及其测量原理,同时在实验课下让学生完成线阵CCD驱动电路的设计与仿真,并进行仿真结果的验证和检查。本实验课程使学生在分析、设计和动手能力等方面得到提高,同时使实验教学和课堂教学紧密结合。

基于此,本文以东芝公司线阵CCD 图像传感器TCD2252D为例,探讨了在实验课程中EDA软件在线阵CCD驱动电路设计中的应用,并给出几种实用的设计方案。

1 利用Multisim设计IC电路

图1引用东芝公司TCD2252D技术手册,给出了TCD2252D线阵CCD驱动电路的各个驱动脉冲的时序要求。本文所有的时序设计均以此为依据。在设计驱动电路时,首先以高低电平的时序关系为主要设计对象,待后期进行调试时再考虑上升沿与下降沿的影响。

图1 线阵TCD2252D驱动电路的驱动脉冲时序要求

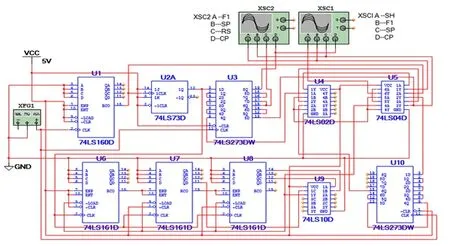

Multisim是美国国家仪器(NI)有限公司推出的以Windows为基础的仿真工具,是一款很好的EDA(Electronic Design Automation)设计软件,适用于板级的模拟/数字电路板的设计工作。在进行实际电路的搭建时,首先利用Multisim进行时序电路图的设计,然后进行仿真。为之后实物搭接的电路实验进行指导,方便其调试与修改。本文所设计的电路图如图2所示。

图2 线阵TCD2252D驱动电路的Multisim设计电路图

本方案的总体设计的步骤是:先形成满足占空比的波形,然后对各个波形进行延时以达到满足CCD时序驱动的要求。故先从理论上推导出满足时序要求所需要的D触发器及非门的个数,然后通过示波器(Multisim或实际搭建电路时)的观察来得到需要的波形,线阵CCD TCD2252这款芯片所需的驱动信号有SH,φ1、φ2,SP,RS,CP等,它们的实现详述如下:

(1) SH的实现:SH的实现主要是靠1400进制的计数器,这里采用的是三个16进制计数器(74LS161),可以比其它进制的计数器少用芯片而达到相同的效果。2800D=101011110000B从而知道将U8的QC和QA端引出,U7的QD端引出,即约为一个1400计数器(从CCD驱动原理上知道只需要满足SH大于1388个Φ1的周期即可,故在此用1408代替,误差可以忽略),Φ1的频率为0.5 MHz,故其一个周期的时间刚好为2000 ns,当Φ1的第1407个上升沿到来时SH被置高电平,当第1408个Φ1的上升沿到来时,SH复位,刚好为2000 ns。再将它根据实际的需要进行一定时间的延时,即可得到满足要求的SH波形。

(2) φ1、φ2的实现:相对较为简单,它接一个JK触发器,J=K=1,每来一个上升沿实现一次翻转,这样就能将时钟十分频后的信号进行二分频,得到满足驱动要求的0.5 MHz的1:1的方波,后面接的U10是一个8D触发器,它主要是配合整个电路的驱动时序实现对Φ1的延时,从而得到满足要求的脉冲。

(3) SP、RS和CP的实现:三者的实现原理是相同的,只不过是在时间延时方面不同,可以选择先产生某一信号如SP,然后对其进行延时,即可得到RS和CP,SP的产生直接利用10 MHz的信号延时调整后与SH“或”即可得到(也可以先进行“或”操作再进行延时而得到),再对SP进行一些时序上的延时处理以达到满足要求的三个信号。如图2所示:U3的5D、6Q和8Q输出的即为相应的SP、RS和CP。

本方案选择10 MHz晶振作为整个驱动电路的驱动时钟,利用一个10进制计数器U1对其进行分频,即可得到占空比为1:9的频率为1 MHz的方波,再利用一个JK触发器U2A进行二分频,即可得到频率为0.5 MHz的方波,把它作为1408计数器(U6-U7-U8)的驱动时钟,当第1407个U2A,剩下的就是利用SH与RS进行逻辑运算,再经过延时处理,即可得到满足要求的波形。在延时方面,考虑到每一个非门延时15 ns左右,每个施密特触发器(74LS14)延时约22 ns,而D触发器在驱动时钟为10 MHz时延时约100 ns,故可以利用此来设计具体的时序要求。

2 基于FPGA进行驱动电路设计

本方案采用ALTERA 公司的EP1C6Q240 芯片,利用的实验平台是ALTERA公司的Quartus II 8.0 Web Edition版。Quartus II是Altera公司推出的CPLD/FPGA开发工具,它提供了完全集成且与电路结构无关的开发包环境,具有数字逻辑设计的全部特性。用FPGA实现驱动电路的设计有许多方法,例如通过VHDL语言、Verilog HDL语言等,在已经搭建好IC仿真电路的基础上,有一种更为方便的方式,那就是利用Quartus II 的原理图输入方式,可以充分利用软件本身已经写好的各个逻辑部件的语句,利用在Multisim里的电路图进行搭建,在一些细节处进行修改(如某些延时方面采用D触发器进行等)即可完成FPGA的驱动设计。利用Quartus II设计的电路图如图3所示。

图3 线阵TCD2252D驱动电路的Quartus II设计电路图

图中U1部分:由于使用的时钟是50 MHz的脉冲,因此此部分将时钟进行分频,变为10 MHz的时钟信号作为整个电路的驱动;U2部分为10分频电路,对10 MHz的时钟进行分频以得到1 MHz的RS信号;U3部分为RS具体产生电路,它用U2部分产生的信号取反后与SH或即可得到实际要求的RS信号,再经过一个74LS273(8D触发器)进行延时后即可以产生所需要的SP、RS、CP信号;U5部分为Φ1、Φ2的产生电路,它由U3的JK触发器得到原始信号后经过D触发器延时得到要求的Φ1、Φ2信号;U4部分为1400进制的计数器,它的驱动脉冲来自U3产生的Φ1原始脉冲,每1408个Φ1脉冲即可产生一个SH高电平,它即是所要求的SH脉冲。

3 利用Proteus进行单片机仿真设计

Proteus软件是英国Labcenter electronics公司推出的EDA工具软件。它不仅具有其它EDA工具软件的仿真功能,还能仿真单片机及外围器件。它是目前最好的仿真单片机及外围器件的工具。

设计电路图如图4所示,其中XTAL1和XTAL2是MEGA16的时钟输入端,为便于计算,这里选用的时钟驱动频率为10 MHz,因此每个时钟周期(也是MEGA16的指令周期)即为100 ns,这样只要保证在每个指令周期内按要求对每个端口进行赋值,即可实现AVR单片机的各个端口对所需波形的要求,当然也可以选用频率更高的晶振作为驱动,这样的话每个指令周期的时间得根据所选择的晶振周期进行分配,在每个指令的周期内进行对端口赋值即可实现要求的波形。图4中RESET端接的是复位电路,实现上电复位的功能。按图4所示的接线方式,PA0~PA5出现的依次是SH、Φ1、Φ2、SP、RS和CP,即驱动CCD的各个信号。

图4 线阵TCD2252D驱动电路的Proteus设计电路图

利用AVR单片机来进行驱动电路的设计,主要是考虑驱动频率的问题,TCD2252D要求的驱动频率最高为1 MHz(MEGA16单片机的大多数指令为单个的系统时钟周期,系统时钟最高频率可以提高到16 MHz,这是它与51单片机的最大区别所在),我们选择10 MHz作为它的时钟周期,这样的话就能保证在100 ns的窄脉冲要求。在确定好利用AVR单片机后,具体到脉冲信号的产生又有两种不同的方案,即利用MEGA16的3个定时/计数器实现自动的定时,且MEGA16的计数器有3个,2个8位的T/C0和T/C2,1个16位的定时器T/C1,均能实现脉冲宽度调制PWM(Pulse Width Modulation),这样可以利用T/C1来产生SH,T/C0和T/C2分别产生Φ1和SP,通过对单片机定时器写入相应的控制字即可实现。这种方案的优点是操作不占用CPU的时间,但缺点也很明显,高电平部分不容易产生,驱动信号为6路,因此必须依靠附加的外部IC来调整以满足要求,这样无异于利用IC搭建电路,只不过是1400计数器利用单片机代替。另外一种思路是直接依靠程序的不停循环来实现驱动信号的输出,这种方案的缺点是一直占用了CPU的操作时间,但优点也很明显,直接利用单片机就可以实现驱动,无需附加任何外部设备。

利用编程的方法实现驱动电路的产生,关键的是要实现在光生电荷累积阶段和光生电荷转移阶段(暂称为普通周期和高电平周期),这样的话分别用两个循环语句控制两个不同周期的输出,利用一个变量X赋初值为1400,每个普通周期减1,当它小于零时即跳转到高电平周期中执行,在高电平周期又对X赋值1400即可实现循环。MEGA16有32个寄存器,因此可以利用17~25来存储其中的9个状态的值,利用R27-R26组合实现一个16位计数器的功能,部分程序如下:(普通周期循环部分)各个寄存器对应值及在周期中的值如图5所示。

图5 各个寄存器对应值及在周期中的值

loop1:out porta, r17;对应起始

r17=0b00110010,其余同理可得:

out porta, r28;PA0输出SH

out porta, r18;PA1输出Φ1

out porta, r28;PA2输出Φ2

out porta, r19;PA3输出SP

out porta, r28;PA4输出RS

out porta, r20;PA5输出CP

ld r30, -X;16位计数器r27-r26每一个周期减1

subr27, r29;r29=0,相当于与零比较,在下个周期进行判断跳转

out porta, r21

out porta, r20

out porta, r22

out porta, r20

out porta, r23

out porta, r20

out porta, r28

breq loop2;brne、breq负责积分周期的跳转brne loop1

高电平周期同理可得对其进行赋值,注意普通周期中是比较r27与零的大小,因此在赋值时应赋为:r26=0b01111000,r27=0b00000110。(说明:2800转换成二进制为101011110000B,原本r27=0b00000101,当综合考虑后依上述进行赋值),可以参考以上程序写出。

4 仿真与实际驱动电路实验结果

利用Multisim进行仿真的实验结果如图6所示。

图6 利用Multisim进行仿真的实验结果

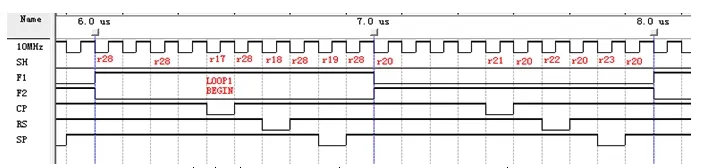

利用Quartus II进行仿真的实验结果如图7所示。

图7 利用Quartus II进行仿真的实验结果

利用Proteus进行仿真的实验结果如图8所示。

图8 利用Proteus进行仿真的实验结果

针对利用IC分立元件搭接的面包板实际电路效果,利用Tektronix四通道彩色示波器进行截图结果如图9所示。

针对利用FPGA开发板的实际电路效果,利用Tektronix四通道彩色示波器进行截图结果如图10所示。

图9 利用IC分立元件搭建面包板实际电路的实验结果

图10 FPGA开发板实际电路的实验结果

针对利用AVR单片机的实际电路效果,利用Tektronix四通道彩色示波器进行截图结果如图11所示。

图11 AVR单片机实际电路的实验结果

在实际测试中,在CH1通道信上,线阵CCD输出波形如图12所示。

5 结语

从以上几种方案的设计过程来看,从最初的方案设计、仿真到最终的电路实现,EDA软件在其中起着不可或缺的作用。IC电路设计复杂,偏重于硬件实现,调试相对困难,灵活性差。FPGA的设计是基于IC电路,因此较为简单,但需要有前期IC设计

图12 线阵CCD的输出波形

的准备。AVR单片机的实现相对较为简单,偏重于软件的编程,只需按所需要的驱动脉冲波形对端口进行连续的赋值即可实现,但需要掌握汇编语言等。综上,本实验课程所给出的TCD2252D驱动电路设计修改时序相对简单,移植较为容易,具有较高的实用价值,同时能帮助熟悉线阵CCD驱动电路的设计。

[1] 王庆友. CCD应用技术[M]. 天津: 天津大学出版社.

[2] Franceschini, N. Small brains, smart machines: from fly vision to robot vision and back again[J]. Piscataway, USA: Proceedings of the IEEE, 2014, 102(5): 751-781.

[3] Liu, Yan, Yu, Feihong. Automatic inspection system of surface defects on optical IR-CUT filter based on machine vision[J]. Oxford, England, UK: Optics and Lasers in Engineering, 2014, 55: 243-257.

[4] Ali, MH, Kurokawa, S, Uesugi, K. Camera based precision measurement in improving measurement accuracy[J]. Oxford, England, UK: Measurement, 2014, 49, 138-147.

[5] 黄彤津, 朱礼尧, 迟涵文, 等. 基于CPLD的线阵CCD驱动电路的设计[J]. 北京: 电子测量技术, 2014, 37(7): 66-70.

[6] 刘月林, 诸葛晶昌. 一种光积分时间可调的线阵CCD驱动设计[J]. 南京: 工业控制计算机, 2013, 26(12): 100-101.

[7] 刘燕, 张会生, 王靖. 基于FPGA的TDICCD8091驱动时序电路设计[J]. 西安: 现代电子技术, 2013, 36(17): 165-167.

[8] 张亮, 刘润民. 可配置的通用线阵CCD驱动电路的研究与设计[J]. 北京: 电子技术应用, 2013, 39(12): 55-67, 60.

[9] 李宁宁, 李志农, 刘治华, 等. 基于CPLD的线阵CCD驱动电路的设计[J]. 沈阳: 机械设计与制造, 2011, 6: 30-32.

[10] 谭露雯, 李景镇, 陆小微, 等. 基于CPLD工作模式可调的线阵CCD驱动电路设计[J]. 西安: 光子学报, 2010, 39(3): 436-440.

Teaching Application of the Designing of Linear CCD Driving Circuit with EDA

ZHU Shi-ping, ZHOU Fu-qiang, LIU Hui-lan, ZHANG Yong-jian

(SchoolofInstrumentationScienceandOptoelectronicsEngineering,BeihangUniversity,Beijing100191,China)

CCD (Charge Coupled Device) is a kind of wildly used solid imaging device, one key problem of CCD application is the design of the driving circuit. The undergraduate course for the CCD driving circuit designing is offered based on the computer aid design, which can help undergraduate students to improve their knowledge of analog circuit and digital circuit. This paper proposes several design schemes for the linear CCD driving circuit of TCD2252D by using EDA software.

CCD; design of driving circuit; FPGA; Proteus

2016-08-11;

2017-07- 14

北京航空航天大学2015年校级教学改革项目。

祝世平(1970-),男,博士,副教授,主要从事图像处理和视频压缩等方面的教学和研究,E-mail: spzhu@163.com

TN949.12

A

1008-0686(2017)04-0092-05