基于65nm高速SRAM全定制设计

2017-09-06贾柱良裴国旭

贾柱良 杜 明 兰 韬 裴国旭

(深圳市国微电子股份有限公司,广东 深圳 518057)

基于65nm高速SRAM全定制设计

贾柱良 杜 明 兰 韬 裴国旭

(深圳市国微电子股份有限公司,广东 深圳 518057)

工艺进入65nm后,芯片集成度越来越高,器件的尺寸原来越小,加上走线宽度的减少,互连寄生效应越来越大,对SRAM的性能的影响也愈加显著。本文从全定制的设计流程出发,介绍了怎样实现SRAM不同功能模块之间的版图布局和IP的设计。在保证模块性能的同时,减少互连寄生对SRAM的影响,保证SRAM的高速运行。

SRAM;全定制;版图;高速

1 引言

随着半导体加工技术的进步,CMOS器件尺寸不断减小,从而大大提高了器件的集成度和电路的速度,降低了成本。但是伴随着器件尺寸的减小,一些新的问题慢慢出现,这些新的问题给电路设计带来了新的挑战。第一,电路的漏电流增加,这主要包括两个方面:一是沟道变短,阈值电压降低,亚阈值漏电流增加;二是门绝缘层变薄,栅氧化层隧穿电流增大,漏电流的增加使得逻辑电路的静态功耗大幅度增加,并逐渐超过了动态功耗。第二,当器件尺寸缩小后,电路设计中必须要考虑阻容迟滞而引起的信号传播延迟,线间干扰以及功率耗散等问题。第三,器件尺寸缩小,随机掺杂波动愈加严重,导致阈值电压的波动越来越大,在电路设计中必须考虑这种波动,增加设计裕量[1]。

工艺尺寸的缩小,互连线的长度、宽度及线间距也越来越小,导致互连线的寄生效应(电容、电阻及电感)越来越严重,它会影响信号的完整性并降低电路的性能。对于大容量的SRAM,它的很多信号线会跨越整个存储体,具有很大的线负载[2]。

因此,对于65nm SRAM设计来说,如何绘制底层IP以及进行一个合理的布局,来减少器件之间的互连延迟,保证芯片的高速运行对于芯片的性能来说至关重要。本文,从版图的全定制设计流程出发,介绍了怎样实现底层模块的版图优化、整个芯片的模块布局以及电源地规划,从而保证SRAM的高速运行。

2 芯片布局

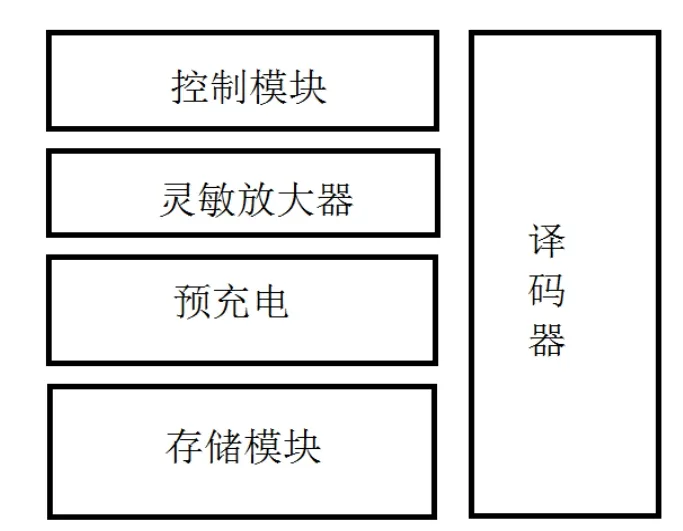

SRAM主要是由存储模块、灵敏放大器、多路选择器、译码电路以及控制电路构成。模块的布局,考虑SRAM各个模块之间的互连关系尽量在最小的面积内保持所有模块的拼接。整个芯片的布局尽量保持正方形,这样能够减小应力对芯片的影响。其次,要求我们考虑不同模块之间连线带来的寄生效应的影响,减小互连走线的距离和增加通孔的数量。

图1 SRAM内部模块排布

3 IP设计

3.1 存储模块

一个好的存储模块需要保证在尽量小的面积内能够存储的容量尽可能大。我们采用标准的6 TCMOS存储单元来设计。芯片总容量为128K16,采用了8个容量16K16的模块构成,在版图中SRAM128K16是将8个SRAM16K16垂直排列,分成上下两组如图2所示。每组存储容量为64K,总的输出在两组64K的中间,也是基于一个信号的平衡考虑。SRAM16K16由4个SRAM4K16构成如图3所示。4个SRAM4K16面对面摆放,构成一个正方形,逻辑控制模块在中间,而输入输出则是统一在中下部,这是为了后期方便连线。

图2 SRAM 128K16

图3 SRAM16K16

3.2 灵敏放大器

SRAM存储单元在读出操作时,仅能输出很小的能量,随着工艺尺寸的缩小,走线带来的寄生电阻和电容对信号的影响会使得其衰减更加严重,这样大大降低了SRAM运行的速度。采用灵敏放大器通过放大了数据的有效输出信号,对于加快SRAM读取速度和稳定输出有着重要的意义。

灵敏放大器电路架构为经典电压型结构。电路结构如图4所示,第一级为电平转换,第二级与第三级电路进行逐级放大。由于灵敏放大器要实现良好的抗噪性就必须要求差分对管和有源电流镜之间失配尽量小。版图上输入对管如图5所示,采用共质心匹配的方式,源漏方向保持一致,差分的输入输出走线的环境分别保持一致,而且尽量减少串扰。在输入对管两边增加接地DUMMY管。由于工艺进入深亚微米后,版图设计要考虑二级效应的影响,其中WPE LOD效应对MOS管的电学特性和器件的匹配有着重要的影响。WPE效应是由于在离子注入工艺时,原子从掩模板的边沿开始侧向散射,并且嵌入到在阱边沿相邻的硅表面。结果就是,阱表面浓度会随着距离掩模板的边沿的远近而有所不同,因此整个阱的掺杂浓度是不均匀的。这种侧面的不均匀的阱掺杂浓度会造成MOS管阈值电压和其它电学特性的改变。LOD效应是由于STI应力对于MOS管的影响,不同的diff长度产生的不同机械应力导致器件性能(阈值电压和饱和电流)受到影响。所以我们将匹配器件的源漏尽量合并,并添加DUMMY来增大SA、SB以及PMOS管到井边界的距离,减小纳米级工艺二级效应的影响。

图4 灵敏放大器电路架构

图5 输入对管版图示意图

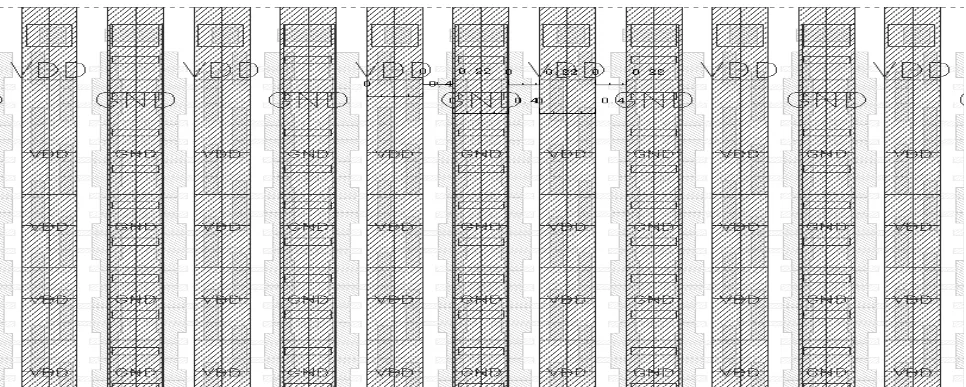

由于电路结构采用一个灵敏放大器对应16个Bitcell和16个预充电模块,所以版图上采用1个灵敏放大器的宽度与16个Bitcell一致。

灵敏放大器的仿真结果如下所示:后仿真将灵敏放大器采用后仿网表,其它模块仍保持与前仿真相同条件,位线压差、位线放电时间与前仿基本没有差别,对灵敏放大器整体读取时间进行了仿真。

图6 后仿灵敏放大器工作速度(VDD=1.2V,tt,25℃)

表1 后仿corners下灵敏放大器工作时间(单位:ns)

从前后仿真结果来看,在各corners下位线压差在80mV~290mV范围内变化,灵敏放大器工作速度在0.768~2.182ns之间,最慢情况出现在ss、1.08V、-55℃情况下。通过以上仿真结果和分析可以看出,灵敏放大器的版图处理可以满足整体电路需求,符合设计指标。

1.8.1 中医临床表现 治疗前、治疗4周末、治疗8周末及治疗12周末,分别对非透析CKD-MBD患者记录1次中医临床症状及体征变化情况,并且根据症状量化评分标准记分。

3.3 预充电模块

预充电路是存储器的重要组成部分,SRAM预充单元在读写SRAM之前把SRAM单元的两个互补数据位线拉高到一高电平:第一保证存储单元的数据不被破坏;第二,由于存储单元管子驱动能力较小,而位线寄生电容很大,存储单元直接驱动位线会很慢,对位线预充电后,再对某一位线放电可以提高对SRAM的访问速度[3]。如图7,单个预充电单元的宽度与单个Bitcell的横向宽度相匹配,两单元上下的位线B和BB完全对接。如图8所示,16个预充电单元组成的预充电模块,对应匹配一个灵敏放大器,可以保证布线不会浪费,从而不引起功耗增大、延时增加。

图7 单个预充电模块

图8 预充电阵列

3.4 译码器

译码电路在芯片中占用面积仅次于存储模块面积。它对SRAM的速度和功耗有着很大的影响。随着存储器容量的增大,译码电路的延时占总延时的比例也越来越多[4]。单个译码器单元的IP设计,版图如图9所示,我们根据单个Bitcell的宽度来设计,这样通过在一个Bitcell横向布线通道内,交叉摆放2个译码单元,可以实现两个译码单元与左右Bitcell之间字线的匹配对接。译码器的TOP直接与矩形的SRAM左右相连,其高度与SRAM单元的高度完全匹配,可以保证布线不会浪费,从而不引起功耗增大、延时增加。

图9 译码单元版图

4TOP拼接

4.1 电源地的布局

随着工艺尺寸的减小,进入65nm后,由于芯片晶体管的数量越来越多,集成度越来越高,对于电源地的供电要求越来越高。电源地网络供电不足,会导致芯片的IR DROP过大,对芯片的性能产生影响。同时,也会导致芯片在电源地的薄弱处存在EM风险,引起芯片失效。

由于SRAM的存储单元、灵敏放大器等模块对电源非常敏感;同时,存储器翻转斜率达到纳秒级,瞬态开关功耗非常大,对电源系统提出了较苛刻的要求;所以如图10所示,我们在SRAM单元中power mesh是0.22um的M4作为供电网络,保证供电稳定,同时还作为一个电源地平面隔离噪声。在设计IP的周围均匀地插入电源地decap电容,响应高频和峰值电流,这样能够减少电源地之间纹波和噪声对SRAM的影响。

图10 power mesh

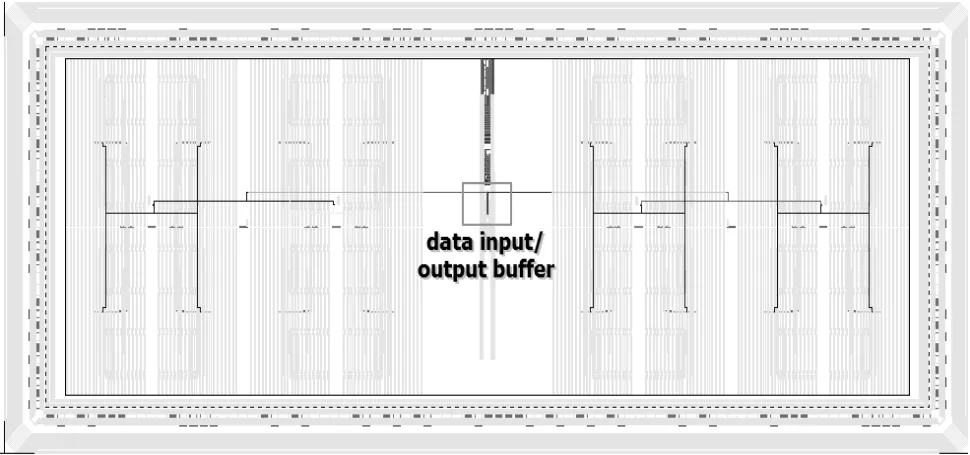

4.2 芯片总体版图

版图如图11所示,考虑到CORE与IO之间信号线的互连对SRAM的影响,所有的地址、数据、控制的进出都集中在中间,然后通过顶层线往两边的存储体输送,两种颜色的交点为插入buffer,这样能尽可能保证信号到每一个存储体的时间是相等的,这种布线方式可以使信号的延时最小,提高存储速度。

IO除了保证电源地的供电外,考虑芯片整体的ESD设计,尽量减小电源地的环路阻抗。CORE采用M5 M6 TM1 TM2的power stripe交叉排布的方式,保证内核的供电需求,结果证明设计满足要求。

图11 芯片概貌图

5 总结

本文从65nm工艺出发,考虑到工艺带来的二级效应和互联寄生对SRAM速度的影响。根据SRAM的电路特性,提供了一个合理的全定制解决方案,经流片验证速度达到预期要求。

[1]张强.65nm SRAM的设计[D].杭州:浙江大学.2010.

[2]温亮.65nm工艺高性能SRAM的研究与实现[D].长沙:国防科技大学,2011.

[3]井源.65nm工艺下L1Cache tag中高速SRAM的设计与实现[D].长沙:国防科技大学.2010.

[4]刘其龙.基于65nm高性能SRAM关键电路的研究与设计[D].合肥:安徽大学.2013.

Full Custom Design of High Speed SRAM Based on 65nm

Jia Zhuliang Du Ming Lan Tao Pei Guoxu

(Shenzhen State Microelectronics Co.,Ltd.,Shenzhen 518057,Guangdong)

As the technology minimum size reaches to 65nm,the chip integration is more and more high,the size of the device is smaller and the width of the line is also reduced.Because of these factors,the parasitic effect is larger and becomes more important to SRAM.This article uses the full custom design flow,introduces how to realize SRAM using different function module layout and IP module.It reduces the impact of interconnect parasitic and guarantees the high speed running of SRAM.

SRAM;full custom design;layout;high speed

TP333

A

1008-6609(2017)07-0044-04

贾柱良(1979-),男,湖南永州人,硕士研究生,工程师,研究方向为集成电路设计。