高速并行调制器的设计与实现

2017-08-08王建新

李 然,王建新

(南京理工大学 电子工程与光电技术学院,江苏 南京210094)

高速并行调制器的设计与实现

李 然,王建新

(南京理工大学 电子工程与光电技术学院,江苏 南京210094)

为了提高高速调制器的处理速率,给出了一种高速并行调制器的设计方案。该方案将差分编码、成形滤波等处理模块全部转化为并行结构,从而在系统主时钟频率受限的情况下进一步提高了处理速率,并对这些功能模块的实现结构进行了优化,以减少资源消耗,便于FPGA实现。测试结果表明,该方案能够显著提高调制器的处理速率。

高速;并行结构;调制;FPGA

随着信息技术和通信技术的发展,人们对信息传输速率的要求越来越高,如对高清电视、视频会议等服务的需求日益高涨,从而对调制解调这一制约传输速率的环节提出了更高的速率要求。传统的高速调制解调器多为高速模拟调制解调器。随着数字芯片处理速度的不断提高,可靠性更高、灵活性更大的高速数字调制解调器得到了越来越广泛的应用[1-3]。

而高速数字调制解调器的速率仍会受限于其所采用的数字信号处理芯片的最高处理速度。在诸多数字芯片中,FPGA的处理速度最快,常用于高速信号处理领域。而FPGA的处理速率主要受限于其主时钟频率。若采用传统的串行调制技术就难以突破主时钟频率对调制速率的限制。若想进一步提高调制速率,就必须先将高速数据分流到各个支路以降低速率,其后采用并行结构进行处理[4-6]。

文中对差分编码、成形滤波等各个调制步骤的并行处理算法进行了研究,将这些模块转化为并行结构,从而在时钟频率受限的情况下提高了处理速率,并对这些结构进行了深度优化,以减少资源消耗,便于FPGA实现。

1 高速并行调制器

为了在符号速率一定的情况下传输更多的信息,高速调制解调器一般采用较高阶的调制方式进行调制。但越高阶的调制方式对信道特性和信噪比的要求也越高,因此需要在传输速率与误码率性能之间进行权衡。目前投入使用的高速调制解调器多采用QPSK调制。但随着高速通信系统对传输速率及传输带宽要求的不断提高,QPSK这样的低阶调制越来越难以满足需求。如今MQAM、MAPSK等更高阶调制得到了越来越多的研究和应用。文中选择了16QAM作为调制方式,这种调制方式能够很好地兼顾传输速率和误码率性能,很适合应用于高速调制解调中[7-9]。

采用并行结构时,若并行的路数越多,处理速率相应就越高,但同时实现的复杂度也越高,资源消耗也就越大。另外,成形滤波时内插的倍数会影响后续并行的支路数,从而也会影响资源消耗的情况。本文选择了8路并行,4倍内插的结构进行实现,以平衡处理速率与资源消耗。

高速并行调制器的设计框图如图1所示。具体过程为:1比特的高速输入数据流经高速FIFO缓冲后以4比特为一个单位,分流到8个支路上,然后对8个支路上的数据进行并行差分编码,并行映射,内插,并行成形滤波和并行上变频,最后由高速FIFO并串转换为一路输出。其中并行映射模块实现较为简单,由于映射的结果只依赖于本支路当前的输入值,不需要考虑其它支路,因此只需将串行的映射模块复制到各个支路即可。

图1 高速并行调制器设计框图

2 并行结构设计与优化

并行结构可以在时钟频率受限的情况下,提高处理速率。但并行结构需要考虑各个支路之间的相互影响,因此需要研究相应的并行实现算法。另外并行实现结构的资源消耗很大,还需对各个模块进行优化以尽可能降低资源消耗。下面将讨论各个模块的并行实现结构及优化方法。

2.1 并行差分编码

16QAM信号具有四相相位模糊,因此需要采用差分编码来解相位模糊。又因为限定每个符号所在象限的只是前两比特数据,所以只需对前两比特数据进行差分编码即可[10]。因此中国广播电影电视行业标准(GY/T 170-2001)[11]里建议对QAM信号进行如下方式的差分编码:

式中 Ak,Bk为编码前符号的高两位,Ik,Qk为编码后符号的高两位,⊕为模2加。

由编码公式(1)(2)可以看出,当前的编码结果Ik,Qk不仅依赖于当前的输入值Ak,Bk,还依赖于上一次编码结果Ik-1,Qk-1。但在并行调制时,因为输入值是并行输入的,除第一条支路外的各支路都要先等待各自上一路的编码结果算出才能进行编码。在时钟频率受限的情况下,除第一条支路外的各支路就来不及处理后续的输入数据了。

为解决这一矛盾,就需要由编码公式(1)(2)推出一个并行编码公式,在该并行编码公式中,各个并行支路当前的编码结果须仅依赖于当前的输入值和已计算出的编码结果。这样才能完成并行差分编码。下面将对此进行推导。

记编码函数为f(X,Y),其中X表示上一次编码结果即(Ik-1,Qk-1),Y 表示当前输入值即(Ak,Bk)。f(X,Y)为当前的编码结果即(Ik,Qk)。该函数具体映射关系如表1所示。

表 1 f(X,Y)映射表

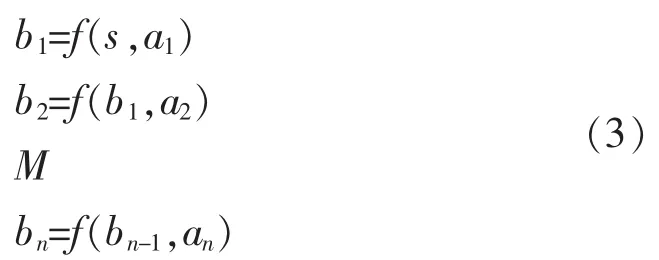

Y第n个输入值为an,第n个编码结果为bn,差分编码的初始值为s。则各个编码结果为:

由式(3)中各式迭代可得:

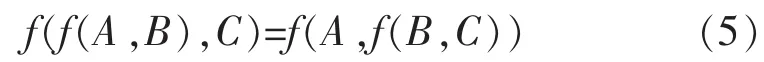

为了对式(4)进行化简,需要先证明如下等式:

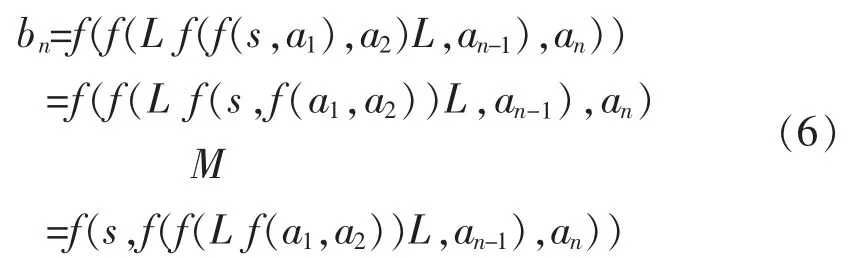

使用Matlab枚举的值,再根据表1分别计算等式两边的结果,发现始终相等,由此证得等式成立。根据式(5)可对式(4)进行如下化简:

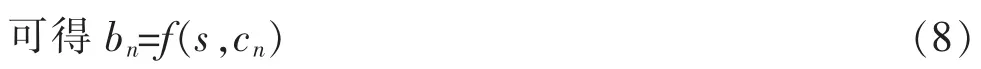

由表 1 易得:f(00,B)=B 所以

令 cn=f(f(L f(f(00,a1),a2)L,an-1),an)代入式(7)

由式(8)可知,以s为初始值对an进行编码得到的结果bn与以00为初始值an对进行编码得到的结果 cn之间存在映射关系 bn=f(s,cn)。因此只需以 s为上一次编码结果对cn再进行一次映射即可得到bn。由此本文提出了一种差分编码的并行实现结构。图2为8路并行时并行差分编码的实现结构框图。每个时钟周期输入的8路数据先以00为初始值进行编码,在输出前再以上一次并行编码的第8路输出结果为上一次编码结果再映射一次,就实现了并行差分编码。

图2 差分编码的并行实现框图

图中映射模块表示编码函数f(X,Y),从其上输入端输入的值为X,即上一次编码结果,下输入端输入的值为Y,即当前输入值。

2.2 并行滤波

并行滤波有两种实现结构,即时域并行滤波和频域并行滤波。

时域串行滤波的公式为:

式中,xn为输入,hi为滤波器系数,yn为输出。

则L路并行滤波时,滤波器第j路的第k个输出为:

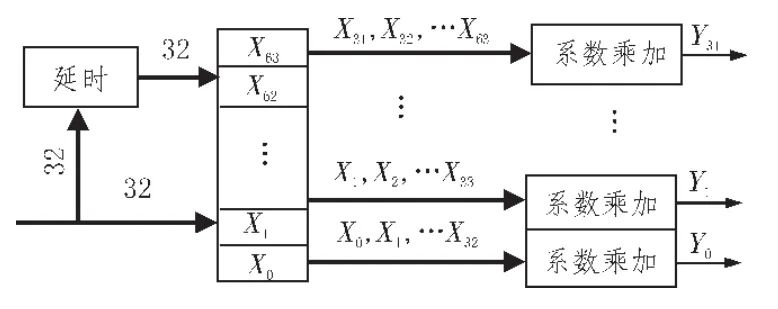

由式(10)可知,时域并行滤波各支路的输出都由M个输入与滤波器系数相乘再累加得到。图3为32路并行滤波,滤波器为33阶的情况下时域并行滤波的实现框图。

图3 时域并行滤波实现框图

频域并行滤波,需先通过DFT变换将多路并行信号转换到频域上,通过重叠保留法或重叠相加法来实现分段处理,再在频域上乘以相应的频域滤波系数来实现滤波,最后经IDFT变换将信号再转换回时域。

由上文可知,时域并行滤波未经优化共需进行33×32×2次乘法。首先,由于滤波前进行了4倍内插,即每4位数据中有3位为0,不需要进行计算。考虑到这一点,实际只需进行(3×8+9)×8×2=33×8×2次乘法。其次,本文选用的滤波器系数是对称的,因此又可节省一部分乘法器,据此优化后只需进行25×8×2次乘法。最后,由于在后续的上变频操作中选取了特殊的本振,使得I/Q两路的滤波器输出有一半用不到,根据这一情况,可对I/Q两路的滤波器分别进行优化,又可减少一半的乘法器。最终时域并行滤波只需进行25×8次乘法。而频域并行滤波经优化后仅IFFT就至少需进行352次乘法,所以频域并行滤波比时域并行滤波所需进行的乘法次数多得多。

因此本文采用时域并行滤波结构以降低资源消耗。

2.3 并行正交上变频

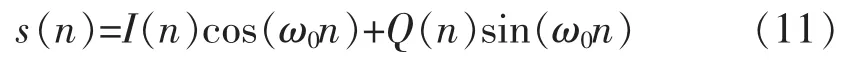

正交上变频公式如下:

则L路并行时,并行正交上变频公式如下:

可见并行正交上变频,就是将各个支路的调制信号与对应的载波幅度值相乘。显然如果载波频率与采样频率为整数倍关系的话,那么各个支路要乘上的载波幅度值就是一定的,这样可降低结构的复杂度,方便FPGA实现。因此可设置载波频率为采样频率的1/4。

为了避免进行乘法以进一步节省资源,载波的4 个点可选取(1,0,-1,0)这 4 个点去与成形滤波器输出相乘。这样只需将输入的32路并行I/Q信号的某些路取反,某些路延时,其余路清零即可,完全不需要使用乘法器。若载波幅度不设为1,则应选择2的整数次幂,这样就可通过移位来进行乘法,以避免使用乘法器。另外由于载波信号的I路与Q路正交,即载波的I路为±1则Q路为0,Q路为±1则I路为0,因此上变频后的输出必然只与I/Q两路中的一路有关,公式中的加法运算也不需要进行。这样选取载波上的点可以大大减少资源消耗。具体实现框图如图4所示。

图4 并行正交上变频实现框图

3 实验测试

测试系统的架构如图5所示,具体过程为:由Matlab产生一段随机数,加载到ROM中,循环读出作为调制器的输入,经高速并行调制器调制后,使用在线调试软件Chipscope通过JTAG接口将输出信号读出。再在Matlab中对输出信号进行解调,并与输入信号进行对比。测试的硬件平台为Xilinx公司的ML605开发板,可提供最高700 MHz的时钟[14-15]。

图5 实验测试框图

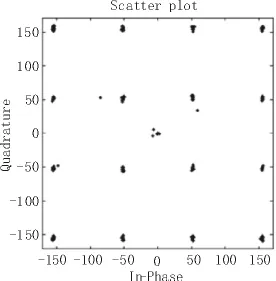

若输入时钟频率为600 MHz,即比特速率为600 Mbps时,系统可正确实现调制功能,解调得出的星座图如图6所示,图中各点非常集中显示调制性能良好。若输入时钟频率提高至700 MHz,也可正确实现调制功能,但解调出的星座图中点更分散,性能较差。

图6 输入时钟频率为600MHz时解调星座图

理论上,该方案可在系统主时钟频率一定的情况下,将调制速率提高到传统串行调制器最高速率的32倍。但由于测试中采用的FIFO难以满足那么高的输入输出时钟频率要求,限制了处理速率的提高。若直接并行输入输出,则可进一步提高处理速率。经实验测试表明,直接并行输入输出时,可将主时钟频率提高至100 MHz,理论上对应比特速率为3.2 Gbps,调制器仍然能正确调制,且性能良好。因此若能采用专门的高速输入输出FIFO即可实现更高的处理速率。

4 结束语

文中研究了调制过程中各个步骤的并行实现算法,从而将各个处理模块转化为了并行实现结构,突破了FPGA[16-17]主时钟频率对调制器处理速率的限制,进一步提高了调制器的处理速率,并对各个处理模块进行了深度优化,减少了资源消耗,且便于FPGA实现。测试结果表明,该方案能够显著提高调制器的处理速率。

[1]许鹏.基于FPGA全数字超高速MPSK解调技术研究[D].北京:清华大学,2010.

[2]王俭.QPSK全数字中频调制解调器的FPGA实现[D].西安:西安电子科技大学,2013.

[3]李玲.QDPSK全数字调制解调技术研究[D].南京:南京理工大学,2014.

[4]曾辉.基于全数字高速并行接收结构APRX的解调技术研究[D].成都:电子科技大学,2013.

[5]陈晖,易克初,李文铎.高速数字解调中的并行处理算法[J].电子科技大学学报,2010,39(3):340-345.

[6]林长星.2Gbps高速通信解调技术及其实现研究[D].北京:清华大学,2012.

[7]胡俊杰.卫星数据传输高速调制器关键技术研究[D].北京:中国科学院研究生院,2011.

[8]房晓飞,刘毓,梁猛.16QAM相干光检测OFDM系统性能研究[J].电子设计工程2015,23(7):189-192.

[9]周钦.星载高速高阶QAM调制技术设计与实现[D].西安:西安电子科技大学,2014.

[10]杜勇.数字调制解调技术的MATLAB与FPGA实现[M].北京:电子工业出版社,2014.

[11]国家广播电影电视总局.中华人民共和国广播电影电视行业标准GY/T 170-2001.有线数字电视广播信道编码与调制规范[S].北京:国家广播电影电视总局,2001.

[12]刘策伦,安建平,王翠莲,等.联合符号同步的低复杂度频域并行解调结构[J].空间电子技术,2013(2):17-19.

[13]Sanjit K.Mitra.数字信号处理—基于计算机的方法[M].4版.余翔宇,译.北京:电子工业出版社,2012.

[14]Xilinx.LogiCORE IP ClockingWizard[EB/OL].[2011-03-01].http://china.xilinx.com/support/documentation/ip_documentation/clk_wiz/v3_1/clk_wiz_ds709.pdf.

[15]Xilinx.ML605 Hardware UserGuide[EB/OL].[2012-10-02].http://www.xilinx.com/support/documentation/boards_and_kits/ug534.pdf.

[16]郎宝华,单成刚.无刷直流电机的FPGA控制系统设计及仿真 [J].西安工业大学学报,2014(2):160-166.

[17]汪鹤,王劲松,张道农.基于FPGA的智能变电站二次设备曼彻斯特编码同步研究[J].电力信息与通信技术,2015(4):26-29.

Design and realization of high-rate parallel modulator

LI Ran,WANG Jian-xin

(School of Electronic and Optical Engineering,Nanjing University of Science and Technology,Nanjing 210094,China)

In order to improve the processing rate of high-rate modulator,a design scheme of high rate parallel modulator is presented.The scheme transforms all processing modules such as differential coding and shaping filter into parallel structure to improve the processing rate further in the condition of the frequency of system major clock restricted,and optimizes the implementation structure of each function module to reduce the consumption of resources and be easy to the FPGA implementation.The test result indicates that the scheme can improve the processing rate of the modulator significantly.

high-rate;parallel structure;modulation;FPGA

TN914

:A

:1674-6236(2017)13-0099-05

2016-05-25稿件编号:201605244

李 然(1991—),男,江苏淮安人,硕士研究生。研究方向:高速调制解调技术。