星务管理中的双CPU冗余通信设计与实现

2017-08-08李华旺

吕 聪,李华旺,常 亮

(1.中国科学院 上海微系统与信息技术研究所,上海 200050;2.上海微小卫星工程中心 上海 201203)

星务管理中的双CPU冗余通信设计与实现

吕 聪1,2,李华旺1,2,常 亮1,2

(1.中国科学院 上海微系统与信息技术研究所,上海 200050;2.上海微小卫星工程中心 上海 201203)

基于Cortex-M3的Smart Fusion2芯片和APA600芯片结合双CPU冗余技术设计实现了微纳卫星星务管理中的双CPU冗余通信。采用双CPU冗余技术来提高系统的可靠性。在信息交互设计中加入看门狗实现CPU状态监控,通过信息发送中握手通信机制的设置以及链路自复位的设置进一步提高系统的可靠性。详细介绍了双CPU冗余通信在星务管理系统中的实现并介绍了链路可靠性设计和双CPU通信过程中的重要函数设计。利用可靠性高的串行通信方式设计双CPU冗余通信即满足微纳卫星对可靠性的高要求又降低了开发而且实现简单这对于卫星系统中的通信有较好的实用价值。

双CPU;冗余通信;监控;可靠性

随着信息技术与小型化技术的飞速发展与应用,传统的卫星研制技术出现了革命性的飞跃。其中一个重要发展趋势是卫星小型化[1],小卫星实现了低成本、小重量、小体积、高性能、短研究周期等特点[2]。卫星越来越小,但对可靠性的要求越来越高。文中设计基于微纳卫星星务管理系统,根据微纳卫星的高可靠性设计要求,以及一个单CPU的控制系统很难满足现代控制系统的要求[3]的现状,选用了双CPU的冗余控制技术。由于双CPU的冗余控制是一种提高系统可靠性的有效手段[4],设计为了适合卫星可靠性要求选用双CPU冗余通信。双冗余技术就是在系统中增加备用模块,一旦工作模块发生故障时,控制系统可以快速切换到备用模块,从而保证了系统的正常工作[5]。其中如何通过双CPU通信保证系统的可靠性是本文的一个研究重点。

1 芯片选型

1.1 Smart Fusion2芯片介绍

主CPU选择Microsemi公司Smart Fusion2SoC FPGA芯片(以下简称SF2),该芯片设计用于满足高安全性、高可靠性和低功耗的基本需求。采用了基于非易失性快闪技术的设计保护功能,易于保护机密和高价值的设计,防止篡改、克隆、过度建造、反向工程和伪造。SF2芯片采用Flash工艺实现,无需额外的配置存储器以及刷新电路。同时SF2芯片上电即行,没有上电加载时间,提高了卫星启动时间。SF2在单一芯片上集成了固有可靠性的快闪FPGA架构、一个 166(MHz)ARM CortexTM-M3 处理器、先进的安全处理加速器、DSP模块、SRAM、eNVM和业界所需的高性能通讯接口。SF2器件具备所需的差异化特性,能够确保在非常低的功耗下安全、可靠地运行。

1.2 APA600芯片介绍

从CPU选择的是APA600芯片,APA600芯片是抗辐射的宇航等级的芯片。其相对于SF2有更高的可靠性但是它在功耗响应速度等方面却没有Smart Fusion2出色,所以选择用高可靠性低性能的APA600来监测高性能但可靠性相对差一点的SF2以使得整个系统的设计更加可靠并实现提高系统性能的目标。

2 双CPU冗余通信设计

2.1 双CPU冗余通信方式选择

双CPU间的通信方式有并行通信方式和串行通信方式。串行通信传送按位顺序进行,传输线少,成本低但传送速度慢。但随着当前通信行业的迅猛发展,串行通信技术日趋成熟,传输速率越来越快,可以进行长距离数据传输并保证信号传输质量,加之其线路设计简单,能很好地满足保护装置的通信要求,因此已经越来越多的应用于双CPU间的通信[6]。而异步串行通信也由于接线少、传输距离远、可靠性高、成本低等特征在数据采集和控制系统中得到了广泛的应用[7-8]。

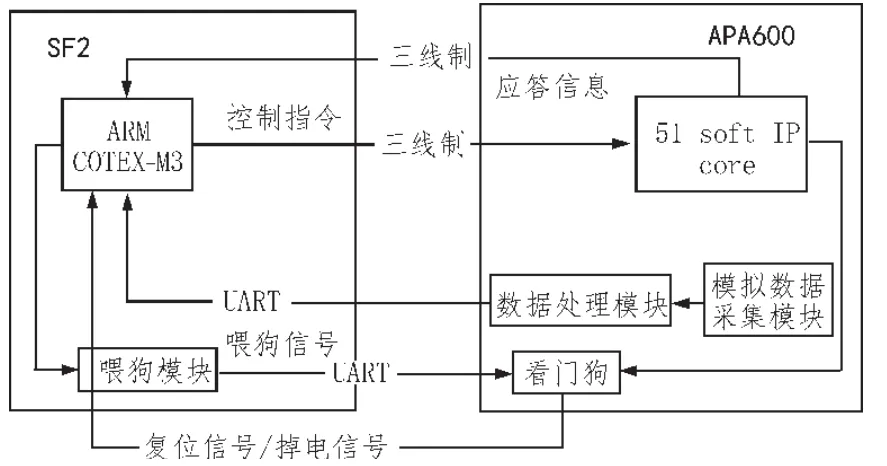

考虑到数据量不是特别大,采用串行通信方式,并采用三线制和UART作为传输链路。其中UART发送信息是将需要发送的并行数据转化为适合在信道中传输的串行数据串行输出,接收时接收串行数据,并将其转化为并行数据[9-10]。SF2通过三线制向APA600发送控制指令,APA600接收到控制指令后通过三线制向SF2返回应答信息并且通过UART向SF2返回数据信号,SF2定时通过UART向APA600发送喂狗信号。为了避免UART和SF2的接收和发送数据时使CPU处于等待状态,接受和发送均采用中断模式[11]。其基本的通信连接如图1所示:

图1 双CPU通信连接图

2.2 双CPU冗余通信控制实现

这里的双CPU控制区别于传统的“热备份”冗余控制,传统的“热备份”冗余就是两个模块同时在线工作,一个主模块,一个从模块,主模块按照系统要求正常工作,从模块处于热备份状态,实时监控主模块工作状态,一旦检测到主模块出现故障,从模块便可自动接管主模块工作,系统可不受停机损失[12]。

星务系统的两种工作模式分别为安全工作模式和正常工作模式,本设计选择两块CPU,主CPU在正常模式下工作,从CPU在两种模式下都有其任务。从CPU主要功能有两个其一是正常工作模式下监测可靠性低但性能好的主CPU并协助主CPU进行工作;另一个功能是在主CPU故障后担任起整个系统的工作保证星务系统在安全模式下仍能完成卫星基本的功能。

从CPU的APA600对SF2的监控通过两种途径来实现。APA600作为从CPU要与主CPU的协同工作来满足星务的需求,SF2向APA600发送控制指令,APA600向SF2返回应答信息并根据控制指令向SF2发送请求的数据,通过该过程APA600实现对SF2的监控;另一种监控方式是通过设置看门狗实现监控,SF2定时向APA600发送喂狗信号,若APA600在设定的时间内没有收到喂狗信号就会复位SF2,如果连续复位超过约定次数就断定SF2不能正常工作,将SF2断电,系统进入安全模式实现正常模式向安全模式的切换。

2.3 UART通信方式的可靠性设计

其中UART通信有两种基本拓扑结构星型和总线型。由于需要点到点的通信在此选择了星型拓扑结构全双工处理方式。星型结构全双工处理方式由于采用独占线路只对单个节点实施全双工对轮询处理的效率并没有影响。不过在这种方式下在主节点未发出命令的任何时间从节点可以主动向从节点传送数据有利于处理比较紧急的通信任务所以这处理方式适用于从节需要主动上传数据的场合[13-14]。

为提高数据传输的可靠性,在软件设计时,运用握手通信机制、CRC校验码等编程设计[15],并加入UART自复位设计。双CPU通信过程中接受不到信息会有两种原因,其一是发送端发生错误没能将信息发出来,其二就是接收端发生错误未能将信息读出来。针对第一种原因在UART链路设计中加入反馈复位信号设计,若对方没收到信息将反馈一个信号给到UART发送端将UART进行复位,复位之后重新发送数据。针对第二种原因即发送端复位之后接收端仍不能接受到数据的情况下就需要检查接受端自身的问题。首先接收端进行自复位,然后给发送端一个重发数据的信号,重新来接收数据。

3 软件实现

3.1 SF2的看门狗设计

看门狗设计实现星务系统安全模式与正常模式的切换。SF2需要每一个任务周期 (500 ms)通过UART向APA600发送喂狗信号,给到APA600中,若APA600连续4 s未接到喂狗信号APA600将整个SF2复位。实现高可靠性的APA600对SF2的监控功能。基于μCOS-II系统的SF2芯片的喂狗信号我们通过系统任务的时间间隔进行发送以确保喂狗信号的定时发出。

若SF2累计复位3次,则掉电SF2,系统进入安全模式。看门狗及复位管理的流程如图2所示。

图2 看门狗及复位管理流程图

3.2 双CPU冗余通信时序设计

SF2向APA600发送控制指令并等待APA600的应答,应答分为两类对于请求数据的指令APA600会将数据通过UART返给SF2,但是对于另一些控制指令并不需要返回数据信息,这时候要想确保APA600收到了SF2的指令就必须设置应答机制。双机通信的时序设计如图3所示。

图3 双CPU通信时序图

3.3 双CPU冗余通信的重要函数设计

1)等待接受函数(commWaitReceiveFinish())设计

在双机通信中很重要的一个工作是接受数据,接收数据之前首先需要知道缓存中存在的数据以保证能完整的读取数据。该等待接受函数的功能是等待接受缓存中完全收满一帧数据之后返回接收到的数据个数,使我们在接受数据之前可以确认缓存区的数据量,保证接受时可以收到完整的数据。函数实现流程如图4所示。

图4 等待接受函数流程图

其中ONE_CYCLE_DELAY是每次等待的时间,这个延时要求必须大于下位机发送一个字节数据的时间(1/(波特率/8)秒)。为减少 CPU延时处理的占用,该时间小于下位机发送两字节数据的时间,且该延时在SF2上必须小于APA600接收应答后开始到发送数据帧的时间(如图5所示)。

图5 帧间传输间隔设计

2)接受函数(commReceiveFrame())设计

接收函数的主要功能就是解析数据帧读取数据并返回帧标识。实现双CPU通信要保证双CPU两边任务的同步性,任务同步的主要思想是网络通信中的应答模式所以我们这里接收函数中要实现有应答的接受函数。接收函数的实现流程如图6所示。

图6 接受函数流程图

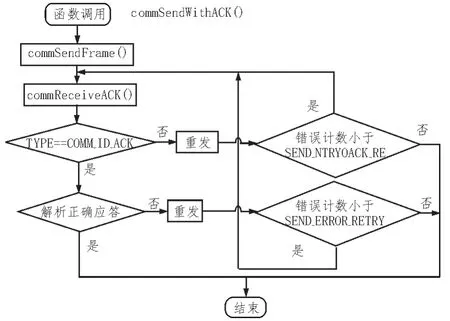

3)发送函数(commSendWithACK())设计

发送函数设计图如图7所示。发送函数在发送数据后,等待接收应答帧。如果接收到正确解析的应答,函数直接返回 TRUE,接收到解析错误应答,则重发;如果应答不成功,将进行数据重发直到重发计数大于设定值(SEND_ERROR_RETRY),重发次数大于设定值仍未成功时函数返回FALSE。其中重发数据的时间间隔根据下位机处理时间来设定。没有接收到数据,重发直到重发计数大于SEND_NOACK_RETRY时返回 FALSE。 重发时间间隔为 FIRST_WAITING_DELAY。

图7 发送函数流程图

4 结束语

文中的双CPU冗余通信设计基于CortexTM-M3的Smart Fusion2芯片和宇航等级芯片APA600,通过UART以及三线制方式来实现两个CPU之间的信息交互。APA600通过看门狗的喂狗信号的接受以及SF2控制指令的正常发送实现对SF2的监控以及两个CPU的协同工作。高性能芯片APA600的监控以及对于UART自复位设计整体提高了整个系统的可靠性,保证了星务系统的任务的可靠执行,使得系统性能更加符合微小卫星对高可靠性的要求。

[1]林来兴.现代小卫星与纳卫星技术发展(2)[J].国际太空,2002(9):27.

[2]余金培,杨根庆,梁旭文.现代小卫星技术与应用[M].上海科学普及出版社,2004(3):4-5.

[3]夏云非,黄凌.双CPU通信接口设计[J].电子世界,2014(5):162.

[4]衡军山,甄成刚.基于软件的双CPU冗余控制研究[J].微计算机信息,2005,21(7-1):59.

[5]衡军山.基于双CPU的冗余控制研究与实现[J].集成与液压,2008,7(36):7.

[6]王跃,李博通,李斌,等.电力系统微机保护装置中双CPU通信方案及优劣分析[J].电气应用2009,28(5):34.

[7]郑争兵.一种基于FPGA的UART电路设计[J].国外电子测量技术,2010,29(7):85.

[8]杨澜,戚秀真.UART微控制器设计方法及其FPGA实现[J].电子科技,2016,29(6):72.

[9]刘宝军,王中训,娄阳,等.基于FPGA的UART设计与实现[J].中国集成电路,2016(6):40.

[10]杨扬,叶芃,李力.基于FPGA的UART设计与实现[J].电子测量技术,2011,34(17):81.

[11]邬芝权,靳桅.基于双缓冲器的UART无线模块设计[J].现代电子技术,2015,38(5):6.

[12]廖慧敏.PLC控制器的双CPU冗余控制实现[J].湖北电力,2005,12(29):6.

[13]严利明,胡立坤,王庆超.基于UART的主从通信方式的主节点时序分析[J].电测与仪表,2006,43(487):51-53.

[14]胡立坤,王庆超.基于UART的可靠通信与性能分析[J].计算机工程,2006,32(10):15.

[15]董兵,许晓斐.RS-485总线系统通信可靠性设计与应用 [J].广东轻工职业技术学院学报.2009,8(3):2.

The design and implementation of redundancy communication of dual-CPU in house-keeping system

LV Cong1,2,LI Hua-wang1,2,CHANG Liang1,2

(1.Shanghai Institute of Micro-system and Information Technology,Chinese Academy of Science,Shanghai 200050,China;2.Shanghai Engineering Center for Micro-satellite,Shanghai 201203,China)

The design and the implementation of dual-CPU redundant communication in house-keeping system of microsat based on Smart Fusion2 and APA600.Using the technology of Dual-CPU redundant to improve system reliability.Added Watchdog to monitor CPU's status in the design of information interaction.Though setting information of handshake communication mechanism and link self-reset to further improve the reliability of the system.Describe the implemented of dual-CPU redundant communication in house-keeping system and the desigh of link reliability and important functions in dual-CPU communication.Using serial communication mode not only meet the high reliability demand for micro-nano satellite but also reduces the development costs.It is also simple to achieve and has a good practical value in satellite communication system.

Dual-CPU; redundancy communication; monitor; reliability

TN915.04

:A

:1674-6236(2017)14-0092-04

2016-07-19稿件编号:201607140

市科委扬帆计划(SHKW14YF01)

吕 聪(1990—),女,山东滨州人,硕士研究生。研究方向:星载计算机。