用于2.5D封装技术的微凸点和硅通孔工艺

2017-07-31曹中复

周 刚,曹中复

(中国电子科技集团公司第四十研究所,沈阳110032)

用于2.5D封装技术的微凸点和硅通孔工艺

周 刚,曹中复

(中国电子科技集团公司第四十研究所,沈阳110032)

过去几十年里,微电子器件尺寸按照摩尔定律持续减小,已经进入到真正的纳米时代。尽管集成电路的特征尺寸已经进入20nm之下,但是在特定领域,尤其是存储器、FPGA等对资源要求极高的领域,仅仅依靠摩尔定律已经不能满足市场需求。市场永无止境地对在可控功耗范围内实现更多的资源以及更高的代工厂良率提出迫切要求。针对一种新的2.5D封装技术,介绍了其中使用的微凸点(microbump)和硅通孔(through-silicon vias,TSV)等两项关键工艺,并进行了分析。

硅通孔;堆叠硅互连;微凸点;凸点下金属化层;封装;电沉积

1 引言

3D封装作为目前国内外比较热门的研究领域,有很多研究机构都在开展相关研究,而真正产业化的应用并不多见,目前主要集中于存储器的生产。业界将多个不同芯片并排堆叠的技术称为2.5D封装,如FPGA厂商赛灵思2011年发布的堆叠硅片互联(SSI)技术就是典型的2.5D封装技术。该技术将四个不同的FPGA芯片在无源硅中介层上并排互联堆叠,构建了相当于容量达2000万门ASIC的可编程逻辑器件。

图1 XILINX的2.5D封装示意图

通过图1的XILINX的2.5D封装示意图可以看出,该结构包括微凸点(microbump)、硅通孔(through-silicon vias,TSV)、无源硅介质(Passive Si interposer)和C4 BUMP。这类新的2.5D封装技术区别于以往的特点在于微凸块和硅通孔等技术的共同应用,各芯片通过微凸块引出信号,多块芯片通过无源硅介质(Passive Si interposer)实现互连,硅通孔技术和C4 BUMP实现基板封装。论文后续部分将分别对微凸点(microbump)和硅通孔(through-silicon vias,TSV)这两项工艺进行研讨。

2 微凸点(m i crobum p)工艺介绍

同黏着键合、金属/焊料微凸点键合、直接氧化物键合、阳极键合和玻璃介质键合等键合技术相比,微凸点键合(如图2所示)由于既可以作为结构支撑也可以作为叠层间的电气互连线[1],具有易于实现高可靠性低温互连等优势而倍受关注。微凸点工艺来源于BGA形式,BGA形式封装1980年由富士通公司提出,在日本IBM公司与CITIZEN公司合作的OMPAC芯片中诞生[2]。随着电路规模的发展,BGA逐渐不能满足电子产品向更小型、更多功能、更高可靠性发展的要求,更不能满足硅集成技术发展对进一步提高封装效率和进一步接近芯片本征传输速率的要求[3]。在这种背景下,日本富士通公司又提出了芯片级封装(CSP)。其结构与BGA结构基本一样,锡球直径和球中心距缩小,这样在相同封装尺寸时可容纳更多的I/O数,使组装密度进一步提高。随着三维封装的发展,研究者根据前面几种封装形式的一些思路提出了微凸块工艺并予以实现。

图2 微凸块键合示意图

根据具体需求,纯金属(Au,Cu,Sn,In等)、共晶或者高熔点合金(PbSn,AuSn,AgSn,SnCu,AgSnCu等)均可用来制作微凸点。不过目前无铅化成为业界选择凸点材料的普遍共识。

目前主要的微凸点制作方法包括:电沉积(electrodepositing)、丝网/模版印刷(screen/stencil printing)、焊料喷射(solder jetting)、C4NP、置球(placing performed solder spheres)、钉头凸点(stud bumping)以及蒸发(evaporation)等。

根据稳定性和精度要求,电沉积方法较适合制作本文中的微凸点。电沉积方法采用光刻掩膜技术通过电沉积来获得形状尺寸精确的凸点,该技术由Hitachi开发并首先提出[4]。电沉积相对进程比较慢,根据沉积材料的不同,沉积速率从每分钟0.2微米至几微米不等。电沉积技术可以采用恒电位(Potentiostatic)、恒电流(Galvanostatic)以及脉冲(Pulse)方式进行。晶圆表面电场分布决定了实际沉积电流,因此在电沉积过程中是影响凸点高度、焊料成分和表面形貌均匀性的最关键因素。为保证晶圆表面电场分布均匀,电压应该施加在晶圆圆周的多点上。除此以外,电沉积面积与晶圆面积的比率以及晶圆表面凸点分布的均匀性也会影响沉积电流的均匀性。电沉积方法可以精确复制光刻胶图案,并且适用于不同尺寸的晶圆,不同的钝化材料以及不同的光刻图案。所有的半导体材料(如硅、SiGe、GaAs、InP等)以及陶瓷和石英基底都可以用电沉积方法来制作凸点。

如图3所示电沉积方法制备凸点的基本流程包括:溅射凸点下金属化层(UBM,Under Bump Metallization)、形成光刻图案、电沉积凸点、去除光刻胶以及UBM刻蚀。

第一步是在晶圆表面溅射UBM层;

第二步,旋涂光刻胶,接下来对光刻胶进行曝光刻蚀;

第三步,在图案中沉积金属或焊料;

第四步,去除光刻胶;

第五步,刻蚀凸点之间的UBM层。

第六步,进行回流,使焊料变成球状,并在焊料与UBM界面处形成金属间化合物。

图3 电沉积法制作凸点流程图

电沉积方法可以方便地制备纯金属凸点以及一些析出电位接近的二元甚至三元合金焊料。但是采用含有多种金属离子的镀液制备合金焊料时往往得到的凸点成分不均匀,利用二步法可以解决这一问题,即采用先沉积一种金属而后再沉积另一种金属,最后对得到的凸点进行退火来得到成分均匀的合金焊料。利用二步法还可以制备一些因沉积电位相差很远而不能在单一镀液中制备的合金凸点。

利用电沉积方法制作小尺寸凸点,首先要保证镀液完全润湿光刻微孔,而由于光刻胶润湿较差等诸多因素,这一点并不容易实现。不完全的润湿会导致气泡残留在光刻微孔中致使最终制备的凸点内部含有孔洞以及凸点体积不一致。现有的技术水平可提供真空浸渍、表面改性、镀液中添加润湿剂等手段改善镀液在光刻微孔中的润湿性能。

3 硅通孔((t hrough-si l i con vi as,TSV)工艺介绍

相比于其他3D封装技术,TSV技术具有四方面的优势[5-6]:

(1)能提供更短的电路连接,大幅提高信号的传输速度;

(2)能实现高密度、高深宽比连接,拥有更多的信号通道;

(3)能替代效率低下的引线键合方式,使信号传输速度更快、功率消耗更少,同时,可以保证传递功率的一致性;

(4)能使高密度堆叠成为可能,拥有更高的封装密度,有效降低成本。

因此,TSV封装技术是整个电子封装产业的技术主流,更多的研究机构和封装公司已将TSV技术看作IC(IntegrityCircuit)互连危机的一种解决方案,也被誉为继引线键合(WB,Wire Bonding)、载带键合(TAB,Tape Automated Bonding)和倒装芯片(FC)之后的第四代封装技术[7]。

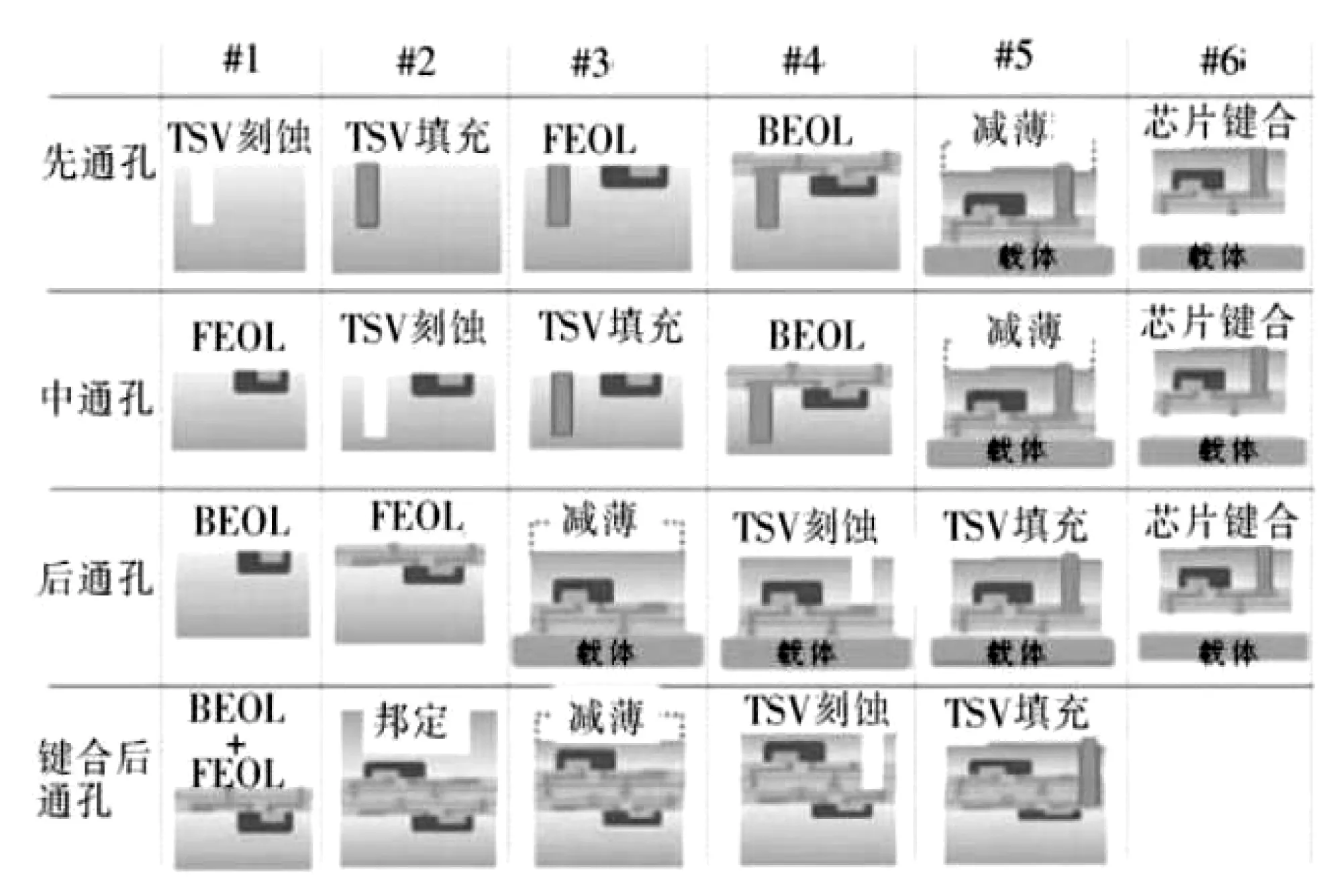

按照通孔制作在整个工艺流程中所处的时间点不同,TSV集成方式可以分为以下四类[5]:

先通孔工艺:CMOS之前制作硅孔;

中通孔工艺:在CMOS和BEOL(Back End of Line)之间制作硅孔;

后通孔工艺:在BEOL之后制作硅孔;

键合后通孔工艺:在硅片减薄、键合后制作硅孔。

四种3D-TSV集成方式的工艺流程图如图4所示[9]。

图4 四种不同的TSV集成方式工艺流程图

后面对减薄技术、通孔工艺这两个TSV主要工艺步骤进行简要介绍。

减薄目前比较主流的做法是一体化减薄,即将硅片的机械打磨、抛光、保护膜的去除和粘贴划片膜等工艺集合在一台设备之内。利用精密的机械式传送系统,硅片从开始打磨一直到粘贴划片膜为止始终被吸在真空吸盘上,这样能够有效保持硅片的平整,也给硅片提供了支撑。当硅片被粘贴到划片膜上后,硅片会顺从划片膜的形状从而保持平整,不会再发生翘曲、断裂等问题,使后续工艺可以有效进行,保证了产率。

比较成熟的通孔制作工艺步骤如下:

(1)通过深层离子反应刻蚀(DRIE)或激光在硅片上刻蚀出通孔;

(2)通过PECVD工艺淀积绝缘层;

(3)通过PVD、PECVD或MOCVD工艺淀积金属粘附层/阻挡层/种子层;

(4)通过化学电镀的方法在硅通孔中填充铜金属;

(5)通过化学机械抛光工艺对硅片进行减薄露出硅通孔另一端。

在整个硅通孔((through-silicon vias,TSV)工艺中减薄和通孔制作这两个步骤关系TSV工艺的质量,应持续开展研究。

根据ITRS预测[8],TSV封装技术,将在硅孔直径、硅晶圆厚度、孔间引脚间距、垂直方向堆叠层数等方面,继续向更加微细化的方向发展。预测显示,TSV的硅孔直径将由4微米缩小到1.6微米,引脚间距将由10微米缩小到3.3微米,垂直方向上的堆叠层数将由5层上升到12层,减薄(Wafer Thinning)的硅晶圆厚度将由40微米进一步缩小到8微米。

4 结束语

首先对 2.5D封装技术采用的微凸点(mi-crobump)工艺进行介绍,列举了电沉积、丝网/模版印刷、焊料喷射、C4NP、置球、钉头凸点以及蒸发等制作方法,重点介绍了适用于微凸点工艺的电沉积方法及其具体流程。接着对TSV工艺及其分类进行了介绍,并对TSV工艺中的主要工艺步骤——减薄技术、通孔工艺进行了论述。通过对微凸点工艺和TSV工艺的掌握,我们可结合其他工艺将其应用于大规模FPGA、大容量存储器等大尺寸、高密度电路的实现。

[1]罗驰,练东,电镀技术在凸点制备工艺中的应用[J].微电子学,2006,36(4):467-472. LUO Chi,LIAN Dong,Application of Electroplating Technology to Solder Bumping Formation[J].Microelectronics, 2006,36(4):467-472.

[2]叶冬,刘欣,刘建华,曾大富,芯片级封装技术研究[J].微电子学,2005,35(4):349-356. YE Dong,LIU Xin,LIU Jian-hua,ZENG Da-fu.A Study on Chip Scale Package Technology[J].Microelectronics, 2005,35(4):349-356.

[3]K.N.Tu.Reliability challenges in 3D IC packaging technology[J].Microelectronics Reliability,2011,51(3):517-523.

[4]TKawanobe,KMiyamoto,Y Inaba.Solder Bump Fabrication by Electrchemical Method for FE Interconnection[J].IEEE Publication CH1671-7/0000,1981:149.

[5]吴向东.三维集成封装中的TSV互连工艺研究进展[J].电子与封装,2012,12(9):1-5. WU Xiang-dong.Research Status of Through-Silicon Via Interconnection for 3DIntegration Technology[J].ELECTRONICS&PACKAGING,2012,12(9):1-5.

[6]蔡积庆.导通孔电镀铜填充技术[J].印制电路信息,2012 (5):28-32. CAI Ji-qing,Copper plating via filling technology[J].Printed Circuit Information,2012(5):28-32.

[7]朱健,吴璟,贾世星,姜国庆.基于MEMS圆片级封装/通孔互联技术的SIP技术 [J].固体电子学研究与进展,2011,31(2):213. Zhu Jian,Wu Jing,Jia Shixing,Jiang Guoqing.3D SIP by WLP/TSV[J].Research&Progress ofSSE Solid State Electronics,2011,31(2):213.

[8]Feng Z V,Li X,Gewirth A A.Inhibition due to the interaction of polyethylene glycol,chloride,and copper in plating baths:A surface-enhanced Raman study[J].The Journal of Physical ChemistryB,2003,107(35):9415-9423.

[9]邓丹,吴丰顺,周龙早,刘辉,安兵,吴懿平.3D封装及其最新研究进展[J].微纳电子技术,2010,47(7):443-450. Deng Dan,Wu Feng-shun,Zhou Long-zao,Liu Hui,An Bing,Wu Yi-ping.3D Package and Its Latest Research[J]. Micronanoelectronic Technology,2010,47(7):443-450.

Technics of Microbump and TSV for 2.5D Package Technology

Zhou Gang,Cao Zhongfu

(The 47th Research Institute of China Electronics Technology Group Corporation,Shenyang 110032,China)

Over the past decade,the micro-electronics device's size continuously scaled down according to Moor's Law,and had already got into a real nano ages.Though the characteristic size of integrated circuits has already got under 20nm,but in such particular fields as memory,FPGA,etc., Moor's Law can't meet the request of market which always makes an urgent request for more resource and higher foundary yield within the controllable power.Microbump and TSV as two key technologies applied to a new 2.5D package technology are discussed and analyzed in this paper.

TSV;SSI;Microbump;UBM;Package;Electrodepositing

10.3969/j.issn.1002-2279.2017.02.004

TN911

A

1002-2279-(2017)02-0015-04

周刚(1978-),男,辽宁省法库县人,高级工程师,工学学士,主研方向:集成电路设计方向,目前关注领域,集成电路3D封装、可靠性设计、可编程器件。

2015-11-04