多相并行FIR滤波器的FPGA高速实现方法

2017-06-27李春祎

张 娜,李春祎

(1.中国电子科技集团公司第五十四研究所,河北 石家庄 050081;2.河北工业职业技术学院,河北 石家庄 050091)

多相并行FIR滤波器的FPGA高速实现方法

张 娜1,李春祎2

(1.中国电子科技集团公司第五十四研究所,河北 石家庄 050081;2.河北工业职业技术学院,河北 石家庄 050091)

L路多相并行FIR滤波器的工作速率是单路串行FIR滤波器的L倍,基于多项式分解的多相并行FIR滤波器实现结构简单、计算复杂度小、滤波运算延迟少;针对多相并行FIR滤波器,给出了基于多项式分解的多相并行FIR滤波器优化实现结构的FPGA高速实现方法。归纳、整理和推导了2路至8路基于多项式分解的多相并行滤波器优化实现结构,并针对FPGA实现的具体特点给出了多相并行滤波器优化实现结构的FPGA高速实现方法。通过测试分析可知,给出的基于多项式分解的多相并行FIR滤波器优化实现结构的FPGA高速实现方法能够在FPGA上高速实现多相并行FIR滤波器。

FIR滤波器;多相分解;FPGA;高速

0 引言

数字信号处理具有灵活性、高精度和高稳定性、便于大规模集成、对数字信号可以存储和运算且系统可以获得高性能指标等优点,已被广泛应用于语音、图像、控制、航空和航天等众多领域[1]。在数字信号处理系统中,有限脉冲响应(Finite Impulse Response,FIR)滤波器具有先天稳定性和可以有严格的线性相位等突出特性,在数字信号处理领域得到了广泛应用[2]。文献[3]指出,随着数字信号处理需求的提高,对FIR滤波器运算速率的需求已超过1 GHz。现场可编程逻辑阵列(FPGA)在灵活性和性能等方面具有优势,已作为通用硬件平台广泛应用;尽管Altera和Xilinx推出器件的最高工作频率超过500 MHz,但是仍然不能直接实现运算速率超过1 GHz的FIR滤波器[4]。由于FPGA器件的限制,要在FPGA中实现运算速率较高的FIR滤波器,只能采用并行结构,耗费更多的资源以降低FPGA的工作频率[5]。

近年来,运算速率较高的FIR滤波器的多路并行实现结构和相应的工程实现得到了广泛关注[6]。文献[7]给出了一种超高速并行滤波结构FIR的FPGA实现及应用。文献[8-9]给出了基于多相滤波的高效数字下变频设计,并通过FPGA实现了在低频率下完成高速数据流下变频。通过直接应用多相分解理论可知,一个N阶串行FIR滤波器可由L2个N/L阶子滤波器等效并行实现,其中并行处理路数为L;可以看出,由多相分解理论得到的并行FIR滤波器实现结构的工作频率降为串行FIR滤波器的1/L,其计算复杂度或耗费的资源升为串行FIR滤波器的L倍[10]。在对FIR滤波器多相分解时,文献[10]提出的Fast FIR Algorithms (FFAs)方法对多相分解的同类项进行规整合并从而减少并行FIR滤波器实现结构的计算复杂度。在FFAs方法的基础上,文献[11-12]利用滤波器抽头系数的对称性关系进一步降低并行FIR滤波器实现结构的计算复杂度;为了进一步节约硬件资源,文献[13]论述了一种基于迭代短卷积算法的低复杂度并行FIR滤波器结构。为了降低FIR并行滤波器的计算复杂度,文献[14-15]提出的迭代短卷积方法通过增加加法和延迟单元为代价减少FIR并行滤波器的乘法器数目。相比于FFAs方法,文献[11-15]提出的并行FIR滤波器实现结构计算复杂度改善不明显。

FFAs方法给出的FIR滤波器并行实现结构延迟少,计算复杂度小,结构简单[4];鲜有文章涉及基于多相分解的FFAs多相并行FIR滤波器优化实现结构的FPGA高速实现;本文聚焦于多相并行滤波器FFAs优化实现结构及其FPGA高速实现。

1 多相并行FIR滤波器实现结构

1.1 传统并行实现结构

FIR滤波器的频域表达式可以表示为[4]:

(1)

(2)

式中,x(·)、h(·)和y(·)分别表示滤波器的输入信号、有限脉冲响应和输出信号,N表示滤波器阶数。

并行路数为5的FIR滤波器的频域表达式为:

,(3)

式中,为了简化表示,Xk表示Xk(z5),Hj表示Hj(z5),Yi表示Yi(z5);滤波器经5路多相化处理后每路速率降为单路全速处理的1/5。

式(3)给出了FIR滤波器的5路多相直接分解实现结构,5路多相输出共需要25个子滤波器(每路多相输出均需要5个子滤波器),其计算复杂度是串行滤波器的5倍。

1.2 基于FFA的并行优化实现结构

基于FFAs的FIR滤波器的并行优化实现结构需要针对具体并行路数,通过多项式分解得到FIR滤波器多相输出与多相输入之间的关系[10]。下面归纳、整理和推导得到2路至8路基于多项式分解的多相并行滤波器实现结构。

当L=2时,有优化实现结构[10]:

(4)

当L=3时,经多项式分解可得:

(5)

当L=4时,对文献[10]结果进行整理可得优化实现结构:

(6)

当L=5时,经多项式分解可得:

(7)

当L=6时,经多项式分解可得:

(8)

当L=7时,经多项式分解可得优化实现结构:

(9)

当L=8时,文献[4]给出了一种实用的优化实现结构。在式(4)~(9)中,符号X和H下的多个数字下标表示对应输入相加,如X15表示X1+X5。

2 多相并行FIR滤波器FPGA高速实现方法

从式(4)~(9)中可以看出多相并行FIR滤波器的实现结构;为了尽可能提高FPGA运行速度,减少滤波器需要并行的路数,对于多相并行FIR滤波器FPGA高速实现,需要结合多相并行FIR滤波器实现结构和FPGA特点进行综合考虑。

对于多相并行FIR滤波器的FPGA高速实现,主要设计思路如下:

① 为了提高效率,采用模块化实现结构,多相并行FIR滤波器FPGA高速实现主要功能模块包括:子滤波器模块、多输入加法模块、延迟模块;

② 为了尽可能提高FPGA运行速度,对于多相并行FIR滤波器的FPGA实现,不管在功能模块内部还是外部都应采用运算加锁存的实现方式;建议对二输入加法器结果锁存(多输入加法器分解为多个二输入加法器实现),对二输入乘法器结果锁存;

③ 为了保证多路输出信号的一致性,应严格控制各路信号的延迟,保证各路信号之间的严格同步,包括功能模块内部和功能模块外部;不管功能模块内还是功能模块外的同步,都以最长延迟为基准利用延迟模块对信号进行同步对齐。

对于子滤波器功能模块,为了尽可能提高FPGA运行速度,借鉴并采用全并行FIR滤波器结构[16]。不失一般性,设定子滤波器系数个数为5,子滤波器设计图如图1所示。

图1 子滤波器功能模块设计图

如图1所示,为了尽可能提高FPGA运行速度,在子滤波器功能模块中,对所有二输入加法器结果锁存(多输入加法器分解为多个二输入加法器实现),对所有二输入乘法器结果锁存;另外,将子滤波器系数作为输入进行配置,保证了子滤波器功能模块的通用性。由于所有子滤波器阶数相同,所有子滤波器输出相对于数据输入之间的延迟相同。

由于加法器输入的多样性,可按照多个模块进行设计。为了尽可能提高FPGA运行速度,借鉴并采用全并行树型加法器结构[5],多输入加法器分解为多级二输入加法器,并对每一级加法器结果进行锁存;另外,为了便于统计延迟及信号同步,将输入数据的取负运算包含在多输入加法器中,并将多输入加法器采用统一设计架构。不失一般性,设定输入数目为9,其中4个输入需要乘以-1,多输入加法器设计图如图2所示。

图2 多输入加法器功能模块设计图

采用图2所示的统一设计架构,不同输入数目对应的加法器延迟时钟数目可以表示为:

(10)

式中,Dclk表示多输入加法器结果相对于输入延迟的时钟数目,Ninput表示输入数目,⎣·」表示向上取整运算。

延迟功能模块可以采用多级D触发器级联的形式实现,也可以采用双口RAM实现。

设计好子滤波器功能模块、多输入加法器功能模块和延迟功能模块后,需要按照式(4)~(9)所示的基于多项式分解的多相并行滤波器优化实现结构完成FPGA高速实现,为了保证多路输出信号的一致性,应严格控制各路信号的延迟,保证各路信号之间的严格同步。

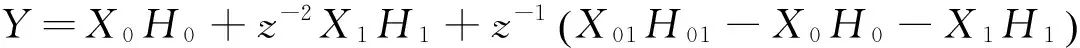

不失一般性,下面以5路多相并行FIR滤波器为例具体说明FPGA的高速实现。

利用式(7)并结合多相并行FIR滤波器的FPGA高速实现主要设计思路,5路多相并行FIR滤波器的FPGA的高速实现图如图3所示。

从图3中可以看出,多相并行FIR滤波器的FPGA的高速实现主要包括3种功能模块:分别是子滤波器模块、多输入加法器模块和延迟模块;为了保证多路输出信号的一致性,除了各功能模块内部的严格同步外,对于各功能模块间采用延迟模块进行延迟以保证各信号之间的严格同步;不管功能模块内还是功能模块外的同步,都以最长延迟为基准利用延迟模块进行同步对齐;在图3中,第4路多相输出对应的7输入加法器功能模块延迟最长,则以它为基准将第0路~第3路多相输出与之同步对齐。另外,图3所示的多相并行滤波器FPGA高速实现中,所有运算都采用运算寄存和全并行的方式进行,由此能够在较高的频率工作。

图3 5路多相并行滤波器FPGA高速实现图

3 算法分析

不失一般性,以5路多相并行FIR滤波器为例进行FPGA高速实现并进行测试验证。

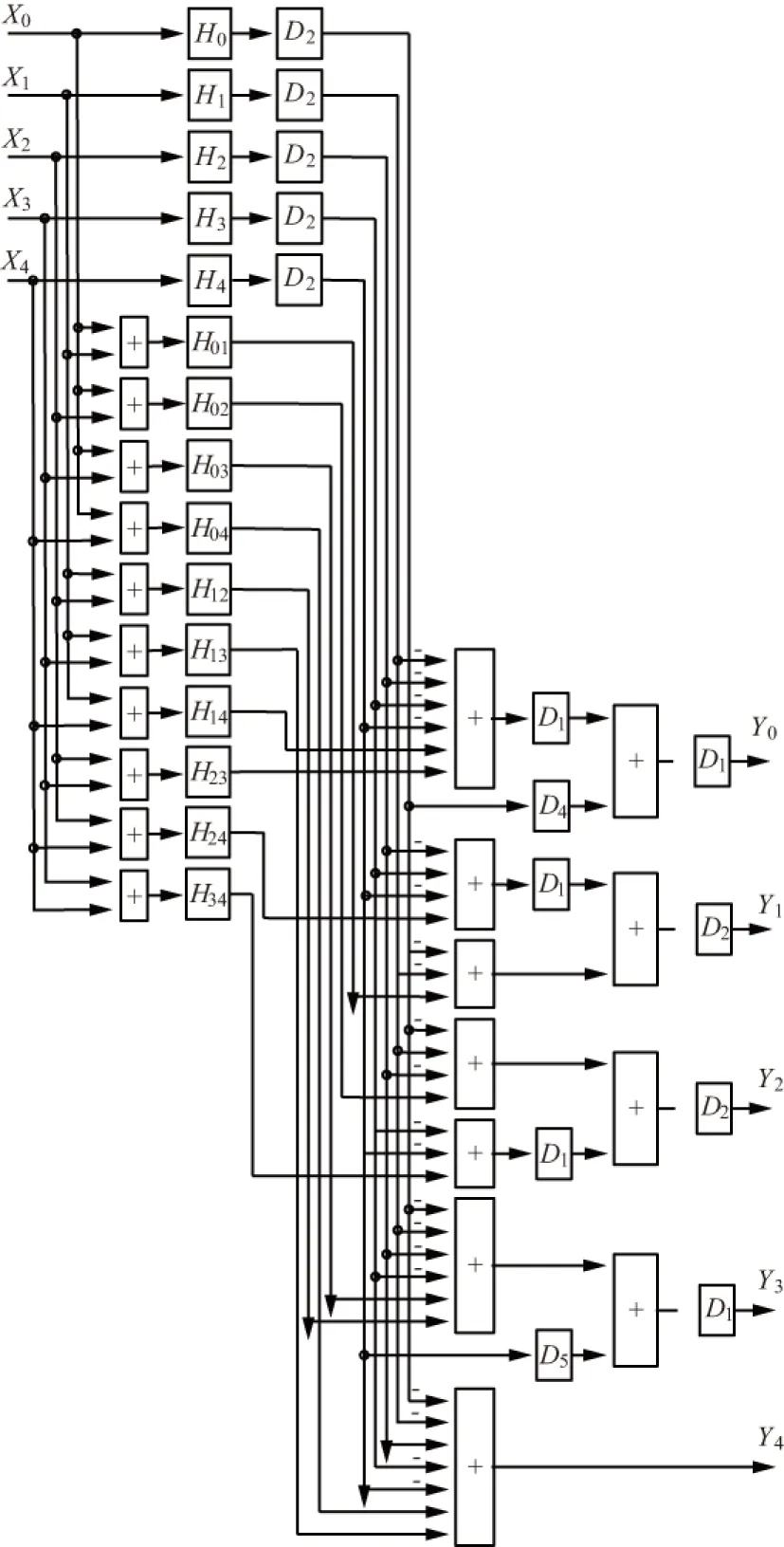

设计1个具有30个抽头系数的低通滤波器,对滤波器的抽头系数按照12位进行量化,其归一化频率响应曲线如图4所示。

在Altera公司Arria V系列芯片5AGXFB3H4F35I5上按照图3所示实现框图对5路多相并行FIR滤波器进行FPGA高速实现,输入信号位宽为9位,系统测试图如图5所示。图6给出了FPGA输入信号和输出信号的频谱。

图4 滤波器归一化频率响应曲线

图5 测试图

图6 FPGA输入信号和输出信号频谱

如图5和图6所示,测试时的输入信号源由2个5路多相NCO累加得到(每个NCO的输出信号频率可单独控制),从而产生共有2个频点的信号。从图4和图6中可以看出,5路多相FIR滤波器FPGA高速实现的输入和输出信号的频谱符合滤波器频率响应特性,且其输出结果和matlab软件的输出结果一致,没有误差。经过测试,FPGA工作速度可达250 MHz。

由此可以看出,本文给出的多相并行FIR滤波器的FPGA高速实现思路能够在FPGA上高速实现多相并行FIR滤波器。

4 结束语

基于多项式分解的多相并行FIR滤波器实现结构简单、计算复杂度小、滤波运算延迟少。本文归纳、整理和推导了2路~8路基于多项式分解的多相并行滤波器优化实现结构,给出了多相并行滤波器优化实现结构的FPGA高速实现方法。通过测试可知,给出的多相并行FIR滤波器的FPGA高速实现方法能够在FPGA上高速实现多相并行FIR滤波器,对系统的工程实现有指导意义。

[1] 张建伟,展雪梅.FIR数字滤波器的设计与实现[J].无线电工程,2010,40(6):54-56.

[2] 许瑞生,崔琦.FIR滤波器在扩频发射机中的应用[J].无线电通信技术,2011,37(4):62-64.

[3] 张维良,张彧,杨再初,等.高速并行FIR滤波器的FPGA实现[J].系统工程与电子技术,2009,31(8):1819-1822.

[4] 宋广怡.FIR滤波器的8路多相27子滤波器实现结构[J].无线电工程,2015,45(2):22-25.

[5] 孙大元,王宪平.基于PMF-FFT的高动态长伪码捕获实现[J].无线电工程,2016,46(8):65-69.

[6] 王璐,李明.基于并行FIR滤波器结构的数字下变频[J].火控雷达技术,2010,39(3):36-40.

[7] 张峻涛,王平,傅石雨.超高速并行滤波结构FIR的FPGA实现及应用[J].通信对抗,2013,32(1):36-39.

[8] 刘二平,刘晓杰.基于多相滤波的高效数字下变频设计[J].无线电工程,2016,46(8):23-26.

[9] 顾明超,李倩.宽带数字下变频器的FPGA实现[J].无线电通信技术,2014,40(5):69-72.

[10]Parker D A,Parhi K K.Area-Efficient Parallel FIR Digital Filter Implementations[C]∥IEEE Proceedings of International Conference on Application Specific Systems,Architectures and Processors,1996:93-111.

[11]Tsao Y,Choi K.Area-Efficient Parallel FIR Digital Filter Structures for Symmetric Convolutions Based on Fast FIR Algorithm[J].IEEE Transactions on Very Large Scale Integration Systems,2012,20(2):366-371.

[12]Tsao Y,Choi K.Area-Efficient VLSI Implementation for Parallel Linear-Phase FIR Digital Filters of Odd Length Based on Fast FIR Algorithm[J].IEEE Transactions on Circuits and Systems-II:Express Briefs,2012,59(6):371-375.

[13]田晶晶,李广军,李强.一种基于迭代短卷积算法的低复杂度并行FIR 滤波器结构[J].电子与信息学报,2014,36(5):1151-1157.

[14]王成,侯卫华,刘明峰,等.采用多级子并行滤波器级联结构的并行FIR滤波器[J].中国电子科学研究院学报,2008,3(1):92-96.

[15]Cheng C,Keshab K P.Hardware Efficient Fast Parallel FIR Filter Structures Based on Iterated Short Convolution [J].IEEE Transactions on Circuits and Systems-I:Regular Papers,2004,51(8):1492-1500.

[16]王英喆,王振宇,严伟,等.全并行FIR滤波器的FPGA 实现与优化[J].电子设计工程,2015,23(22):94-97.

FPGA Implementation of Polyphase Parallel FIR Filter

ZHANG Na1,LI Chun-yi2

(1.The 54th Research Institute of CETC,Shijiazhuang Hebei 050081,China;2.Hebei College of Industry and Technology,Shijiazhuang Hebei 050091,China)

Compared with the serial FIR filter,the sample frequency ofL-channel polyphase parallel FIR filter is increased by a factor ofL.The implementation structure of polyphase parallel filter based on polynomial decomposition is simple,with low computation complexity and short delay.The paper summarizes and deduces the optimal structure of polyphase parallel filter from 2 channels to 8 channels.Further,the paper proposes the implementation method of the optimal structure of polyphase parallel filter fit for processing in FPGA.The computer simulation shows the proposed implementation method of polyphase parallel filter is fit for processing in FPGA with high-speed.

FIR filter;polyphase decomposition;FPGA;high-speed

10.3969/j.issn.1003-3114.2017.04.21

张娜,李春祎.多相并行FIR滤波器的FPGA高速实现方法[J].无线电通信技术,2017,43(4):86-90.[ZHANG Na,LI Chunyi.FPGA Implementation of Polyphase Parallel FIR Filter [J].Radio Communications Technology,2017,43(4):86-90.]

2017-03-11

中国电子科技集团公司航天信息应用技术重点实验室开放基金(EX166290012)

张 娜(1984—),女,硕士,工程师,主要研究方向:卫星通信。李春祎(1980—),女,讲师,主要研究方向:信号与信息处理。

TN919

A

1003-3114(2017)04-86-5