基于P2020的嵌入式卫星TDMA访问控制平台设计

2017-06-27杨旭光

杨旭光

(中国电子科技集团公司第五十四研究所,河北 石家庄 050081)

基于P2020的嵌入式卫星TDMA访问控制平台设计

杨旭光

(中国电子科技集团公司第五十四研究所,河北 石家庄 050081)

针对TDMA卫星通信系统通信质量高、系统容量大的特点,设计了一种基于P2020处理器嵌入式平台的卫星TDMA访问控制平台,对P2020处理器进行了简要介绍,分析了嵌入式平台的结构组成,给出该嵌入式平台的特点及设计方案,对网口模块、串口模块和处理器上电复位模块进行了详细阐述,设计了网络模块的驱动程序,对平台进行了工程验证测试,平台可满足大容量、多模式TDMA卫星通信系统应用的发展需要。

P2020;嵌入式;时分多址;访问控制

0 引言

卫星通信以其覆盖范围广、良好的广播能力及不受各种地域条件限制等优点在无线通信中发挥着重要的作用[1]。在卫星通信领域,TDMA通信体制具有通信质量高、保密较好、系统容量大的优点,但它必须有精确定时和同步以保证终端之间的正常通信,全网需要进行时间同步,各地球站之间在时间上的同步技术较复杂,实现比较困难[2],技术实现上要求软件及操作系统响应快、实时性强,在硬件上要求平台运算能力强,通信接口数据传输速度快,数据存储读取速度快。访问控制单元是TDMA通信系统的重要组成部分,主要负责TDMA链路的访问控制、突发数据成帧、突发数据解帧和帧计划计算等。硬件平台要求与调制解调模块具有高速通信接口、较强的数据吞吐率、较为丰富的外部接口以及较低的功耗。PowerPC是近年来通信领域广泛使用的一种嵌入式微处理器,是一种RISC架构的CPU[3],具有优异的性能、较低的能耗、较低的散热量,以及伸缩性好、方便灵活等优点,选用合适的PowerPC系统可以满足TDMA访问控制单元对硬件平台的要求。

1 平台组成

1.1 QorIQ P2020处理器介绍

PowerPC作为主流通用处理器之一,其运算性能和综合性能在高端服务器以及苹果G系列图形工作站等方面已得到体现[4]。目前主流处理器多采用多核设计,区别于单核芯片,多核芯片内部集成了2个或2个以上的核心,多核体系结构化解了单核平台上存在的性能瓶颈,在多核平台中,由于各线程都是在相互独立的执行核上并行运行的,因此各线程根本无需为得到某种资源而挂起[5],结合操作系统的支持,相对单核心可以带来不错的性能提升。

嵌入式处理器是嵌入式系统的核心,具有功耗低、稳定性好、环境适应性强的优点。本设计使用的P2020处理器是由FreeScale公司出品的双核嵌入式处理器,内部集成了2个e500v2内核,主频最高支持1.2 GHz,内置512 KB L2Cache,支持32/64-bit DDR2/DDR3,支持ECC,具有3个10/100/1000以太网接口、3路高速PCIe接口、2个UART接口、2个I2C接口,还具有Enhanced local bus(eLBC)总线和16个GPIO引脚[6]。

1.2 平台的结构

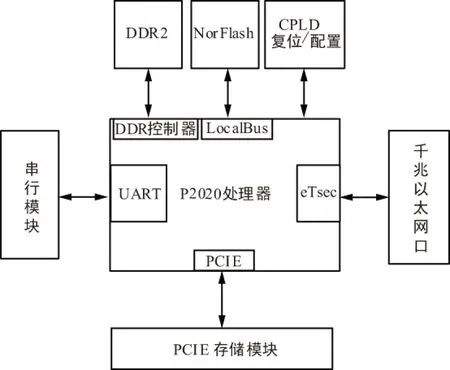

基于P2020嵌入式处理器的卫星TDMA访问控制平台的设计框图主要包括内存模块、Flash存储模块、千兆以太网接口模块、PCIe 接口模块(含扩展存储模块)、串行模块、CPLD控制模块,框图如图1所示。

图1 基于P2020嵌入式处理器的卫星TDMA访问控制平台设计框图

基于P2020嵌入式处理器的卫星TDMA访问控制平台,对外提供千兆以太网业务口,以及与外部信道模块交互的千兆以太网接口。通过业务口收发IP业务数据,通过与外部信道模块的接口实现信道数据的收发,在平台内部,处理器对IP 数据进行拆包组包运算、帧计划计算、TDMA成帧运算。P2020处理器利用自身以太网接口多、主频高和双核的特点,满足了TDMA访问控制装置接口丰富、运算能力强的需求,实现了数据的高速处理与通信;平台提供了PCIe转SATA大容量存储模块,实现了高速大容量高速数据存储和TDMA卫星通信程序的便利存储与加载。

2 平台详细设计

2.1 千兆以太网口模块设计

P2020处理器提供3个高速以太网控制器(eTSECs),支持IEEE1588标准,支持GMII、RGMII、SGMII、R/TBI协议。

P2020处理器以太网控制器(eTSECs)支持1000BASE-T。1000BASE-T物理层为邻点之间建立数据通道并提供比特流服务,由PCS子层以及PMA子层组成。PHY是物理接口收发器,位于OSI七层协议中的最底层物理层。物理层主要定义的是为数据传输的物理链路创建、维持以及拆除所需要的一些物理特性,为整个传输提供一个稳定可靠的物理环境。数据链路层在物理层基础上建立相邻节点之间的数据链路,通过差错控制提供数据帧在信道上无差错地传输。数据链路层可细分为逻辑链路控制LLC(logical link control)子层和介质访问控制MAC(media access control)子层[7-8]。MAC是媒体接入控制器,位于数据链路层,介于物理层与网络层之间,主要功能包括帧同步、差错控制、流量控制及链路管理[9]。P2020处理器的eTSECs接口提供MAC子层的信息处理。

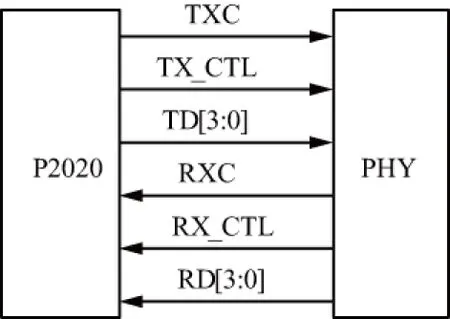

88E1111是一种成熟的PHY芯片,支持10/100/1000 Mbps三种速率以太网,为MAC提供RGMII/GMII/SGMII/MII和TBI等接口,P2020内部集成了MAC层功能模块,对外提供了3路与PHY互联的GMII/RGMII接口[10]。P2020处理器通过MDC/MDIO对PHY芯片的寄存器进行控制。将HWCFG_MODE[3:0]设置为“1011”,使PHY芯片工作在千兆RGMII coppor模式下。连接关系如图2所示。

图2 RGMII接口连接示意图

在时钟方面,88e1111需要一个外接的25 MHz时钟为其提供钟源,RGMII端收发时钟使用P2020芯片的eTsec模块提供。

88e1111与P2020的MDIO模块连接,MDIO最多可以识别32个物理芯片,使用物理芯片之前需对其进行配置,配置信息包括芯片地址、模式等。通过连接配置pin,对PHY芯片的CONFIG[0:5]引脚进行硬件配置,使芯片工作在需要的状态下,其中ANEG[3:0]配置为“1110”,使得芯片支持自动翻转,速率自适应。SEL_TWSI配置为“0”,使能MDC/MDIO接口,使得P2020可以实时对PHY芯片进行控制。

2.2 千兆网驱动设计

平台使用WindRiver公司的VxWorks6.9作为操作系统,使用WindRiver WorkBench3.3作为开发环境。VxBus是风河公司从VxWorks6.2开始引入的操作系统驱动程序架构,集成了多种通用驱动开发程序,并将驱动的安装配置集成到了开发环境WorkBench中。VxBus架构将各种不同功能设备集成至同一的架构中,驱动的大部分配置在hwconf.c中完成。文件中有2个关键的数据结构:hcfResource和hcfDevice。PLB为processor local bus的缩写,是一种虚拟总线,VxBus架构下设备驱动形成一个链表,直接或者间接挂接在PLB上,hcfDevice是PLB上的设备列表,包括设备名、设备号、总线类型以及hcfResouce等信息[11]。具体配置方法如下:

在config.h文件中加入对VxBus以及相应网口驱动的支持,例如INCLUDE_VXBUS、INCLUDE_ETSEC_VXB_END、INCLUDE_END、INCLUDE_MII_BUS以及INCLUDE_GENERICPHY等。此外还要修改hwconf.c文件:

Const struct hcfResourcetsecVxbEnd0Resources[]=

{

{“regBase”,HCF_RES_INT,{(void*)CCSBAR+0x24000}},/*基地址寄存器地址*/

……

{“phyAddr”,HCF_RES_INT,{(void*)0x1a}},/*phy地址*/

{“miiIfUnit”,HCF_RES_INT,{(void*)0}},/*Unit号*/

}

Const struct hcfResourcemv88E1xx0Resources[]=

{

{“phyAddr”,HCF_RES_INT,{(void*)0x1a}},

……

{“nonGenericBSPMod”,HCF_RES_INT,{(void*)MV88E_CDS2020_BSP_MOD}},

}

Const struct hcfDevicehcfDeviceList[]=

{

{“motetsec”,0,VXB_BUSID_PLB,0,tsecVxbEnd0Num,tsecVxbEnd0Resources},

{“mv88e1x11phy”,0,VXB_BUSID_MII,0,mv88E1xx0Num,mv88E1xx0Resources},

……

}

VXB_INST_PARAM_OVERRIDEsysInstParamTable[]=

{

{“mv88E1x11phy”,0,“mode”,VXB_PARAM_INT32,{(void*)MV88E_MODE_RGMII}},

……

}

VxBus驱动初始化主要在sysLib.c中完成,driverHwInit调用hardWareInterFaceInit()作为VxBus驱动的初始化入口函数,随后调用hardWareInterBusInit()完成VxBus驱动初始化大部分任务。

2.3 P2020复位/上电模块设计

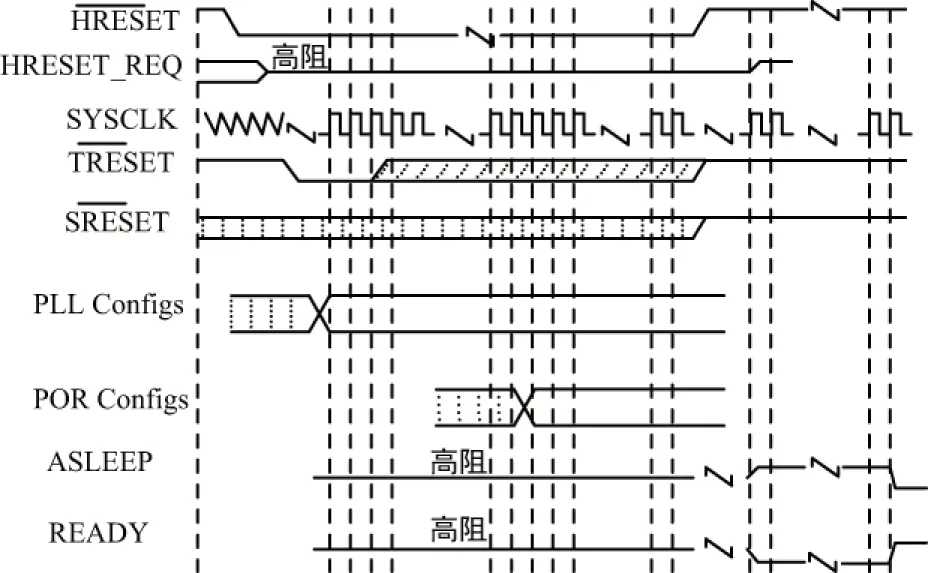

CPU的上电时,需要对相关模块进行复位,并且时钟遵循相关的时序要求,芯片要求具体复位顺序如下:

① 按照芯片手册指示加载电源,满足硬件要求;

② 系统置位HRESET和TRST,将所有寄存器初始化到默认值,大多数I/O被驱动为三态(一些时钟、时钟使能及信号被设为有效);

③ 系统应用稳定的SYSCLK和稳定PLL配置输入,设备时钟锁相环锁定SYSCLK;

④ P2020使能IO驱动;

⑤ E500核PLL配置输入被应用,允许e500 PLLs开始锁定设备时钟(CCB时钟);

⑥ 锁定时钟后,CCB时钟循环大约50 μm后;

⑦ 内部对e500核硬复位取消,对于PLL和其他IO模块的软复位取消,PLL开始锁定;

⑧ eLBC总线根据配置项中的设置进行启动地点配置;

⑨ 启动位置配置完毕后,READY和ASLEEP信号指示对应状态[12]。

启动时序如图3所示。

图3 P2020上电启动时序

电路设计时,需要对上电配置项进行设置,统筹规划整版芯片的上电复位控制顺序。上电复位脚在P2020中与其他功能引脚复用,在上电复位时,引脚用于系统状态配置,在上电复位完成后,引脚用作其他功能引脚用。由于一部分功能引脚配置值需要根据环境进行配置,因此一部分功能引脚使用CPLD进行控制,另外一些由上下拉电阻来进行配置固化,相关配置如下所示:

Cfg_sys_pll[0:2]决定CPU的BBC对SYS_CLK的倍频;

Cfg_ddr_pll[0:2]决定DDR的时钟频率;

Vcfg_core0_pll[0:2]/cfg_core1_pll[0:2]决定core0/core1对CCB倍频;

Cfg_cpu0_boot和cfg_cpu1_boot决定复位时执行boot的core;

Cfg_rom_loc[0:3]决定bootrom的位置。

由CPLD配置的主要是系统中核心频率、DDR频率、CCB频率以及启动位置。此外,CPLD还包括FLASH等外围电路的上电复位控制逻辑,以及外接看门狗电路的控制。P2020复位时可以从连接在LocalBus的CS0的NorFlash执行第一条指令,从而完成系统的上电复位流程。

2.4 串行模块设计

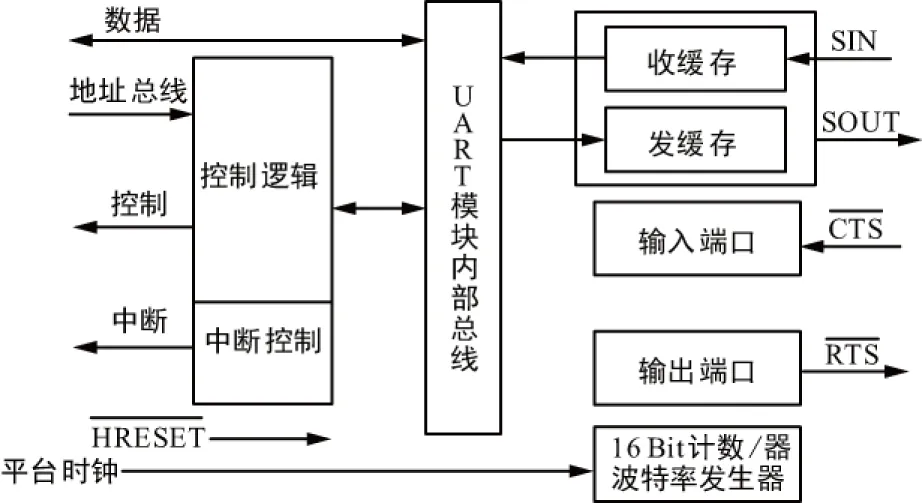

UART是一种应用广泛的短距离串行传输接口,常常用于短距离、低速低成本的通信中[13-14]。异步通信中,数据按帧传送。帧格式中,一帧数据由一个起始位、8位数据位、奇偶校验位(可省略)、停止位所组成。P2020处理器集成了2个独立的UART接口,每个UART通过CCB时钟进行锁定。UART为点对点的模式,每个UART接口包括以下内容:收发缓存器、流控端口(CTS、RTS)、用于波特率发生器的16位计数器、中断控制逻辑器。模块结构如图4所示。

图4 UART模块结构示意图

模块提供了全双工异步收发器,通过SIN和SOUT实现串行数据的收发,时钟速率通过模块可配置,钟源为P2020内部的CCB时钟。在收发过程中,模块通过SIN收取数据,将其转换为并行格式,检查开始位、停止位和校验位,在FIFO模式下,将开始位、停止位和校验位移除后,将数据放到收发缓存中,实现对数据的收发。本平台中,通过外接RS232/RS485接口芯片,结合两个UART模块,对外提供一个RS232和一个RS485串行接口,满足板卡对接口的设计要求。

3 平台测试及结果

嵌入式平台应用于TDMA访问控制,应用软件使用Vxworks操作系统。测试环境贴近应用环境,亦选用Vxworks操作系统。ICE2 是windriver公司出品的一款仿真器,基于WindRiver workbench OCD调试环境,可以实现对嵌入式板卡的在线烧写调试等工作。板卡的bootrom文件大小为1 MB,将其放置至系统物理地址的最末端,使用ICE2将Vxworks的1 MB大小的Bootrom烧写到0xfff00000至0xffffffff处。连接平台调试串口与网口,串口可以正常打印Vxworks的bootline信息,配置bootline为:

boot device:配置启动方式。键入“motetsec0”,表示从eTSEC0加载,通过主机上的FTP服务器完成程序的启动;

File name:键入“vxworks”,表示程序启动时的文件名;

Inet on ethernet(e):键入IP地址,表示eTsec0的网址;

Host inet(h):键入主机的IP地址;

User(u):表示登录主机FTP服务器时的用户名。

通过网络加载,可以正常加载Vxworks镜像。

通过网络分析仪对平台的3个eTsec千兆网口进行测试,通过更改PHY芯片的硬件配置字,将PHY芯片设置为环回模式。连接网口至网络测试仪,参考RCF2544测试规范,测试包长使用64 B、512 B、1 518 B等。测试次数设定为20次,不间断压力测试时间为24小时,经过测试,不同包长测试结果皆可达到限速1 Gbps,满足平台的设计要求。

TDMA通信体制要求设备能够对数据收发进行精确定时,满足时隙运算的要求。依托本文平台的高速以太网接口,TDMA业务及控制信息能够实现在访问控制平台与信道之间的高速可靠传输,同时提高缓存区的效率,提高TDMA帧计划的计算速度,使得系统能够高效、快速地实现TDMA通信。

4 结束语

介绍了一种基于P2020处理器的卫星TDMA访问控制平台,描述了平台的功能和特点,对整个模块的硬件计算进行了说明。分析了P2020处理器在TDMA访问控制平台中的优点,阐述了平台的实用价值,该平台应用于TDMA卫星通信终端,作为访问控制板卡,为终端提供了多个高速千兆以太网接口,以及RS232、RS485等接口,依托P2020较强的处理能力和较低的功耗,满足了大容量、强实时性的TDMA通信终端的需求。

[1] 李冬浩,吴昊.MF-TDMA卫星通信系统的IP接入设计[J].计算机与网络,2011,13:47-49.

[2] 王丽娜,王兵.卫星通信系统(第2版)[M].北京:国防工业出版社,2014.

[3] Dipto C,Casey C.PowerPC概念体系结构与设计[M].北京:电子工业出版社,1995.

[4] 高宇,尤祖光.PowerPC多核技术在数字信号处理中的应用[J].无线电工程,2014,44(9):52-55.

[5] 夏航,望溢.基于多核处理器P2020的综合数据处理模块设计及应用[J].航空电子技术,2012,43(3):30-35.

[6] Conductorn Inc. Freescale Semiconductor Corp.QorIQTMP2020 Communications Processor Product Brief[M].USA:Freescale Semiconductor,2009.

[7] 侯义合,张冬冬,丁雷.基于FPGA+MAC+PHY的千兆以太网数传系统设计[J].科学技术与工程,2014,14(19):275-279.

[8] 侯义合. 基于QWIP-LED器件的红外成像探测系统技术研究[D]. 上海:中国科学院研究生院(上海技术物理研究所),2014.

[9] 胡阳.基于POWERPC的嵌入式无线通信控制单元设计[D].北京:北京邮电大学,2015.

[10]Marvell Semiconductor Inc.. 88E1111 Datasheet[M].USA:Marvell Semiconductor,2004.

[11]付月生,王丽.基于VxBus的驱动程序架构分析[J].计算技术与自动化,2012,31(2):98-102.

[12]Conductor Inc.Freescale Semiconductor Corp.QorIQTMP2020 Integrated Processor Reference Manual[M].USA:Freescale Semiconductor,2009.

[13]苏漪,谭潭.FPGA与DSP接口(UART)的设计实现与验证[J].无线电工程,2009,39(10):45-47.

[14]吴海明,童怀.计算机与CPLD串口通信[J].中国集成电路,2007,16(12):77-80.

Design of Embedded Platform for Access Control of Satellite TDMA Based on P2020

YANG Xu-guang

(The 54 Research Institute of CETC,Shijiazhuang Hebei 050081,China)

TDMA technology has many advantages such as high quality of communication,large system capacity and so on. This paper presents the design of an embedded platform for satellite TDMA access control based on P2020 processor. The feature and design scheme of the embedded platform are analyzed,the P2020 processor is briefly introduced. The Ethernet module,serial module and processor reset module are described in details,the driver of the Ethernet module is designed,and the platform is tested by experiment. The test result shows that the platform meets the requirements of large-capacity and multi-mode TDMA satellite communication system applications.

P2020;embedded;TDMA;access control

10. 3969/j.issn. 1003-3114. 2017.04.04

杨旭光.基于P2020的嵌入式卫星TDMA访问控制平台设计[J].无线电通信技术,2017,43(4):13-17.

[YANG Xuguang. Design of Embedded Platform for Access Control of Satellite TDMA Based on P2020 [J]. Radio Communications Technology,2017,43(4):13-17. ]

2017-03-28

杨旭光(1986—),男,工程师,主要研究方向:嵌入式系统软硬件开发。

TP391.4

A

1003-3114(2017)04-13-5