一种抗注入攻击的高速AES算法设计

2017-06-27杨自恒

杨自恒,王 宇

(黑龙江大学 电子工程学院,黑龙江 哈尔滨150080)

一种抗注入攻击的高速AES算法设计

杨自恒,王 宇

(黑龙江大学 电子工程学院,黑龙江 哈尔滨150080)

为了提高AES抵抗故障注入攻击的能力,各种各样的抵抗措施相继被提出。很多嵌入式系统中,都使用AES来提高系统的安全性。然而,自然和恶意注入故障降低了AES算法的鲁棒性,并且还可能导致私人信息泄漏。对并发的故障检测方案进行了研究,用以实现可靠的AES算法,进而提出了一种基于改进型AES结构的故障检测方案。将轮变换拆分成2部分,并且在这2部分中间加入了流水设计。仿真结果显示,其错误覆盖率达到了98.54%。此外,该方案和前人所提出的方案都在最新款的Xilinx Virtex系列FPGA芯片上得到了实现。对这些方案的硬件开销、频率及吞吐量进行比较,结果显示,该方案要优于前人所提出的方案。

密码;AES算法;故障检测;FPGA实现;嵌入式系统

0 引言

使用AES加密算法的目的是为了保证信息的安全传输,并且只有具有相同秘钥的接收系统才能完整地恢复出原始数据。然而,由于存在着大量的恶意注入故障,这时就无法保证传输过程中AES算法的可靠性。在文献[1-2]中介绍了几种针对AES的故障攻击方案。差分故障分析(DFA)是基于对AES算法的故障注入来获取加密信息。当处理算法执行时,攻击者将故障注入,这将会扰乱正常的执行行为并且产生错误密文。因此,在一定数量的故障注入之后,攻击者就可以通过分析错误密文进而猜测出秘钥。为了使加密算法可以更有效地抵抗故障攻击,科学家们又提出了多种故障检测方案。

文献[3]针对AES提出了一个轻量级并发故障检测方案。作者表示:当该方案在FPGA上实现时,该方案具有更优的硬件资源和时间复杂度,然而,该方案并不适用于基于查找表的S盒与逆S盒的实现。在文献[4]当中,Chu等人提出了一种全新的故障检测方法,这种方法是使用多项式余数系统(PRNS)实现AES算法。该故障检查方案具有很高的错误覆盖率,并且因为其自身的分布和并行特性,使得PRNS具有抵抗旁路攻击的特性。然而,该方案需要额外3个S盒去计算剩余的多项式,这将会增加大约81%的硬件开销,并且增加受到功耗攻击的可能性。在文献[5]中,Mestiri等人提出了基于信息冗余的故障检测方案,该方案的故障覆盖率达到了99.998%。而Mestiri等人发表的另一篇文章[6]则提出了一种基于混合冗余的故障检查方案。该方案中的行变换和逆行变换是基于位级置乱的方法,作者称,这个方案的故障覆盖率达到了99.999%。文献[7]提出了基于时间冗余的故障检测方案:每轮加密执行2次,并且结果之间相互比较。虽然该方案可以检测到几乎所有的故障,但是只有当执行频率在限定值时,其损耗才可以被接受。

本文提出了一种新的故障检测方案,以获得一种可靠的AES加密方法。本文改进了AES轮结构:每一轮加密操作被分解成2条流水线结构以便于上半轮操作检查故障,下半轮操作去执行加密,反之亦然。

1 背景简介

1.1 AES加密算法

美国国家标准技术研究所在2000年10月发布了基于Rijndael算法的高级加密标准(AES)[8]。AES代替了从1976年沿用至今的数据加密标准(DES)。时至今日,科学家们已经提出了多种用于提高AES算法效率的超大规模集成电路,并且这些电路的性能已经在专用集成电路和FPGA系统上得到了验证[9-11]。在AES算法中,除最后一轮外,其他每一轮都要执行这4种变换:子字节、行移位、列混合和轮秘钥加,但是在最后一轮中是不需要执行列混合变换的。

1.2 利用故障检测方案抵抗故障攻击

故障注入攻击是一门很实用的技术,可以有效地破解无保护的加密算法。在执行过程中,该技术是注入一个或者几个故障,使用错误的输出信息获取在密文当中的秘钥信息。

从一些文献可知,大部分的故障检测方案都是基于某种类型冗余。在硬件冗余中,两个硬件同时使用相同的数据去进行相同的计算。经过计算之后,将结果进行对比,并且将每个对比结果认为是一个故障。该技术的优点是可以检测出瞬态和永久的缺陷。然而,要实现这点至少需要100%的硬件开销。在时间冗余当中,相同的硬件处理相同的数据需要重复执行两次相同的过程,这将会使用最少的硬件开销,但是,需要100%的时间开销。在信息冗余中,需要注入的或者发生的故障的检测,通常使用两种技术:奇偶校验和非线性鲁棒码,如图1所示。

图1 抵抗故障攻击方式

2 AES实现

图2是32位的AES算法[12]。这需要4组32位输入数据和4组32位秘钥数据。加密和解密的过程如下所述,并且输出也是4组32位数据。

① 输入接口用于加载输入数据模块,并且存储等待加解密的输入模块,明文和秘钥的长度是32位,但是输出的位宽为128位[13],所以当加载时,需要输入数据缓存区和输入秘钥缓存区进行数据缓存;

② 控制指的是状态控制,它为其他单元产生控制信号;

③ AES轮是去执行输入数据的加密和解密的过程;

④ 秘钥扩展是计算基于单一外部秘钥的一组内部秘钥;

⑤ 输出接口采用128位长度输出数据,采用与输入数据/秘钥缓存相同的方法,将数据长度转换成4个32位的数据;

⑥ AES库:包含有不同的AES功能,例如S盒、行变换、列混合以及添加轮秘钥等。

图2 32位AES框图

3 提出针对AES的缺陷检测方案

在说明本文提出的缺陷检测方案之前,首先,先说明一下,时间冗余技术是如何应用到AES加密技术中的。图3显示了时间冗余技术如何应用到AES加密技术当中[14-15]。

图3 AES算法的基本时间冗余方案

在图3中,使用相同的AES结构去执行加密和相同输入的重加密。在加密执行结束时,结果会相互比较,并且每一个差异都会被认为是一个故障。每轮都需要2个时钟周期:第1个时钟周期用来执行加密,与此同时,第2个时钟周期对相同输入数据进行了重加密并且比较结果。该技术的缺点是:需要100%的时间开销。

提出了一个针对AES的故障检测方案的硬件实现。该方案是一种改进型的时间冗余方案,可以检测在运行时的瞬态单一故障和复杂故障。针对这个方案,AES轮变换被分解成2部分,这2部分,使用流水线寄存器连接起来。每部分都会被执行2次,并且结果会和缺陷检测目标进行比较。因为在轮变换当中加入了流水线寄存器,最大频率就会增加,因此,提出方案的吞吐量要比原始的AES加密算法的吞吐量略低。

AES轮分为2部分。第1轮操作去检查错误,与此同时,第2轮操作也被执行,反之亦然。图4为将时间冗余技术加入到AES算法的结构图。

图4 具有故障检测方案的AES轮

当CR1和CR2寄存器相比较时,轮计算输出数值。第1轮操作,由输入值计算中间值,并且将这些存储到流水线寄存器中。由中间值得到计算轮的输出数值。这2个操作必须有相同关键路径延迟。在图4中,寄存器在每个时钟周期去加载以执行轮操作和故障检测过程。

第1个时钟周期,起始轮执行明文与初始秘钥异或。在接下来的2个时钟周期中,状态信息通过第1个AES轮的前半轮(R1,1)。R1,1起始于第2个时钟周期。在第3个时钟周期,第1个AES轮的后半轮开始执行使用相同输入的R1,1进行加密。R1,2在第4个时钟周期开始加密,在相同的时钟周期中CR1和CR2是用来存储每半轮的输出值,之后,CR1和CR2中的值会分别与PR和OR中的存储值相互比较。CR1和CR2寄存器分别在奇时钟周期和偶时钟周期加载,用来存储输出值,之后进行比较。流水线寄存器和异或寄存器在所有时钟周期都会被加载。R1,1的错误检查在奇时钟周期执行,R1,2的错误检查在偶时钟周期执行。

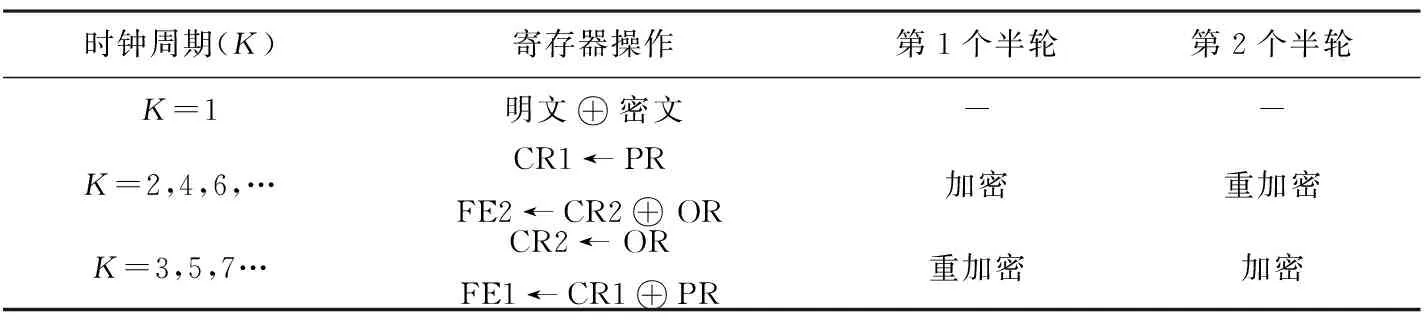

从表1看出:半轮操作应该在每个时钟周期进行加密和重加密的切换。第1轮比较将会发生在第3个时钟周期,第1个半轮正常的加密结果将会和第1个半轮中的重加密结果进行比较。应当注意的是:虽然加密过程是在第2个时钟周期完成的,但是结果直到第3个时钟周期才会被使用,上半轮的输出结果可以用于故障检测。

表1 已提出结构的操作顺序

时钟周期(K)寄存器操作第1个半轮第2个半轮K=1明文密文--K=2,4,6,…CR1←PRFE2←CR2OR加密重加密K=3,5,7…CR2←ORFE1←CR1PR重加密加密

4 AES轮的具体执行

提出每半轮加密过程的具体实现。第1个半轮主要完成S盒和行变换,而第2个半轮则执行列混合与轮秘钥加。

4.1 AES第1个半轮的具体实现

在实现S盒和逆S盒操作时候,提出了2种方法。第1种方法是:使用查找表(LTU)的方法确定每个输入对应的S盒和逆S盒的值。将所有的值都存储在ROM中所形成的一张表中[13]。当S盒与逆S盒变换执行时,原值的置换值都是由查找表提供的。第2种方法是在有限伽罗华域来实现S盒与逆S盒。这种方法需要花费大量的硬件资源并且还需要消耗很长时间。相比于复域变换,使用查找表方法的S盒与逆S盒变换,是一种更快更简单的方法。在这项研究当中,本文使用查找表的方法来实现。

行移位是在不同的字节数状态行上的循环移位操作。状态的第1行保持不变,而第2行左移1个字节,第3行左移2个字节。因为行移位执行时,状态矩阵最底下3行进行循环左移,所以不会对字节变换的输出产生影响。之后,字节替换和行移位是在同一个单元中执行完成的。R1,j的具体实现如图5所示。

图5 上半轮(R1,j)的硬件实现

4.2 AES的第2个半轮的具体实现

通过文献[1],列变换的实现等式是:

(1)

考虑到等式:03=02⊕01,上述所有方程组,可以使用02的乘法方程式进行重写。新方程组为:

(2)

02乘法运算使用X时间函数来完成,X时间函数利用3异或门实现。轮秘钥加是异或运算,它是在列混合的结果中添加轮秘钥,其中轮秘钥是由秘钥扩展序列产生的,R2,j的具体实现如图6所示。

图6 下半轮(R2,j)的硬件实现

5 改进型高速AES算法故障检测评估

为了评估所提出设计的故障检测能力,将不同情况下的单字节和多字节故障注入到该方案当中。具体为:

① 故障注入到初始轮、第1个半轮R1,j和第2个半轮R2,j;

② 故障注入到加密数据路径中的多路复用器、多路输出选择器和状态寄存器当中;

③ 故障注入到故障检测数据路径、比较寄存器和比较器;

④ 每轮中,相同故障值被注入到相同位置2次。

在本文提出的方案中,已提出了单一瞬态故障和多重瞬态故障。故障位置被随机选择产生单比特故障和多比特故障。对于单比特故障,瞬态故障被随机插入到上述故障点的任意一个故障点中。

使用ModelSim进行仿真,在AES加密的第1个半轮输出和第2个半轮当中使用故障指示标志。根据所提出的设计方案的输出,能够将实验结果划分为4类(如表2所示):

① 静默故障:输出值是预期值并且没有检测到错误,这就意味着改缺陷对提出的方案没有影响;

② 假阳性故障:输出值为预期值,然而在系统当中可以检测出错误;

③ 未被检测出的故障:输出值不正确,但是无错误被检测出来,这就意味着缺陷检测系统无法检测出注入或者发生的故障;

④ 已检测出的故障:输出值不是预期值,并且故障被检测到,这就意味着通过提出的方案,可以检测出故障。

表2 加密过程中的错误覆盖率

故障类型故障覆盖率/%静默故障假阳性故障未检测出故障已检测出故障单比特3.57310.3340.13585.958多比特突发故障N=21.7685.2740.08692.958N=30.9062.5910.01596.488N=40.3861.2710.00598.338N=50.1150.6170.00399.265随机故障0.4041.0420.01498.540

很显然,错误检测方案应该最大限度减少未被发现故障的发生。如果在没有故障发生的情况下,绝不允许第2类故障的发生。第1类故障在本质上取决于结构特性,而不是取决于提出的错误检测方案。

单一故障:认为第1类故障为单一缺陷。对于这种故障,假设单比特瞬态故障随机地插入到上述提出的故障点的任意一位中。使用4 000个单比特故障对其进行验证。瞬态故障的发生位置也是随机选择的。被检测错误的百分比的定义为:被检测缺陷的数量相对于注入到设计当中的单比特缺陷总量的比值。从表2当中的结果可以看出:大部分的单比特瞬态缺陷在检测错误或者假阳性都被认为是一个静态缺陷,只有很少一部分的输入故障没有被检测到。

多重故障:由于DFA攻击参考故障模型的存在,使得多比特故障的覆盖率更高。在仿真中,使用2种方式注入多比特瞬态缺陷,例如:突发故障和随机故障,并且获取这2种故障的错误覆盖率,具体情况如下:

突发故障:认为多比特瞬态故障是突发故障。对于这种类型的故障,假设瞬态故障发生在上述一个或多个故障点当中。之后,在图4当中使用2个标志获得错误覆盖率,本方案已经使用了4 000个故障进行证明。注入故障时,由128位当中的错误位数来区分。通常,故障检测改善了伴随着故障数量增加的故障覆盖率。这是因为:大部分的故障位会引起在半轮计算输出中的大量位变化,相应的下半轮计算输入,这将增加检测缺陷的可能。从表2结果中可以看出,当故障目标在可能的故障位置时,故障可能是静态的、可被检测的或者是假阳性的。只有很少一部分的故障不能被检测到,并且覆盖率越高时,缺陷多样性就越高。

随机故障:认为第2类故障是随机故障,将随机位数故障插入到上述提出的一个或者多个故障点中。随机故障的故障覆盖率如表2所示。当注入一个随机位数瞬态故障,未检测故障的概率是0.014%,然而通过提出的故障检测方案,98.54%的注入故障或者随机发生的故障可以被检测到。因此,本文提出的这种方案可以对自然和恶意注入的故障提供足够的安全保护。

6 FPGA实现

在FPGA上实现本文所提出的方案并且验证上一节提出的结论。128位AES的两种结构得到了实现,第1种结构是没有缺陷检测,而第2种结构是有缺陷检测。这2种结构使用VHDL语言编写。使用的FPGA型号为Virtex-5的XC5VFX70T。对2种结构的AES加密和解密的综合结果,如表3所示。

表3 AES加密与解密过程的结果展示

AES-128加密解密硬件开销/片频率开销/MHz吞吐量开销/Mbps硬件开销/片频率开销/MHz吞吐量开销/Mbps无故障检测429237.032528.33532218.822334.08有故障检测491(14.45%)353.23(49.02%)2055.17(18.71%)715(34.40%)314.04(43.51%)1827.14(21.72%)

由表3得到有故障检测和无故障检测的占用片载的数量、频率、吞吐量、硬件开销和频率开销的测试结果。当无缺陷检测的AES实现时,需要频率为237.07 Hz的片载资源共429片。有缺陷检测的AES算法占用了超过14.45%的片载,但比原AES的频率使用率高出49.02%。无缺陷检测的AES加密的最大频率是第1种实现方案频率的2倍。这是因为:实际中,AES实现的关键路径并没有分裂成两个具有相同延迟的部分,而造成这种差异的第2种原因是:将多路复用器添加到第1和第2个AES半轮当中。

无缺陷检测的AES算法在执行时候,需要12个时钟周期。表3中显示,这是相比于无缺陷检测能力的AES解密的实现,本文提出的缺陷检测方案会导致在加密过程中约18.71%吞吐量减少和约43.51%频率占用率的减少。

表4 AES具有故障检测方案的AES加密结果比较(-表示减少)

AES-128加密故障覆盖率/%开销/%单比特多比特硬件频率吞吐量本文方案85.95898.5414.4549.02-18.71文献[15]10099.99626.9≈0≈0文献[8]10093.7581≈0.17--文献[7]------36----(15-55)文献[14]100752.3-28.29-50

表4比较了本文提出的故障检测方案与相似4类方案的故障覆盖率、硬件开销、频率开销和吞吐量开销。相比于文献[7]和文献[8],提出的方案具有最小的硬件开销和最高的频率。从保密的角度看,本文提出的方案的故障覆盖率达到了98.54%。在文献[8]检测方案中,故障覆盖率为93.75%,并且对原始实现的频率的影响很小,但是在硬件成本上的消耗更高,需要81%的硬件开销。文献[7]中使用奇偶校验去检查AES中的故障,这种方案的硬件消耗是上一种方案的2倍[7,14]。文献[7]的方案需要更多的限制,因此其需要的硬件开销是本文提出方案的2倍(大约36%)。

虽然文献[14]略微影响原始的实现区域,该方法引起了了大约28.3%的频率下降并且引起了大约3倍的吞吐量的减少。从安全的角度来看,在故障注入到轮操作中,这个方案并没有得到足够的验证。因此,这个系统的缺陷覆盖结果是高度依赖于该文献所提出的假设。

7 结束语

本文研究了AES加密和解密过程中的若干故障检测方案,提出了依靠S盒和逆S盒的结构的一种新的故障检查方案。仿真结果显示,该方案可以检测98.54%的自然和突发性故障。其余的1.45%则为静默故障、假阳性故障和不可检测故障。此外,所提出的缺陷检测方案以及当前所提出的所有方案都在最新的Virtex FPGA上得到了验证。当AES在FPGA上实现时,该方案的频率开销大约是49.02%。相比于其他具有相同的缺陷覆盖的故障检测方案,该方案具有更高的频率开销。由仿真结果以及可接受的缺陷覆盖可知:本文提出的方案,具有最高的频率、合理的硬件和时间复杂度开销。因此,该方案可以实现更可靠的AES加密和解密结构。

[1] Tunstall M,Mukhopadhyay D,Ali S.Differential Fault Analysis of the Advanced Encryption Standard Using a Single Fault[J]. Community Mental Health Journal,2011,49(6):658-667.

[2] Ali S,Mukhopadhyay D,Tunstall M.Differential Fault Analysis of AES Using a Single Multiple-Byte Fault[C]∥Proceedings of the Workshop on Fault Diagnosis and Tolerance in Cryptography,2011:35-42.

[3] Mozaffari-Kermani M,Reyhani-Masoleh A.A Lightweight High-performance Fault Detection Scheme for the Advanced Encryption Standard Using Composite Fields[J].Very Large Scale Integration Systems IEEE Transactions on,2011,19(1):85-91.

[4] Chu J, Benaissa M.Error Detecting AES Using Polynomial Residue Number Systems[J].Microprocessors & Microsystems,2012,37 (2):228-234.

[5] Mestiri H,Benhadjyoussef N,Machhout M,et al.High Performance and Reliable Fault Detection Scheme for the Advanced Encryption Standard[J].International Review on Computers & Software,2013,8(3):730-748.

[6] Mestiri H,Benhadjyoussef N,Machhout M,et al.A Robust Fault Detection Scheme for the Advanced Encryption Standard[J].International Journal of Computer Network & Information Security,2013,5(6):49-55.

[7] Maistri P,Leveugle R.Double-data-rate Computation as a Countermeasure Against Fault Analysis[J].Computers IEEE Transactions on,2008,57(11):1528-1539.

[8] 何明星,林昊.AES算法原理及其实现[J],计算机应用研究,2002,19(12):61-63.

[9] Mestiri H,Machhout M,Tourki R.Performances of the AES Design in 0.18μm CMOS Technology[C]∥Proceedings of the 7th International Conference on Design & Technology of Integrated Systems in Nanoscale Era,2012:1-6.

[10]Moh’d A,Jararweh Y,Tawalbeh L.AES-512:512-bit Advanced Encryption Standard Algorithm Design and Evaluation[C]∥ Proceedings of the 7th International Conference on Information Assurance and Security,2011:292-297.

[11]蔡琛,陈运,万武南,等.基于主成分分析的AES算法相关功耗分析攻击[J].电子技术应用,2015,41(8):101-105.

[12]Mestiri H, Lahbib Y,Machhout M,et al.Multi-level AES Design Security:from SystemC-TLM to FPGA[J].Journal of Theoretical & Applied Information Technology,2014,66(2):401-408.

[13]Rahman T,Pan S,Zhang Q.Design of a High Throughput 128-bit AES (Rijndael Block Cipher)[J].Lecture Notes in Engineering & Computer Science,2010,2181(1):134-138.

[14]Rajendran J,Borad H,Mantravadi S,et al.SLICED:Slide-based Concurrent Error Detection Technique for Symmetric Block Ciphers[C]∥Proceedings of the International Symposium on Hardware-Oriented Security and Trust,2010:70-75.

[15]Mozaffari-Kermani M,Reyhani-Masoleh A. Concurrent Structure-independent Fault Detection Schemes for the Advanced Encryption Standard[J]. IEEE Transactions on Computers,2010,59(5):608-622.

Design of AES Algorithm Against Injection Attack

YANG Zi-heng,WANG Yu

(School of Electronic Engineering,Heilongjiang University,Harbin Heilongjiang 150080,China)

To secure the Advanced Encryption Standard against physical attacks known as fault injection attacks,different countermeasures have been proposed. The AES is used in many embedded systems to provide security. However,the natural and malicious injected faults reduce its robustness and may cause private information leakage. The concurrent fault detection scheme is studied to realize the reliable AES algorithm,and then a new fault detection scheme based on modification of the AES architecture is proposed. The round AES transformation is broken down into two parts and a pipeline stage is inserted in between. The simulation results show the fault coverage reaches 98.54% for the proposed scheme. Moreover,the proposed and the previously reported fault detection schemes have been implemented on the latest Xilinx Virtex FPGAs. Their area overhead,frequency and throughput have been compared and it is shown that the proposed fault detection scheme outperforms the previously reported ones.

cryptographic;AES algorithm;fault detection;FPGA implementation;embedded systems

10. 3969/j.issn. 1003-3114. 2017.04.10

杨自恒,王宇. 一种抗注入攻击的高速AES算法设计[J].无线电通信技术,2017,43(4):40-46.

[YANG Ziheng,WANG Yu. Design of AES Algorithm Against Injection Attack[J]. Radio Communications Technology,2017,43(4):40-46. ]

2017-03-14

国家自然科学基金项目(60672011);黑龙江省科学技术计划项目(GZ06A101)

杨自恒(1972—),男,副教授,主要研究方向:嵌入式、信息安全。王 宇(1992—),男,硕士研究生,主要研究方向:嵌入式、信息安全。

TP391.4

A

1003-3114(2017)04-40-7