分布式测试系统时间同步技术的研究

2017-05-24牟宗磊

牟宗磊,宋 萍

(北京理工大学 仿生机器人与系统教育部重点实验室,北京 100081)

分布式测试系统时间同步技术的研究

牟宗磊,宋 萍

(北京理工大学 仿生机器人与系统教育部重点实验室,北京 100081)

分布式测试系统是集计算机控制技术、网络通信技术与多传感器信息融合技术于一体的复杂测控系统;与独立测试系统不同,在网络化分布式测试系统中,各测试装置需按通信协议与网关节点通信以完成相应的测试;不同测试装置在接收网关节点发出的信号时,由于传输距离不同会引起时延差;如果系统中的各个测试装置不具备统一的时间基准,那么得到的测试数据因为时钟差异将无法反映出信息的真实情况;因此,整个网络中所有测试装置需要保持时间同步;针对分布式测试系统时间同步的需求,对信号传输过程中的时延问题进行了研究,提出了一种基于FPGA的时延测量方法,对这种软硬件结合时延测量方法的实现原理进行了详细阐述,并进行了功能仿真及试验验证。

分布式测试系统;时延差;时间同步;时延测量;功能仿真

0 引言

分布式测试系统通常由分布在测试区域内的大量测试节点构成,节点之间按相关协议共同协作完成复杂的测试任务[1]。分布式测试系统的一个核心要求是各数据采集装置可以实现高精度同步采集。在分布式测试系统中,为保证各个测试装置具有统一的时间基准,一般只采用一个主节点时钟,其它从节点时钟通过直接或者间接的方式同步于主节点时钟。当前,基于硬件时间戳实现的高精度时间同步主要有两种方式,一种是基于GPS的时间同步,另一种是基于高精度时间测量芯片TDC-GP2的时间同步[2]。这两种时间同步方式具有精度高的优点,但应用成本高,需要在每个测试设备安装昂贵的芯片组件。另外,GPS模块对周围环境依赖性强,不适用于复杂的测试环境。

基于上述原因,本文对分布式测试系统的拓扑结构进行了研究,在考虑线性拓扑结构网络中中间节点对时间同步精度影响的情况下提出了一种适用于分布式测试系统的时间同步方法。本方法实现简单、通用性强,在提供与GPS相同时间同步精度的情况下,无需在测试装置上安装专用时钟芯片,只需对主从节点间的信号传输进行时延测量,就可以统一各个数据采集装置的时间基准,进而实现时间同步。

1 分布式测试系统组织体系

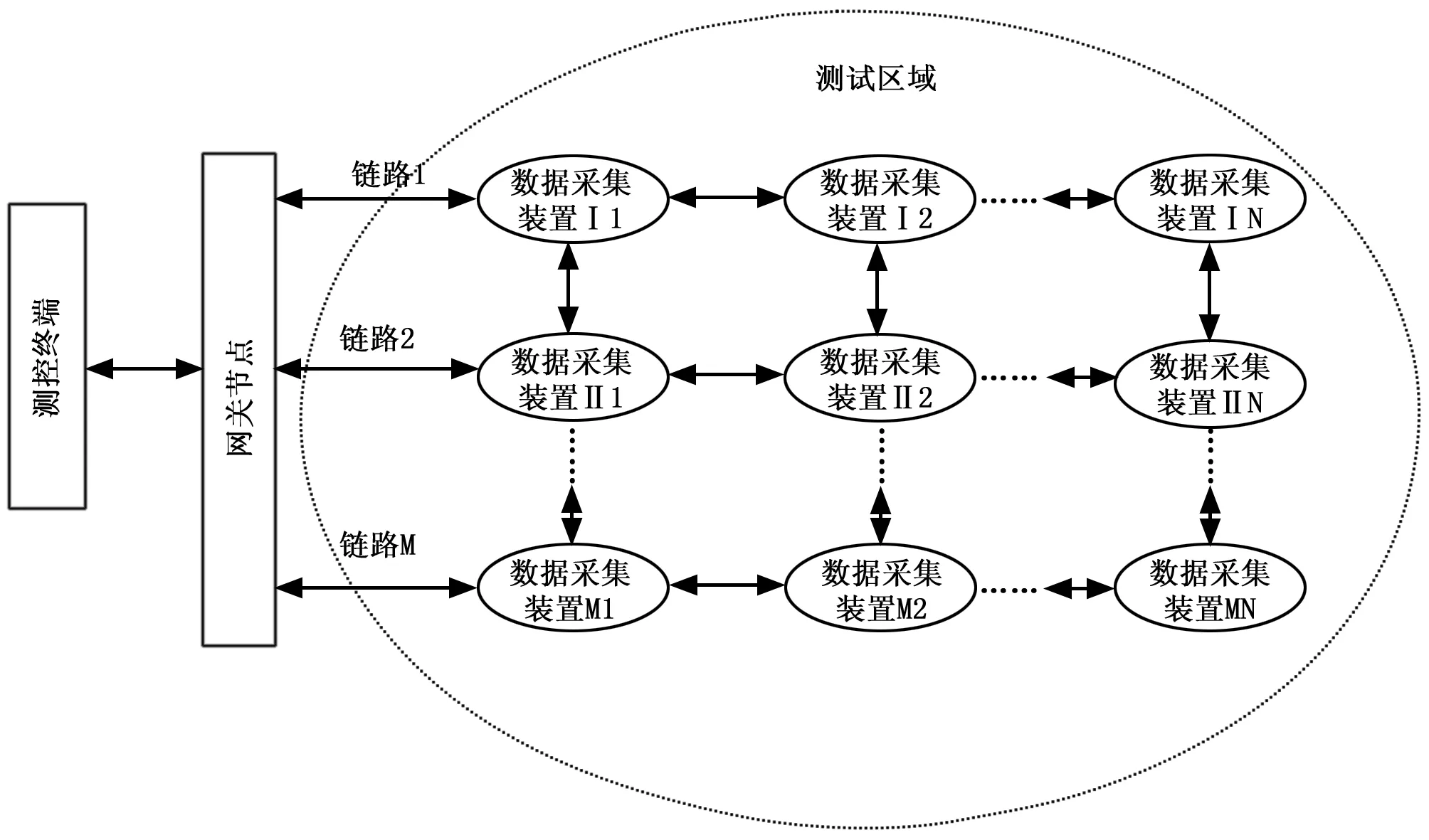

在分布式测试系统中,测控终端主要通过网关节点来实现对分布在测试区域内能独立完成测试任务的各个数据采集装置的集中控制,从而保证各个数据采集装置能够协调统一地完成测试任务。待测试结束后,数据采集装置在测控终端和网关节点的控制下通过无线或者有线传输的方式把采样数据回传给上位机,进而对数据进行实时处理或者后续处理[3]。本文所提及的基于光纤传输的分布式测试系统组织体系主要包括测控终端、网关节点和数据采集装置三部分,如图1。

图1 分布式测试系统组织体系简图

1.1 测控终端

测控终端主要通过网络接收远程客户端的测试命令,同时以有线传输的方式向网关节点发送测试命令和相关的配置参数,并且还能响应客户端处理与分析数据的请求,对网关节点回传的数据做后续处理分析。

1.2 网关节点

网关节点收到测控终端的测试命令之后,首先按通信协议对命令完成译码,然后执行后续的相应工作程序。网关节点不仅是整个系统的事件响应与调度中心,也是数据汇聚与交换中心。在这样的组织体系中,网关节点不仅拥有同时管理与挂接若干条测试链路的功能,而且能够合理且高效地将测控终端的请求分配给对应链路上的数据采集装置,进而更高效地实现多用户并发性测试请求和测试任务的协调性。

1.3 数据采集装置

每个布设在测试区域内的数据采集装置都可作为一个微型的测试系统。数据采集装置通常包含有传感器、信号调理放大电路、电源模块、数据采集与存储模块、数据传输模块、核心控制器等部件。应用于测试现场的数据采集装置采用时间同步技术使得所有的测试节点在某些关键时刻能够协调完成采集数据的任务,在短时间内完成用户的各种测试需求,并且快速释放系统资源,以便再次进行测试响应。

2 基于线性拓扑结构的时延测量

现有的分布式测试系统按通信媒介不同主要分为基于无线的分布式测试系统和基于有线的分布式测试系统,网络拓扑结构主要分为星型、树形、环形、总线型等拓扑结构。基于有线传输方式的传输媒介主要有电缆和光纤两种,而基于光纤传输的分布式测试系统因具有数据传输速度快、抗干扰强力强、安全性能高、可靠度高等优点而广泛应用于各种复杂的测试环境。本文所提及的分布式测试系统采用光纤传输模式。

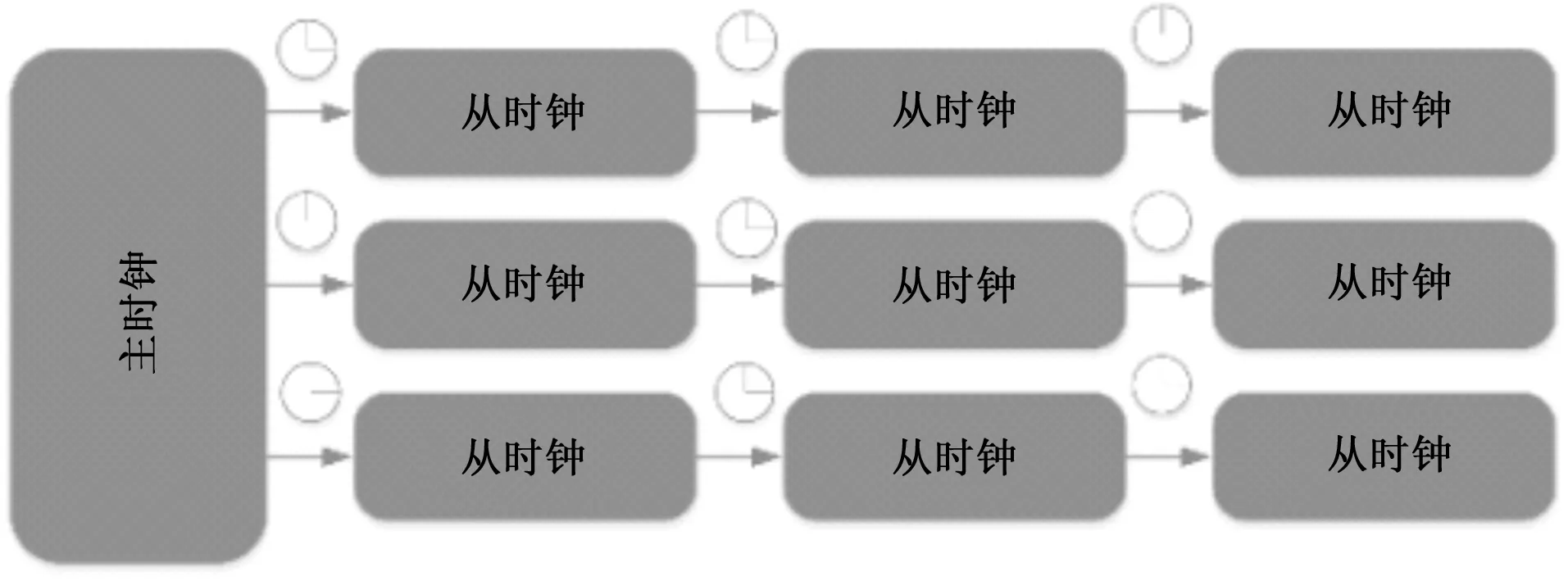

在基于有线传输的分布式测试系统中,为提高时间同步精度,一般只选用一个主节点时钟,其余从节点时钟通过直接或者间接的方式同步于主节点时钟,协同完成分布式测试任务。由于线性拓扑结构组网方式简单、易控制,被广泛应用于各种有线分布式测试系统中。在线性拓扑结构中,部分从节点时钟无法直接和主节点通信来实现时间同步,需要经过多个中间节点的消息包转发才能逐级实现时间同步,如图2。在消息包经过多个中间节点转发的过程中,传输时间受主、从节点时钟精度的共同影响误差较大,而且这种拓扑结构累积的时间误差将会随着中间节点数量的增加而增大,导致时间同步精度显著降低。在很多分布式测试系统中,我们不关注各个数据采集装置开始采集的绝对时间,而只需准确获知各个采集装置相对于主时钟的相对时间就可以统一时间基准,完成数据的后续处理工作。因此,在组建好主从式线性网络拓扑网络结构后,采用相关算法选择时间精度最高的主时钟设备,同时准确测得信号传输过程中各个数据采集装置相对于主时钟的时延值,为网络中的各个测试节点统一时间基准、实现时间同步,协作完成测试任务提供了保障[4]。

图2 线性拓扑网络主从时钟结构

2.1 时延测量原理

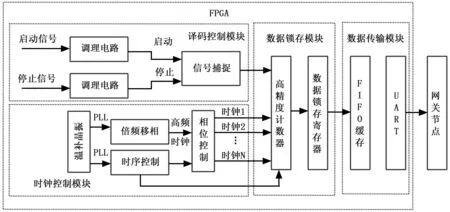

基于对系统时延测量速度、功耗、体积及抗干扰能力等方面的考虑,系统在具体实现上采用了FPGA作为主控芯片,在每个测试装置上采用成对的光纤收发一体模块进行通信,各个数据采集装置之间采用光纤进行串联通信,组成线性拓扑网络结构。基于FPGA的时延测量原理图如图3所示,即将译码控制模块、时钟控制模块、数据锁存模块以及数据传输模块全部集中在FPGA芯片上,使各部分性能达到最佳状态[5]。

图3 基于FPGA的时延测量原理图

FPGA是整个时延测量系统的控制核心,选用Altera公司的Cyclone II型系列FPGA。具体测试时,启动信号和停止信号首先要经过信号调理电路进行预处理,然后输送到FPGA数据锁存模块中进行测量。FPGA内部具有基准时间逻辑电路,这样就能捕获计数器当前的计数值,此值会被FPGA内部的RAM存储器进行存储,然后经过数据传输模块把测量结果传输给网关节点,网关节点汇聚各个测试装置的时延值后通过光纤上传给测控终端。

2.1.1 译码控制模块

经过调理电路调理后的启动信号和停止信号分别作为待测信号传输时延值的开始计数信号和停止计数信号,译码控制模块的功能是将测控终端的命令最终转化为各种使能信号及读写信号,从而完成对各相应寄存器的读写控制,进而实现对测试系统中各个数据采集装置功能的控制。该逻辑功能的完成需要底层的硬件驱动程序及相应的通信协议的密切配合,本系统根据自己定义的硬件通信协议实现测控终端对各个功能模块的控制[6]。

2.1.2 时钟控制模块

时钟控制模块主要由外部温补晶振和FPGA内部PLL(锁相环)构成。测量过程中,充分利用FPGA内部丰富的时钟资源和存储资源,借助PLL把板级的时钟进行倍频处理,从而可以产生一个高频率、低抖动、稳定度高的基准参考时钟,从而实现减小量化误差的目的。现场应用时可以根据测试需求对基准时钟进行倍频或者移相,满足不同测试精度的需求。

2.1.3 数据锁存模块

时延值的测量在FPGA内部转化为启动与停止两个脉冲信号上升沿之间时间间隔的测量,被测时间间隔主要有以下三部分组成:①采用脉冲计数法得到的基准时钟周期的整数倍NT;②启动信号上升沿与毗邻的基准时钟上升沿之间的时钟偏差ΔT1;③截止信号上升沿与毗邻的基准时钟上升沿之间的时钟偏差ΔT2。设被测的时间间隔为ΔT,则有:

ΔT=NT+ΔT1-ΔT2

(1)

这种时延测量方法测量的是信号在网关节点和数据采集装置之间传输一个回路的时延差,在不考虑光纤色散和时钟偏移的情况下,单向传输的时延差应为:

(2)

N次测量的平均时延值为:

(3)

式中,T为所选择主时钟的固有时钟周期。为了得到稳定的时延测量数据,计数值在输出前需经过锁存器锁存缓冲,利用状态机不同状态的跳转把高精度计数器中的数据赋值到数据锁存寄存器中进行锁存。

2.1.4 数据传输模块

数据传输模块的作用主要是把所测时延值上传到网关节点,具体实现过程为:把寄存器中的时延值写入FIFO(先进先出)中进行缓存,当接收到测控终端的数据上传指令时,通过Niosii(软核处理器)中的UART(通用异步收发传输器)把FIFO中的时延测量值发送到网关节点,供上位机读取。

3 Modelsim仿真及误差分析

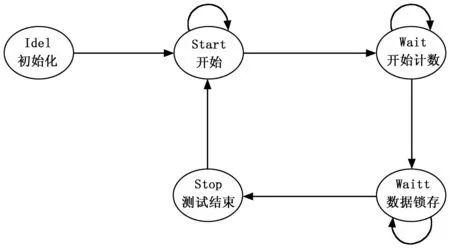

为验证基于FPGA的时延测量算法各功能模块的正确性,借助Modelsim软件对FPGA内部的状态机及各个模块进行了功能仿真验证[7]。图4所示为时延测量算法的状态机结构图,仿真的目的主要是验证时延测量算法所涉及的各个状态机能否按相应条件正常跳转,以及能否实现高精度计数及数据锁存等功能。为减小仿真时的计算运算量,缩短仿真程序执行时间,对仿真程序进行了优化,只进行最必要部分的功能仿真,仿真时所采用时钟频率f=100MHz。

图4 时延测量算法状态机跳转图

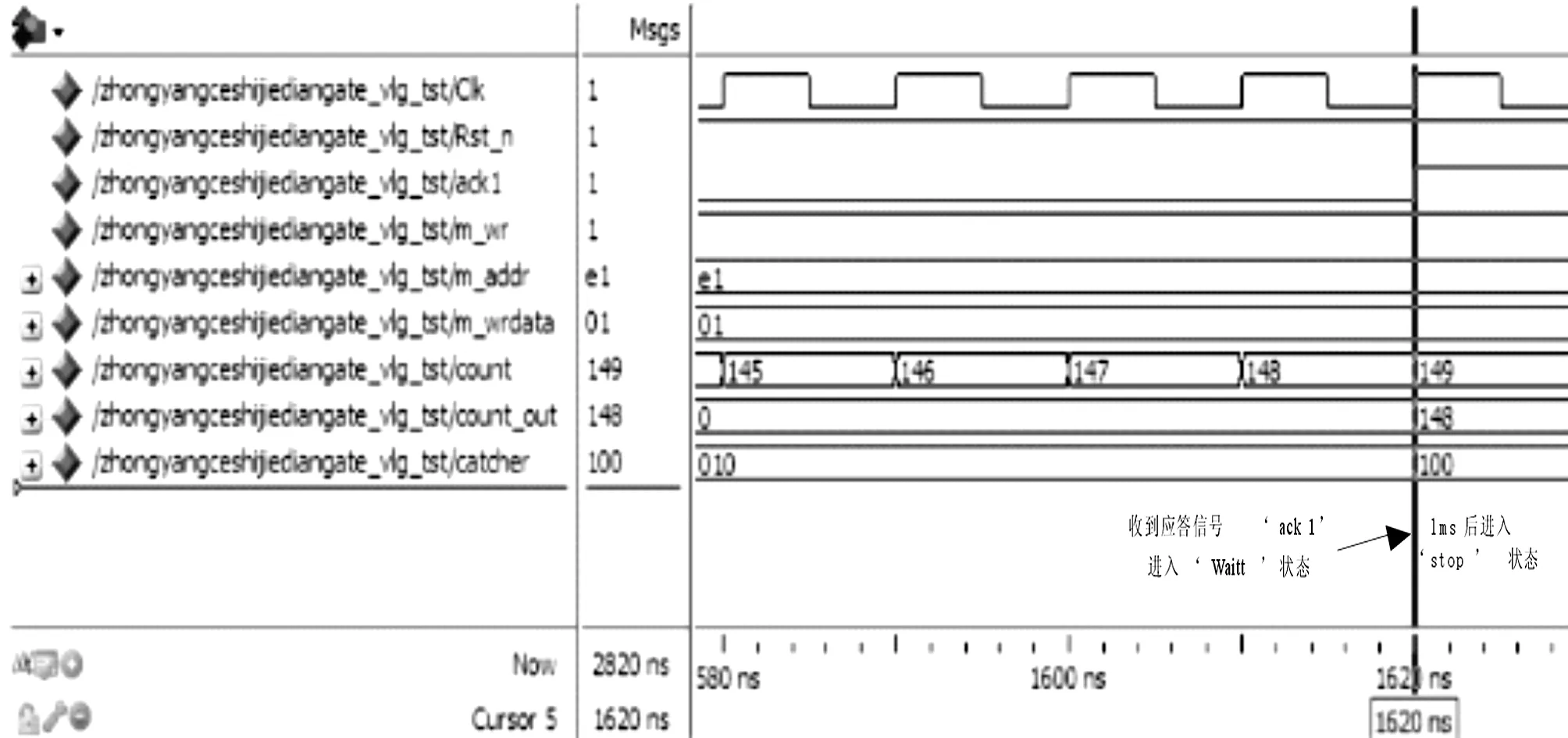

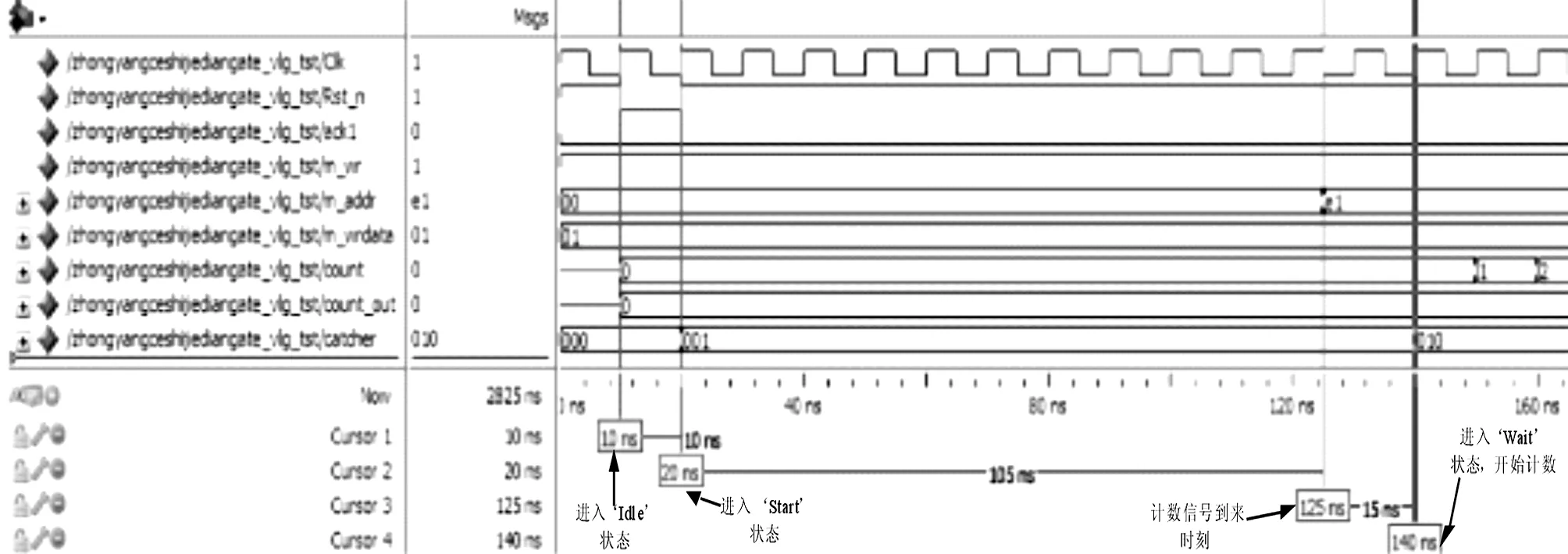

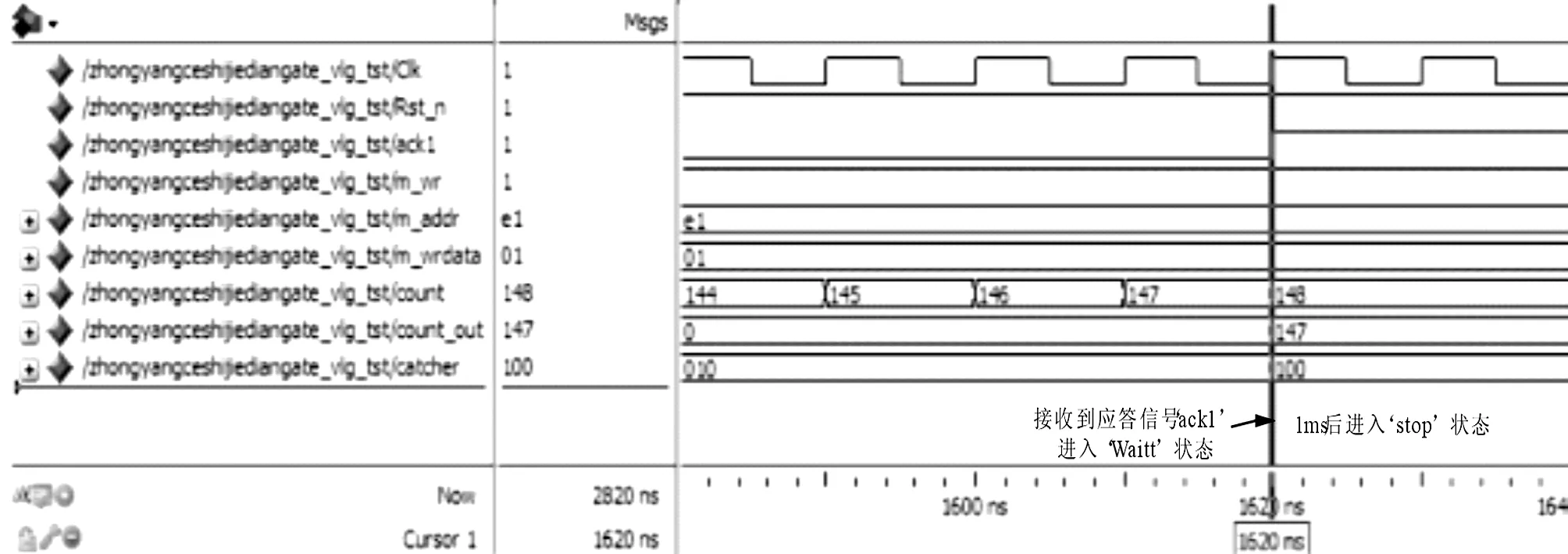

图5~6所示为Modelsim中截取的各个状态机跳转的时序图。系统上电后状态机进入初始化状态(Idle),复位(Rst_n)完毕后进入开始状态(Start),等待时延测量指令的到来。网关节点按照硬件通信协议对测试系统中的各个测试装置依次进行时延测量,测试装置收到网关节点的指令后按照通信协议对命令进行解析,只有当地址和命令分别与测试装置的节点号和时延测量功能完全匹配时,测试装置才会响应时延测量。在此,为简化仿真程序,采用地址(addr)匹配来进行时延测量功能的仿真,如图5所示,当addr为该节点地址(e1)时,地址匹配成功,在下一个时钟上升沿,系统接收到时延测量启动信号,状态机进入开始计数状态(Wait),等待时延结束信号(ack1)的到来。为模拟信号在传输链路上的时间延迟,在仿真程序中采用了1490ns的延时,即1490ns后计数模块接收到结束信号,计数器停止计数,状态机跳转到数据锁存状态(Waitt),把16位count寄存器中的数据锁存到16位count_out寄存器中等待输出。数据锁存完毕后,在下一个时钟周期,状态机进入停止状态(Stop),本次时延测试结束,延时1ms后状态机自动进入开始状态,等待下次触发信号的到来进行下一次时延测量。

图5 状态机跳转时序图

图6 结束信号对齐时钟上升沿

从以上的功能仿真结果中可以看出,本模块的各部分功能设计逻辑正确,状态机跳转正常,可以完成时延测量的功能。在图5~6中的功能仿真中,启动、停止信号的上升沿与时钟上升沿严格同步,没有相位偏移。但是在真实工作状态下,晶振受温度、老化、振动等因素的影响可能会发生频率的微变,导致状态机跳转信号可能与时钟上升沿存在相位偏差。为了更加真实地模仿实际工作情况,在Modelsim中我们对启动信号延迟5ns于时钟上升沿、停止信号正常到达和启动信号正常到达、停止信号延迟5ns于时钟上升沿这两种情况进行了仿真。

从图7~9中的功能仿真中可以看出,当启动信号、停止信号的上升沿与时钟的上升沿存在时钟相位偏差时,可能会导致计数器中的数值存在±1个计数误差,导致所测时延值存在一定误差。

图7 开始信号滞后于时钟上升沿

图8 结束信号正常到达

图9 停止信号滞后于时钟上升沿

4 试验验证及数据分析

为了验证整个时延测量电路精确度和系统稳定性,在线性网络拓扑结构上的数据采集装置和网关节点之间进行了时延测量,随机选择一条链路上的三个数据采集装置作为测试节点。时延测量示意图如图10所示,其中网关节点作为1号节点,离网关最近的测试装置作为2号节点,后面依次为3号节点和4号节点,节点之间采用光纤进行连接,四个节点等间距布设。

图10 时延测量示意图

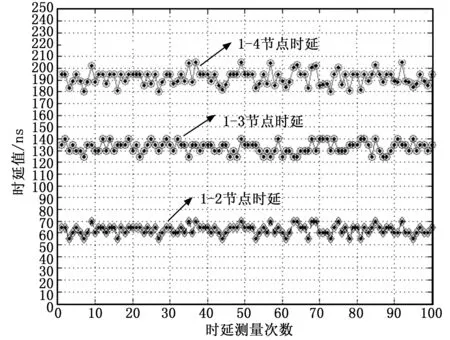

时延测量启动信号由1号节点上的FPGA提供,启动信号沿光纤传输链路到达各测试节点,节点响应完毕后经过光纤收发一体模块和光纤将停止信号送回1号节点上的FPGA中进行测量。测得时延值锁存后通过串口发送到上位机中,在上位机中借助MATLAB软件对测得的时延值进行分析[8]。在115200波特率下分别以100MHz、200MHz时钟频率测量1~2号节点100组时延值,1~3号节点100组时延值,1~4号节点100组时延值。借助MATLAB软件分别对测得的100组随机时延值数据进行分析,画出不同时钟频率下所测时延值的动态分布图,如图11~12。

由图11~12可以看出,线性拓扑结构中1~2节点时延值的总体均值为65ns、1~3节点时延值的总体均值为130ns,1~4节点时延值的总体均值为195ns,两节点间的时延测量误差集中分布在某些值附近,误差波动随着测量晶振频率的提高逐渐缩小,200MHz时误差波动范围最小误差约为5ns;时延测量值随节点之间距离的增加呈线性增长趋势,没有随节点之间的距离和测量次数的增加而呈发散趋势,证明这种时延测量方式稳定可靠,可以满足分布式测试系统时间同步的要求。

图11 100 MHz时延值分布图

图12 200 MHz时延值分布图

5 提高时延测量精度的措施

由仿真和试验实测数据看以看出,利用本测试方法实现时间同步存在一定的测量误差,为进一步提高测试精度,降低误差对时间同步带来的影响,主要从以下两个方面采取了措施以提高时间同步精度。

5.1 多次测量求平均时延值法减小时延测量误差

单次时延测量存在一定的随机误差,多次测量求平均值的方法是常用的提高测量精度的方法[9]。设测量次数为N,第i次所测时延值结果为ti,时延测量是正态分布的平稳随机过程,可用下式计算时延偏差的标准方差:

(4)

其中,平均时延值:

(5)

5.2 选用高精度晶振提高时延测量精度

在时延测量系统中,高精度的时钟频率是影响测量精度的重要因素之一。FPGA内部高精度计数器的基准信号源是由系统板载石英晶振提供的,因此,进行高精度的时延测量,选择一个频率性能稳定的晶振是至关重要的。衡量晶振性能的主要参数有标称频率、频率温度稳定度、短稳、老化率等[10]。频率温度稳定度是指晶振在正常工作的温度范围内,晶体输出频率相对于基准温度的时频率变化值,是关于温度K的一个函数,该值越小表明晶振受温度影响越小,性能越稳定。短稳即短期频率稳定度,表现为短时间内(一般为毫秒级)晶体频率值随机平均漂移情况,是关于时间t的一个函数。频率短期稳定度一般通过阿伦方差来表示,即:

(6)

6 结论

本文所提及的分布式测试系统主要由测控终端、网关节点和分布在测试区域内的数据采集装置组成,所提的时延测量技术适用于分布式测控系统中实现网关节点和数据采集装置之间的时间同步。本文从实现原理上对这种采用时延测量技术来实现时间同步的方法给予了详细的阐述,并进行了功能仿真验证以及试验验证。仿真及试验结论表明:该测量方法简单、实用,可以实现信号传输链路的高精度时延测量,是一种行之有效的时延测量方法,可以准确获得信号传输到各个测试装置的时延差,进而实现各测试装置的时间同步。该时间同步技术适用于需要时间同步精度比较高的瞬态类信号分布式测试系统,尤其适用于一些不能接受高成本时钟同步芯片或者不能接收到GPS信号的复杂测试环境。

[1] 王 爽, 胡冬旭. 基于FPGA的分布式测控装置设计与应用[J].国外电子测量技术, 2015(10):11-13.

[2] 赵德平, 韩建平. 基于TDC_GP2的高精度时间差测量的关键技术研究[J]. 材料与冶金学报, 2014,4:016.

[3] 支超有, 姜丰收. 混合总线分布式测试技术研究及应用[J]. 计算机测量与控制, 2012, 20(12): 3139-3140.

[4] 沈 艳. 分布式测试系统协作理论及其通信平台实时性研究[J].电子科技大学, 2004, 6.

[5] 逄锦昊, 苏 涛, 杨 涛,等. 基于FPGA的多路高速数据传输同步时延测量系统[J].电子器件,2015(02):447-451.

[6] 王首浩, 仲 悦, 张 巍, 等.一种用于分布式控制的光纤通信协议设计与仿真[J]. 计算机测量与控制, 2014, 9: 101.

[7] 徐盛晨. 基于FPGA的实时数据采集与传输系统的设计[D].北京:北京邮电大学, 2014.

[8] 马文起, 耿虎军, 郭肃丽,等. 一种基于FPGA和Matlab的时延测量方法[J].无线电工程,2014,44(11):38-40.

[9] 庄晓燕. 分布式测试系统时钟网络结构与同步算法研究[D]. 成都:电子科技大学,2013.

[10] 洪 锋, 张玉亮, 杨博真,等. 水下传感器网络时间同步技术综述[J].电子学报,2012,41(5): 960-965.

Research on Time Synchronization Technology in Distributed Test System

Mou Zonglei,Song Ping

(Ministerial Key Laboratory of Biomimetic Robots and System, Beijing Institute of Technology, Beijing 100081, China)

The distributed test system is a complicated measuring and controlling system based on computer controlling technology, network communicating technology and sensor technology. Different from the independent test system, in the network distributed test system, every test device need to communicate with the gateway node according to the communicating treaty to fulfill corresponding test. Different transmission distances will lead to delay difference when the gateway node has sent signals to different test devices. The test data can not reflect the true information for the reason of clock difference unless the test devices of the system own a unified time base. So all the devices in the whole test network should keep time synchronization. In the view of the requirement of time synchronization, the delay of signal transmission in the test system is studied, and also, a time delay measuring method based on FPGA is presented. The realization principle of delay measuring method from software and hardware is expounded in detail, and the function simulation and experiment verification are carried out.

distributed test system; delay difference; time synchronization; delay measurement; function simulation

2016-11-29;

2016-12-19。

牟宗磊(1985-),男,山东日照人,博士研究生,主要从事传感与机电控制方向的研究。

1671-4598(2017)05-0021-05DOI:10.16526/j.cnki.11-4762/tp

TN

A