基于MPC8270的处理器板卡设计

2017-05-24邱永成谢荣清

邱永成,谢荣清

(中海油田服务股份有限公司 物探事业部,天津 300450)

基于MPC8270的处理器板卡设计

邱永成,谢荣清

(中海油田服务股份有限公司 物探事业部,天津 300450)

随着海洋地震勘探发展,为了实现海洋地震勘探采集数据的实时传输和处理,设计了一种基于MPC8270的地震数据采集处理板卡;根据海洋地震数据采集处理的实时性和大数据量要求以及MPC8270处理器的特性,设计了基于MPC8270和FPGA的CPCI总线通信结构,能够实现地震数据的高速实时传输;详细介绍了MPC8270的关键外围电路、FPGA及CPCI总线电路的硬件设计及实现方法,并在实际应用中给出了板卡嵌入式操作系统VxWorks配置的实现方式;板卡以MPC8270作为核心处理器,以FPGA为控制核心电路,以VxWorks为实时操作系统,实现地震数据的高速处理和CPCI总线实时传输功能;经过多次实验室内部测试及海上实际生产应用,结果表明地震数据采集处理板卡能够实现地震数据的高速处理和实时传输,并且板卡性能稳定可靠;板卡的设计简单,结构通用,对数据处理、总线控制和信息交换等领域相关系统的开发具有一定的参考价值。

MPC8270;CPCI总线;FPGA

0 引言

MPC8270是Freescale公司的一款多功能通信处理器,集成了PowerPC内核和通信处理模块内核[1],有较高的集成度和较低的功耗,能够简化电路板的设计,加快处理器板卡的开发调试,并且价格相对较低。这种低成本多用途的集成处理器的应用场合是使用PCI 接口的网络基础结构、电讯和其它嵌入式应用等方面。PCI总线以其独立于处理器的独特设计和高性能、开放性等优势,已在PowerPC微处理器中广泛使用,通过PCI总线可以很方便地实现CPU与外围高速设备的互联[2],特别是与FPGA的互联,通过寄存器直接读取或者DMA等方式,能够实现大容量数据的高速处理和快速实时传输。

目前海上地震勘探随着油气勘探程度的提高,勘探目标日益复杂,勘探难度也就越来越大,常规的勘探往往难以解决出现的复杂地质问题[3],因此海上油气勘探逐渐向进一步提高时间和空间分辨率的方向发展,这就造成单检、小道距、多道采集成为地震勘探采集的发展趋势;而随着地震采集道数和采集频率的提高,地震数据量将大大增加,单缆单炮数据甚至可超过1 Gbit,并且根据地震数据的实时特性,这就需要先进、可靠的采集方式进行大数据量地震数据的实时采集和传输。因此本文设计了一种以MPC8270处理器为CPU的PCI板卡,对MPC8270的关键外围电路、FPGA及CPCI总线电路的硬件设计进行了详细说明,主要的目的就是实现地震数据的实时传输和处理。

1 板卡总体结构

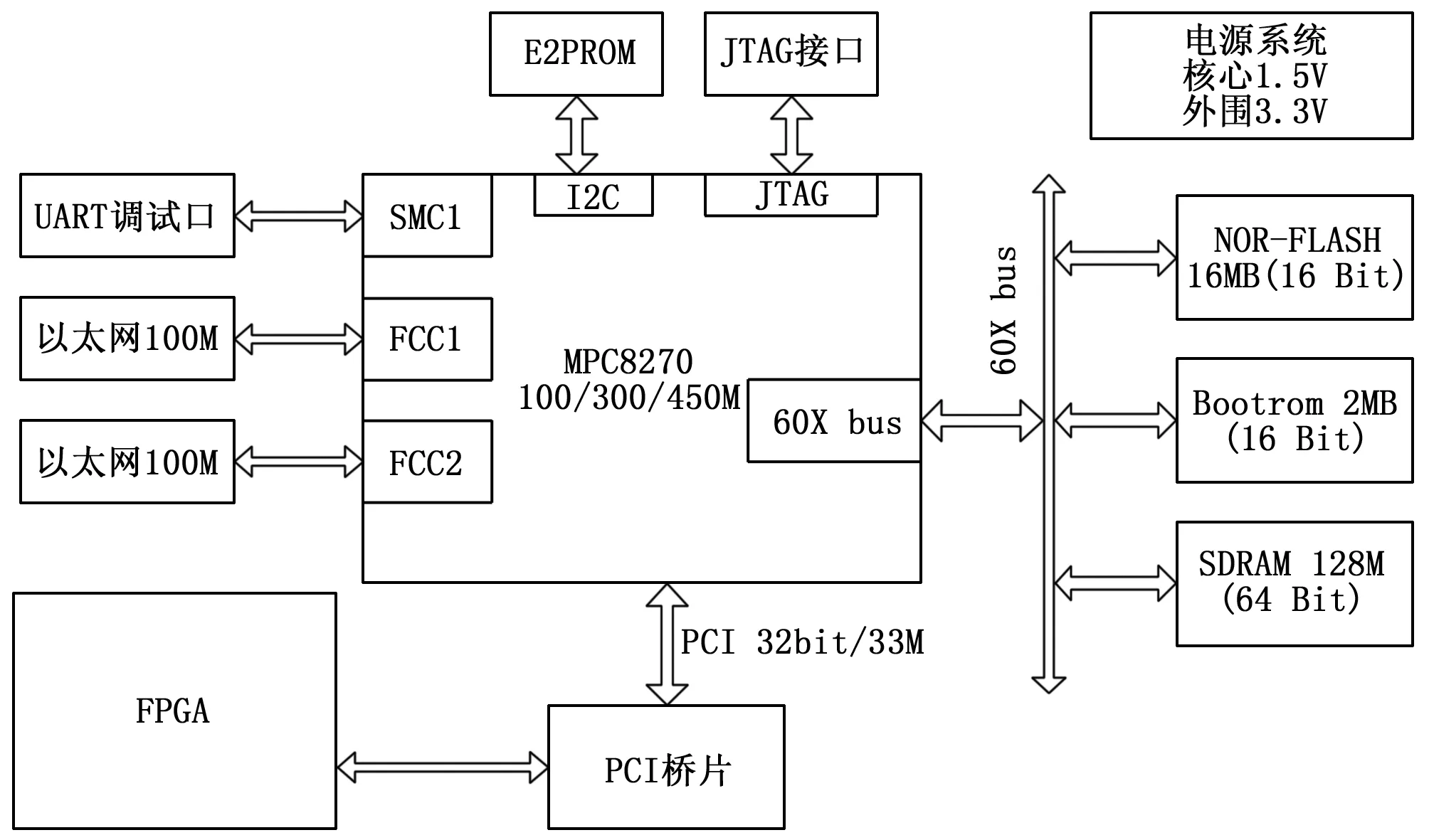

根据地震数据的采集传输特性要求,板卡需要实现大容量地震数据的实时处理和传输,并且兼顾系统的开发难度和成本因素,因此板卡以MPC8270处理器为核心处理器,采用FPGA对地震数据进行高速处理;MPC8270与FPGA之间通过CPCI总线进行通信,可以实现寄存器直接读取、DMA等多种传输方式,可以对大容量的地震数据进行高速传输。另外根据系统实时性的要求,处理器要求支持实时操作系统VxWorks,而MPC8270正好满足要求。因此地震数据处理板卡结构以MPC8270、FPGA和PCI硬件为基础,图1为板卡的总体结构框图。

图1 板卡总体结构框图

如图1所示,整个处理器系统主要包括FPGA、PCI硬件电路、MPC8270处理器及周边电路。处理器周边电路主要包含以太网口、UART串口、I2C总线接口、JTAG接口、60X总线接口、PCI总线接口、电源转换电路、时钟电路、复位电路等等,其相关电路功能如下所示。

MPC8270处理器:完成高同步性的命令实时处理以及地震数据的高速传输和网络发送;

两个100 M以太网接口:一个用来完成地震数据的上传;一个用来完成控制命令的下传;

一个UART串口:实现板卡调试及相关信息的输出;

一个I2C总线接口,用来连接E2PROM。保存配置信息;

一个JTAG接口,用来调试;

60X总线外挂2 M字节的BootROM、16 M字节的Flash和128 M字节的SDRAM;用来完成BootROM保存、应用程序存储和数据存储及转发功能;

提供一个PCI接口:用来从FPGA获取地震数据,并通过以太网接口发送给上位机;

电源转换电路,用来给板上不同器件及功能单元供电;

2 硬件设计

2.1 MPC8270及周边电路

2.1.1 MPC8270上电配置

处理器的主要功能就是执行相关指令,进行逻辑运算,数据运算处理等。MPC8270包含32bit Local Bus和64位60X Bus的双地址总线,总线时钟最大支持100 MHz,支持主从模式的32 bit33/66 MHz的PCI总线,MPC8270上电后可以通过以下一些管腿进行配置实现板卡的相关功能:

1)PCI_MODE:PCI桥的使能,在此接低,可以使MPC8270工作在PCI模式下。

2)PCI_CFG[0-3]:PCI桥的一些模式配置。

PCI_CFG0:定义PCI桥为主或从模式,在此接低,使MPC8270桥为主模式;

PCI_CFG1:片内仲裁使能,在此接低,允许片内仲裁器;

PCI_CFG2:DLL使能,在此接高,使能DLL;

PCI_CFG3:预留,接高;

3)PCI_MODCK:在PCI模式下,定义额外的时钟电路工作模式,在此接高,使PCI能工作在33 MHz模式下,接低则实现66 MHz工作模式。

4)MODCK[1-3]:与MODCK_H一起定义时钟方式,在此接为“100”。

5)PCI_MODCK_H[4-7]:在PCI模式下,代替硬件配置字中的MODCK_H,在此接为“1010”,与MODCK[1-3]一起定义CPU时钟模式为100 M总线时钟/200 M CPM时钟/400 M核时钟。

6)RSTCONF:硬件配置字选择,在本板使用跳线进行选择,当不插跳线时为正常工作状态,即MPC8270从FLASH中加载硬件配置字,当插上跳线时MPC8270上电后不从FLASH中加载硬件配置字。

2.1.2 CPU片选及中断分配

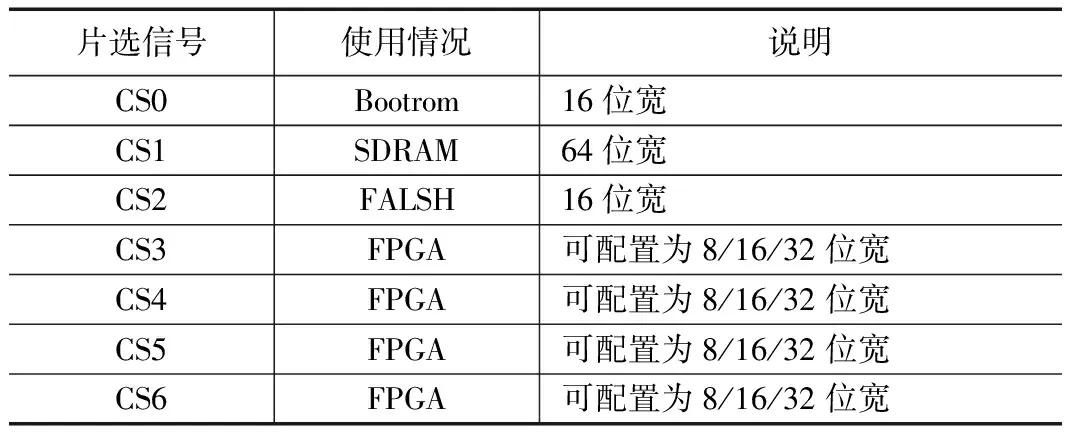

MPC8270的存储空间控制器共有12个可设地址空间,每个空间有一个单独的片选信号输出,本板的使用情况如表1。

表1 片选信号分配表

MPC8270可支持24个外部中断源:16个PORT C引脚和8个IRQ引脚,本板的使用情况见表2。

表2 中断分配表

2.1.3 LOCAL BUS总线驱动及SDRAM实现

由于LOCAL BUS总线上带有多个存储外设,因此需要进行总线驱动以提高系统的可靠性。选择2片SN74LCX16245MTDX来实现数据线驱动,2片SN74LCX16373MEAX来实现地址线驱动。

MPC8270通过60X总线外挂SDRAM芯片实现内存单元。SDRAM的总线频率为100 MHz,SDRAM的总线宽度为64-bit。

在本设计中,我们选择MICRON公司的MT48LC16M-16A2TG-75IT,每片为32 MB空间,在此使用4片来实现128 MB的内存空间,SDRAM连接到MPC8270的60X总线上。

2.1.4 Bootrom和flash实现

根据应用程序大小的相关估算,板上系统提供2 M字节的16 bit位宽的BootROM和16 M字节的16 bit位宽的FLASH。分别用来保存BootROM代码和VxWorks操作系统和应用程序代码及相关配置信息。

本板的BootROM选择AMD公司的AM29LV160DB,2 MB,16位宽。FLASH使用SPANSION公司的S29GL128M10TAIR2来实现,16 MB的存储空间,16位数据宽度,作为VxWorks的存储空间及其它存储空间。

2.1.5 以太网实现

板卡通过使用MPC8270片上集成的两个快速通信控制器(FCC),实现设计需求的两个以太网接口。一个用来上传地震数据,一个用来下传送控制命令。其中PHY芯片使用LXT972ALE,线路变压器使用H1102,连接器使用RJ-45。

MPC8270内部有I2C控制器,对外有标准I2C总线接口,本板采用同为I2C接口的E2PROM AT24C16A,可直接连接MPC8270的I2C接口。

AT24C16A不使用设备地址,在总线读写中出现在低3位设备地址时序的3个比特是页地址,该3比特与随后的8比特地址构成11位的存储地址,可完全寻址AT24C16A的2K字节存储空间。

2.1.6 UART及复位逻辑实现

MPC8270内部带有两个SMC,本系统使用其中一个SMC1进行UART调试接口的连接。外围采用SP3220EEA实现电平转换,对外提供DB9/F接口座。

根据MPC8270上电复位时序要求,采用两片ADM811T来实现其复位逻辑。外设复位逻辑使用SN74LVC125ADR。原理见图2。

图2 复位逻辑原理图

如图2所示,复位信号共分两级,第一级复位连接FLASH等其它外设,第二级复位连接MPC8270,使MPC8270退出复位状态时FALSH已经准备好,以保证MPC8270的读写时序正确。

2.1.7 电源及时钟电路

本板共需要使用6种电源:5 V、3.3 V、1.5 V、1.8 V、1.2 V、0.9 V分别给板卡上不同器件和功能单元完成供电。5 V和3.3 V电源通过CPCI接口的J1、J2连接器从机箱背板获取电源,其他电源通过二次电源转换获得工作所需要的电流。其中FPGA使用3.3 V、1.8 V、1.2 V,无上电顺序要求;MPC8270使用3.3 V、1.5 V,推荐1.5 V先上电,但在本设计中3.3 V由背板获得,1.5 V由本板生成,无法满足要求,因此对MPC8270外围电路进行一些必要保护,包括如下。

上电时使FLASH处于复位,避免对FLASH的误操作;

SDRAM的CKE接上电复位,避免SDRAM进入错误状态板上1.2 V、1.8 V、1.5 V、0.9 V需要使用二次电源进行变换得到,1.5 V需要的电流低,选用一个3 A的LDO即可,本板使用LINEAR公司的输出可调的LDO T1764EQ;1.8 V电源是给FPGA的接口使用,需要的电流较大,在此使用LINEAR公司step down controller LT1778EGN;1.2 V电源是FPGA的核心电压,考虑到FPGA对该电源功率的需求与FPGA的逻辑设计有很大关系,在此也使用LT1778EGN来实现较大功率的输出,可满足将来FPGA逻辑设计进一步复杂时所需的更大功耗。0.9 V是专门用于总线终端匹配使用的电源,采用1片PTH05060YAH为本板产生所需的Vtt,该器件可提供10 A的电流驱动能力。

本设计中MPC8270的PCI总线工作在主模式下,MPC8270的时钟都由60X总线输入的时钟产生,60X 时钟在MPC8270芯片内部经锁相环倍频后送核、CPM使用,再经过分频后供PCI接口使用。60X总线时钟由外部100 MHz晶振产生,100 MHz晶振产生时钟后通过CY2309芯片进行扇出给MPC8270和FPGA使用。

2.2 FPGA

FPGA主要完成地震数据的临时存储及高速数据的转换和处理功能,根据大容量,可靠性高的要求,我们选择Altera公司的Stratix II EP2S60F1020C5作为板上数据处理核心。通过此FPGA连接接口单元接收地震数据,并通过高速PCI接口和局部总线接口实现与MPC8270之间的数据高速传输。

Stratix II可以使用5种方法进行配置:FPP-快速被动并行、AS-主动串行、PS-被动串行、PPA-被动异步并行、JTAG方式。

在本板使用AS模式,好处是只需要外加一片串行E2PROM,外围电路和控制方法都简单,而且串行E2PROM的内容可在线编程,上电后,Stratix II会自动进行逻辑加载。串行E2PROM选用ALTERA的EPCS16SI16N,该芯片容量为16 Mbit,可存储EP2S60的压缩文件。

FPGA与MPC8270 LOCAL之间使用32位宽总线,信号具体定义如表3。

表3 FPGA与MPC8270之间的信号

在实际设计中,将MPC8270 LOCAL的接口分散接入FPGA的bank1、bank2、bank5、bank6,以利于FPGA的PCB出线。

2.3 CPCI总线接口

本设计使用PLX公司的PCI9054以实现MPC8270通过PCI总线访问FPGA的功能。PCI9054是目前应用广泛,性价比较为突出的PCI接口芯片之一,这里选择它作为8270的PCI端与FPGA局部总线的连接,实现灵活的数据传输方式。PCI9054的接口最高为32位,33 MHz,支持PCI双地址周期,地址空间高达4 GB;提供了两个独立的可编程DMA控制器,每个通道均支持块和Scatter/Gather的DM方式,DMA通道0支持请求DMA方式;PCI和Local Bus数据传送速率高达132 MB/S;本地总线速率高达50 MHz;支持复用/非复用的32 bit地址/数据;

PCI9054有三组对外接口:PCI总线、LOCAL总线、E2PROM接口。PCI9054的配置可以自动加载E2PROM也可以通过LOCAL总线进行配置,上电后PCI9054自动读取E2PROM接口,若没有E2PROM或读到E2PROM为空,则PCI9054使用默认配置值,随后可通过LOCAL总线进行配置。本板使用一片NM93CS56L来存储配置信息。

PCI9054的LOCAL总线可以工作在3种模式下:M模式、C模式、J模式,其中M模式主要应用于MPC850/860;J模式的地址线与数据线是复用的,完全由PCI总线来控制;C模式的地址线和数据线分开使用,适合应用于有本地端主设备的情形[4]。在本板的设计中使用了J模式,通过设置PCI9054的MODE0(156引脚)和MODE1(157引脚)的值来实现其工作模式的配置,将PCI9054的156脚接高电平157脚接地后,使其工作于J模式完成与FPGA之间的信号连接。PCI9054的PCI接口工作在从模式,其时钟由MPC8270提供一个33 M时钟;PCI9054的LOCAL接口时钟由FPGA提供,FPGA将外部输入的100 M时钟分频为50 M后送给PCI9054。

3 VxWorks配置

由于要处理实时信息,保证命令和地震数据的实时性要求,板卡使用实时性好的VxWorks 操作系统[5],VxWorks是美国风河公司开发的一套高可靠性、可裁剪的嵌入式实时操作系统广泛应用于工业控制、通信、航天航空等领域中。VxWorks操作系统在启动后会自动的对PCI总线进行扫描,根据PCI设备在总线上的位置自动给设备分配总线号、设备号、功能号以及地址空间的分配。例如:利用PCI9054的VendorID和DeviceID来确定该设备在总线上的位置及VxWorks操作系统对该设备内存空间和I/O空间的分配。

pciFindDevice(vendorid, deviceid, unit, &pcibus, &pciDevice, &pciFunc) 其中,VendorID和DeviceID通过硬件手册可以获取,通过这个函数就可以知道该PCI设备在PCI总线上的位置,假设为:busNo 0x0, DeviceNo 0x19, FunNo 0x0, 利用这几个参数在target shell下输入:

-> pciHeaderShow 0, 0x19, 0

就会显示出VxWorks操作系统对该PCI设备的空间分配和一些配置信息。

另外一种方法是:在系统启动后,不运行任何程序,直接在target shell下输入命令:

-> pciDeviceShow i (i = 0, 1, 2,… 其中i 表示PCI总线)

通过这个命令同样也可以获得PCI9054的总线号、设备号、功能号,然后同样用pciHeaderShow命令来获取bar0、bar2的配置信息。(注:系统中只用到这两个bar空间)

在Shell下通过命令pciHeaderShow 0x0,0x19,0x0可获得某块FCI板的配置空间信息。假设为:

Bar0: 0xb0000000

Bar2: 0xb0100000

因为,在对PCI9054的操作中要对Bar0和Bar2空间的寄存器进行读写操作,所以要把这两个地址空间在VxWorks操作系统中的地址空间里预先分配出来。这样,才可以对这两个空间内的寄存器进行读写操作。具体的添加方法是:

打开BSP目录中sysLib.c文件,在PHYS_MEM_DESC sysPhysMemDesc [] ={…}的最后面添加:

{ /* Bar0 空间 */

(void *) 0xb0000000,

(void *) 0xb0000000,

0x00010000,

VM_STATE_MASK_FOR_ALL,

VM_STATE_FOR_PCI

},

{ /* Bar2 空间 */

(void *) 0xb0100000,

(void *) 0xb0100000,

0x01000000,

VM_STATE_MASK_FOR_ALL,

VM_STATE_FOR_MEM_APPLICATION

},

添加上述内容后重新编译bootrom和VxWorks操作系统,启动后在shell下输入命令

-> d 0xb0000000

显示Bar0空间的地址的内容,如果正常显示,则表明添加正确,否则,表示错误。

4 海上试验应用

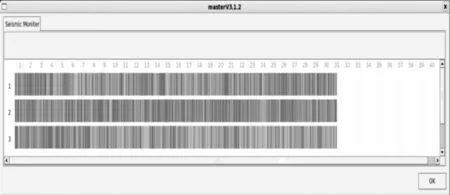

本文所设计的基于MPC8270的处理器板卡应用于地震采集仪器中,在经过了长期的实验室内部测试和调试等过程后,在物探船上进行了多次实际的海上试验和地震勘探采集作业。其中2014年在渤海海域进行了三维采集作业,图3为作业过程中上位机记录显示的拖缆地震数据阵子图。

图3 地震勘探采集作业阵子数据图

作业采样率1 ms,阵子抽取率8帧/秒,作业过程中最长测线连续工作大于500炮,总作业炮数大于10 000炮,上位机接收到的地震数据未出现错误,这充分验证和证明了本设计的处理器板卡的稳定性和可靠性。

5 结论

本文用MPC8270和FPGA实现了地震数据的高速传输和处理,设计了一种基于MPC8270的处理器板卡,详细介绍了MPC8270及外围电路、FPGA以及CPCI接口的电路设计及实现方案,并给出了嵌入式操作系统VxWorks配置的详细实现方式。该处理器板卡采用了通用的CPCI总线接口,利用PCI9054的对PCI总线的管理,能方便实现对系统中其它扩展板卡的控制、管理及信息交换;另外整个电路设计方案还可以方便的移植到其它相关数据传输系统中去,因此对数据处理、总线控制和信息交换等领域相关系统的开发具有一定的参考价值。

[1] 胡淑军.基于MPC8270的嵌入式系统研究和低功耗设计[D].北京:北京邮电大学,2008.

[2] 陶 芬,胡本志,陈 浩,等.基于PCI总线的MPC8245处理器板卡设计与实现[J].数字技术与应用,2012,12(8):113-116.

[3] 唐 进,杨 凯.浅谈中国海上地震勘探新技术应用[J].气象水文海洋仪器,2013,30(2):107-112.

[4] 王 旭.PCI9054局部总线3种工作模式的具体应用[J].电子与封装, 2005, 5(12):27-31.

[5] 李勇华.嵌入式操作系统VxWorks的实时性能测试分析[J].电子技术与软件工程,2014,11:192-192.

Design of Processor Board Based on MPC8270

Qiu Yongcheng, Xie Rongqing

(Geophysical Department,China Oilfield Services Limited,Tianjin 300450,China)

With the development of marine seismic exploration, in order to realize the real-time data transmission and processing of marine seismic exploration, a seismic data acquisition board based on MPC8270 is designed; according to the requirements of real-time and large amount of data for marine seismic data acquisition, and the characteristics of MPC8270, the design of CPCI bus communication structure based on FPGA and MPC8270 that can achieve high-speed and real-time transmission of seismic data. Introduces the hardware design and realization method of the key peripheral circuit of MPC8270、 FPGA and CPCI bus circuit, and the configurations of embedded operating system VxWorks are given. The board with MPC8270 as the core processor, using FPGA as the control core circuit, real-time operating system based on VxWorks and CPCI bus, realize high speed processing and real-time transmission of seismic data;after several laboratory internal testing and field application,results show that the seismic data acquisition board can realize high speed processing and real-time transmission of seismic data, and the board performance is stable and reliable; The design of the board is simple, the structure is general, it has a certain reference value to the development of the related system of the data processing, the bus control and the information exchange and so on.

MPC8270;CPCI bus;FPGA

2017-01-12;

2017-02-21。

国家高技术研究发展计划(863计划)(2012AA09A211)。

邱永成(1980-),男,天津滨海新区人,硕士研究生,电子工程师,主要从事地震勘探装备的研究。

谢荣清(1979-),男,天津滨海新区人,硕士研究生,系统工程师,主要从事地震勘探装备的研究。

1671-4598(2017)05-0232-04

10.16526/j.cnki.11-4762/tp.2017.05.064

TP368.1

A