高可靠性远程数据传输系统设计*

2017-04-25李治华赵冬青甄国涌刘东海

李治华,赵冬青,甄国涌,刘东海

(中北大学仪器科学与动态测试教育部重点实验室,电子测试技术国家重点实验室,太原 030051)

高可靠性远程数据传输系统设计*

李治华,赵冬青*,甄国涌,刘东海

(中北大学仪器科学与动态测试教育部重点实验室,电子测试技术国家重点实验室,太原 030051)

针对数据在远距离高速传输系统中存在的可靠性低的问题,提出了一种基于LVDS长线传输和8b/10b编码的解决方案。该设计以LVDS为数据传输接口,在硬件电路上加入均衡设计,补偿长线传输的损耗;在逻辑设计上加入8b/10编码,实现传输中的直流平衡,提高数据传输的可靠性。经验证,该系统工作稳定,串行数据以400 Mbit/s的速率,可实现在百米双绞电缆传输线或2 km光纤传输线上的零误码传输。

高速传输;LVDS;可靠;低误码率;8b/10b编码

某飞行器在研制过程中,需要使用数据采集系统采集各种模拟信号,并将信息回传给地面进行数据处理,但由于飞行器所处环境特殊,无法近距离测试,因此需要将数据通过长线高速实时的回传给地面数据处理系统,以便实时了解飞行器设备的工作状态,但飞行器的使用的弹上电缆网或光纤所处环境恶劣,周围电磁干扰大。普通并行的总线在长距离传输的条件下,抗干扰能力差,无法应用于系统中。

基于串化器/解串器的LVDS是一种低功耗、低摆幅、低误码率的低压差分信号,它的理论传输速度可达1.923 Gbit/s,是解决数据高速长距离传输,保证数据可靠性的简单有效的方案[1]。但该解决方案,在极其恶劣的环境下,数据传输的可靠性会降低,单纯依靠LVDS技术本身的抗干扰性已无法满足数据的高速可靠传输,为进一步优化设计,降低误码率,增加了8b/10b编码,保证传输中的直流平衡,从而提高传输的可靠性。

1 高速数据传输系统电路结构

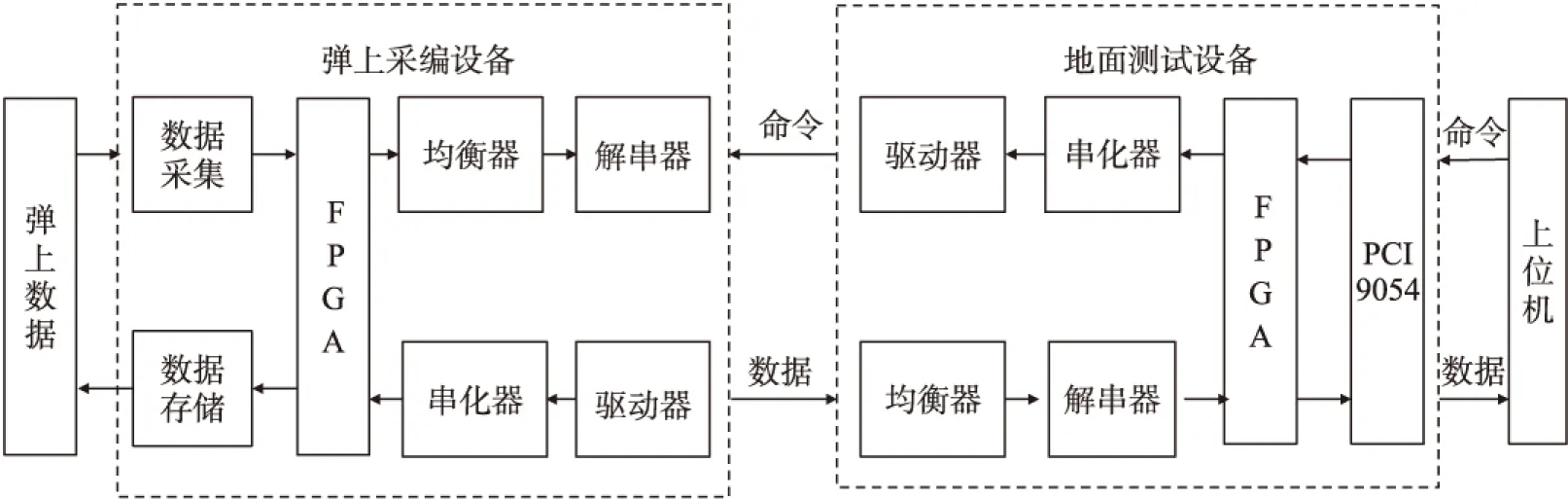

系统电路结构如图1所示,由弹上采编设备,地面测试存储设备及计算机3部分组成。弹上采编设备采集并存储,地面设备接受计算机下发指令并转发给弹上采集设备和接受弹上回传数据。

系统采用LVDS接口实现高速数据传输。在发送端,FPGA逻辑控制模块通过CPCI接口模块接受上位机下发的10bit命令,通过SN65LV1023串化器进行并串转化后,再经驱动器LMH0074增强电压摆幅后下发给转发器;在接收端,LVDS接受模块通过SN65LV1224解串器接收转发器上传的数据并进行串/并转化后经均衡器LMH0074对信号进行恢复后,再通过CPCI总线上传至上位机进行实时信息处理。

图1 高速数据传输系统电路结构

2 硬件可靠性设计

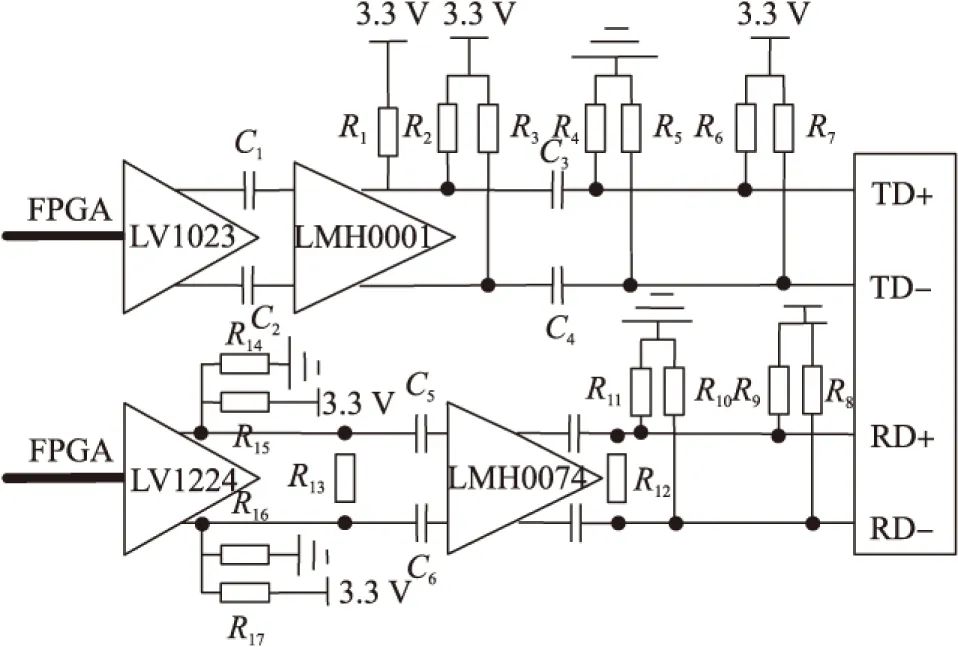

为了尽可能的提高数据传输的可靠性,减少由电缆或PCB损耗引起的高频信号边沿变化速率降低,引入码间串扰,导致高频在长距离传输时的信号衰减。为了解决信号衰减和损耗引起的误码率,在本设计中采用了信号调理和预(去)加重法和均衡(EQ)技术芯片对高频信号进行补偿,提高了传输性能。该设计采用美国半导体公司的LMH0074和LMH0001,是一对数据传输均衡器和驱动器,可以完成高速长线数据传输信号的调理作用,降低信号的衰减和损耗,提高数据传输的可靠性[2-3]。

图2 LVDS接口收发电路

2.1 控制命令链路硬件可靠性设计

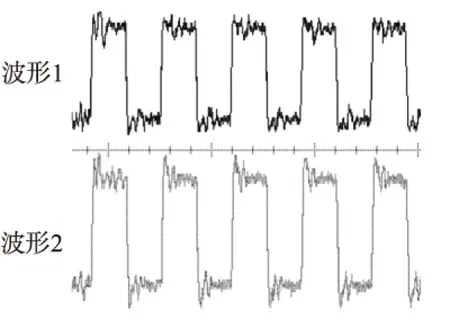

电缆驱动器LMH0001SQ是PECL电平,光收发一体模块则是LVPECL电平,这二种电平在相互连接时,需要考虑三者之间的电平的摆幅及大小的问题,因此要求上级输出的电平落入后一级输入电平有效范围内。在设计中我们选择交流耦合,有效地避免了前一级和后一级的电位的联系,同时不会破坏前级的内部偏差。图3是LMH0001SQ接收端和输出端波形图。

图3 LMH0001SQ接收端(波形1)和输出端(波形2)

在本设计中选用收发一体的光模块OCM3823,最高传输速率为1.25 Gbit/s。在命令链路的发送端,串化器SN65LV1023A将10bit并行的命令数据串化成串行数据,此时输出的低压差分信号为100 mV左右,传输距离约10 m,不能满足长距离传输的需要。LMH0001芯片传输速率可达540 Mbit/s,100 mV的差分输入门槛电压;当REF外接电阻的阻值为750 Ω时,差分输出电压约为800 mV,加外部电阻的偏置,输出电压约为1.5 V~2.3 V之间,这样就可以驱动百米双绞电缆传输线或2 km光纤,提高了命令数据在距离上传输的可靠性。

2.2 数据回传链路硬件可靠性设计

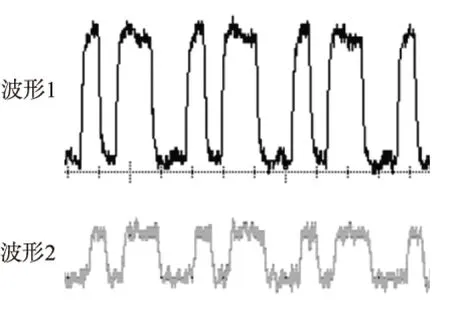

LVDS传输信号经过百米双绞电缆传输线或2 km光纤传输后,会产生损耗,损耗与信号频率的平方根成正比[4-5]。为了使接收的正确可靠的接受信号,补偿信号损耗。均衡芯片LMH0074SQ是针对125 Mbit/s到540 Mbit/s的传输速率,能够自适应补偿400 m belden 1694A或第5类非屏蔽双绞线传输的损耗,该均衡器抖动性极低,功耗仅有200 mW。

图4 LMH0074SQ接收端(波形1)和输出端(波形2)

在本设计中,在数据链路的接收端,在差分信号之间接入一个100 Ω的电阻,匹配传输线上的阻抗;在LMH0074自动均衡控制模块即AEC+和AEC-之间跨接一个1 μF的电容,用于控制均衡环路的增益和带宽;为了防止信号媒介发生发射,在LVDS信号的输出端匹配一个100 Ω,精度为1%的电阻,且在PCB布线时尽量靠近解串器。

3 软件可靠性设计

3.1 控制命令链路软件可靠性设计

如果指令识别错误,采集存储设备将不能进入正确的工作模式,最终可能导致不能采集到数据,因此在指令识别上应充分考虑到冗余及校验设计,以确保命令指令能准确无误地下发。

LVDS有效的指令数据传输是10位,但在实际传输中却是12位,增加了起始位“1”和终止位“0”,他们的作用是作为嵌套时钟的起始位和终止位。解串器从嵌套的时钟的数据中重建并行时钟,该时钟用来选通输出锁存器,并将串行数据转化成10位并行的数据存入输出的锁存器[6-7]。当收到的数据是连续几个“0”“1”变化的数据时,解串器则会将数据误认为是嵌套时钟的起始位和终止位并锁存,数据传输出错。

针对上述问题,提出了在发送有效指令的同时插入无效指令,就可以从根本上解决了连续多次重复发“0”“1”变化的数据引起的指令数据解码错误问题。由于LVDS同步码格式能够快速使解串器锁定时钟,因此在设计上采用同步码作为插入数据,因此有效指令和同步码以1∶7的比例下发命令。这样不仅能保证不会出现将数据误认为是嵌套时钟的起始位或终止位即RMT模式,也能最大限度保证命令下发不失锁。经测试该方法正确可靠,指令能够正确无误地下发。

3.2 数据回传链路软件可靠性设计

当数据流中有多个连续的“1”或“0”时,信号的转换可能因为电压位阶的变换而造成信息错误,而直流平衡可以有效地克服此类问题。8b/10b编码的特性之一是保证数据流中的直流平衡,远程数据回传时,采用8b/10b编码的方式,可以有效平衡数据流中“1”“0”的个数比例[8]。连续的“1”或“0”的个数不会超过5个,即连续的5个“1”或“0”后,必会插入一个“0”或“1”,这样就保证了直流平衡。一个8 bit的数据,经8b/10b编码后,可能出现的只有3种情况:

(1)6个逻辑“1”,4个逻辑“0”;

(2)6个逻辑“0”,4个逻辑“1”;

(3)5个逻辑“0”,5个逻辑“1”。

这3种情况你对应的8b/10b编码的极性误差为+2,-2,和0。

3.2 LVDS发送端8b/10b编码

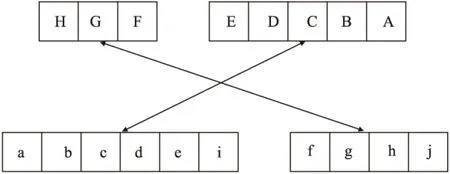

8b/10b编码中有268个有效的编码列表,其中256个是数据编码列表,12个控制字编码。其中12个控制字用于建立位同步,链路状态,数据帧标志的开始和结束。8b/10b编码时字节ABCDEFGH被分为ABCDE和FGH两部分,其中E和H为最高位,编码后对应生成abcdei和fghj,其中i和j是做高位。数据编码在编码过程中分为5b/6b和3b/4b相互独立的两部分。如图5显示了8b/10b的关系变换。

图5 8b/10b变换关系

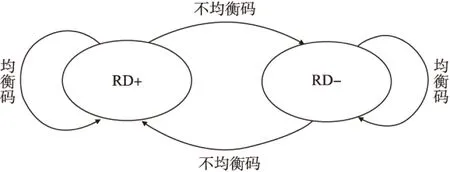

8b/10b编码具有直流平衡的特性,主要是引入了Run Disparity的概念来平衡数据流中的“1”和“0”的个数即Run Disparity实际上是指数据流中“1”和“0”的个数之差[9]。如果Run Disparity为0,则Run Disparity为中性,如果数据模块abcdei和fghj都为中性,那么整个数据模块都为中性,就可以得到真正完美的直流平衡,在LVDS数据回传链路就不会出现因为多个连续的“1”“0”电位转换而造成的信息错误,这是最完美情况,但LVDS总线在实际工程应用中上是不可能实现真正的直流平衡。因此8b/10b的编码原理就是通过检测前一个字符的不均衡型来决定后一个字符的选择。如果前一个字符是正不均衡型,则后一个字符就应该选择一个负不均衡型;同理,反之。因此这种不均衡机制使得整个高速传输系统中的数据流尽可能的保持了“1”和“0”的平衡。

图6 RD状态转换图

根据编码规则,链路系统在上电或初始化之后RD为负。在编码过程中,5b/6b编码在前,3b/4b编码在后,当前用于5b/6b编码的RD是前一个字节编码产生的产生RD,用于3b/4b编码的RD来源于前一个相邻的5b/6b产生的RD。RD的运算规则如图6所示。

(1)如果编码后的任意子模块的RD大于零,则新生成的RD为正;同时若6比特模块abcdei为“111000”或者4比特模块fghj为“1100”时,生成新的RD亦为正;

(2)如果编码后的任意子模块的RD小于零,则新生成的RD为负;同时若6比特模块abcdei为“000111”或者4比特模块fghj为“0011”时,生成新的RD亦为负;

(3)任意RD为零的子模块所生成的子模块由前面紧接着的模块RD决定。

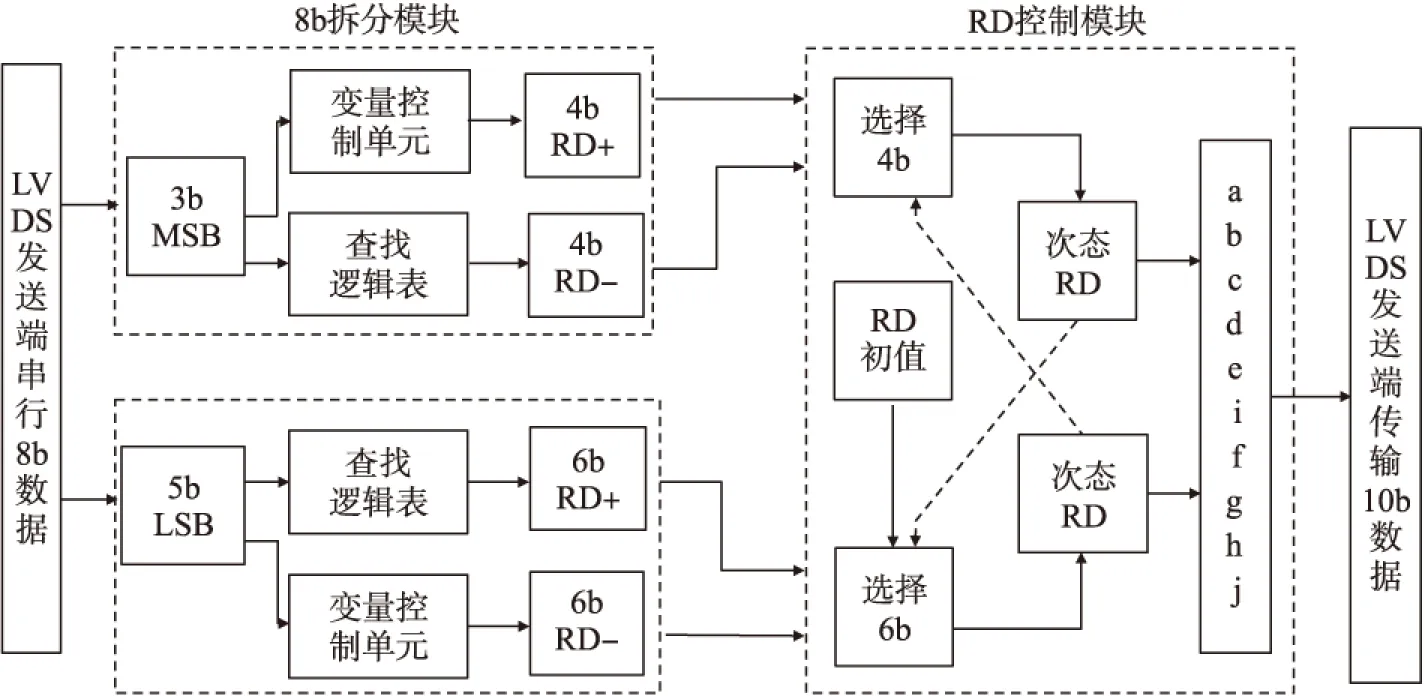

编码过程实现流程图如图7所示,LVDS接口在发送端,把8b的数据分为高3b和低5b,然后进行5b/6b转换和3b/4b转化。在5b/6b编码模块和3b/4b编码模块,由变量控制单元和查找表逻辑实现输入源码到码组的映射,大部分码源对应两种极性码组。在RD控制模块中,RD的初始值为RD-(上电或者复位),或者根据上一次RD的极性来判断6b对应的码组,以及6b次态的极性;然后再根据5b/6b编码的极性来决定4b的对应的码组,以及4b次态的极性,最后的RD的极性作为下次10b编码的初始值,依次循环判断,最后把4b和6b进行拼接后输出十位的LVDS数据流。

图7 8b/10b实现流程图

3.2.2 LVDS接收端8b/10b解码

LVDS接收端解码是发送端的逆过程,采用多对一的映射关系,分别通过对6b/5b和4b/3b解码实现[6]。该部分需要外部基准时钟来恢复时钟信号,在对远程数据进行解码时为保证解码的正确可靠性,外部提供了严格基准时钟源频率,并对时钟进行抖动控制。在解码后对8b进行校验,判断是否产生误码,如果校验正确,则输出有效数据。

4 可靠性结果验证

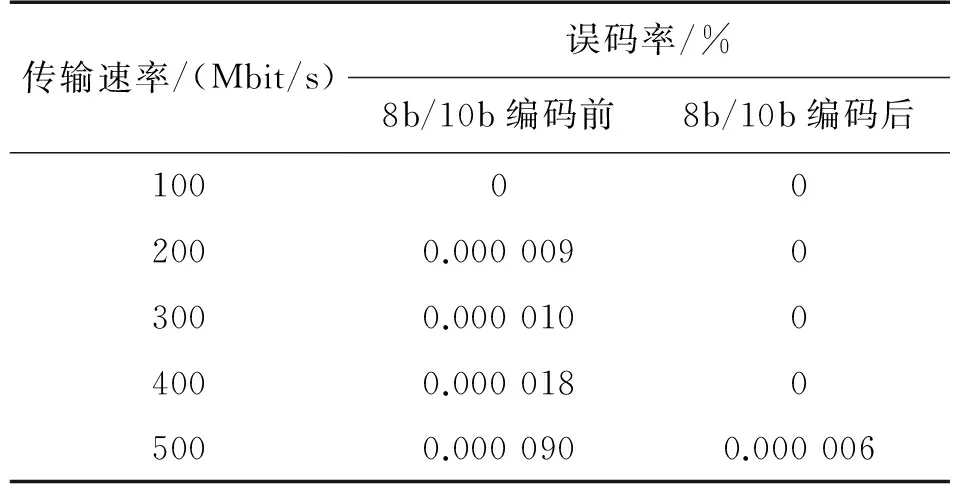

采用7段15 m屏蔽双绞线,通过J14H系列的连接器串接成105 m的电缆网,通过LVDS接口连接地面综合测试台和弹上采编存储设备。通过程序控制数据的传输速率分别为100 Mbit/s,200 Mbit/s,300 Mbit/s,400 Mbit/s,500 Mbit/s,分别对加8b/10b编码前后进行速率及误码率测试,测试结果如表1所示。

从测试结果可以分析得出,当传输速率低于100 Mbit/s时,硬件电路能保证传输的可靠性,当传输速率大于100 Mbit/s时,误码率随着速率的增大而增加。在逻辑设计上加入8b/10b编码后,能有保证400 Mbit/s,远程数据传输的可靠性。

表1

5 结束语

针对高速数据在传输过程可靠性低的问题,从硬件电路上,对LVDS信号做预处理和信号补偿,同时在逻辑设计上,采用8b/10b编码,优化了数据传输的可靠性。通过LVDS接口,在105 m弹上电缆网或者2 km光纤上,以400 Mbit/s的速度传输全“0”,全“1”,以及递增数,递减数等数据,可实现零误码传输。

[1] 马将,任勇锋,李圣昆,等. LVDS远程传输中继电路的设计应用[J]. 通信技术,2010,43(1):26-28,31.

[2] 张天文,刘文怡. 基于LVDS和PCI接口的高速图像传输系统设计[J]. 电子技术应用,2014,40(7):51-53,60.

[3] 任勇峰,彭巧君,刘占峰,等. 基于FPGA的CPCI高速读数接口设计[J]. 电子器件,2015,38(1):148-151.

[4] 李辉景,王淑琴,任勇峰,等. 基于CRC校验的高速长线LVDS传输设计[J]. 电子器件,2015,38(6):1346-1351.

[5] 来卫国. 10位BLVDS串化器DS92LV1023和解串器DS92LV1224的原理及应用[J]. 国外电子元器件,2002(8):45-47.

[6] 方平,丁凡,李其朋,等. 基于PCI总线的高速图像数据通道的研究[J]. 传感技术学报,2006,19(3):690-693.

[7] 许军,许西荣. PCI-Express中8b/10b编码解码器的设计与实现[J]. 微电子学与计算机,2006(3):37-39.

[8] 孙科达,石旭刚,史故臣,等. 一种新的8B/10B编解码方案设计与实现[J]. 光通信技术,2009,33(7):27-30.

[9] 武小强,田小平. 一种基于FPGA的8B/10B编解码电路的设计与实现[J]. 西安邮电学院学报,2010,15(5):27-29,52.

Design of High Reliability Remote Data Transmission System*

LIZhihua,ZHAODongqing*,ZHENGuoyong,LIUDonghai

(Key Laboratory of Instrumentation Science and Dynamic Measurement,Ministry of Education,Science and Technology on Electronic Test and Measurement Laboratory,North University of China,Taiyuan 030051,Chain)

Focused on the low reliable problem of data existing in high-speed and long-distance transmission system,a method based on long transmission of LVDS and 8b/10b encoding is proposed. LVDS is designed as high speed data transmission interface,the equalization circuit is adopted to compensate loss of remote transmission;8b/10b coding is realized on logic design which achieves the equilibrium of DC transmission and stability improvement in data transmission. The experiment proves that the system works stable,and realizes the rate of 400 Mbit/s of serial data transmission via 100 m shielded twisted-pair or 2 km optical fiber transmission line.

high-speed transmission;LVDS reliability;low error rate;8b/10b encoding

项目来源:国家自然科学基金项目(51275492)

2016-05-07 修改日期:2016-06-08

C:6210

10.3969/j.issn.1005-9490.2017.02.045

TP274

A

1005-9490(2017)02-0490-05