基于FPGA的数字系统设计方法

2017-03-17王玉喜

王玉喜

哈尔滨智路科技开发有限公司

基于FPGA的数字系统设计方法

王玉喜

哈尔滨智路科技开发有限公司

FPGA(FiledProgrammableGateArray)是20世纪80年代中期出现的一种新概念—用户现场可编程门阵列集成电路。PGA具有更多的门电路,体积小,成本低,并且方便随时修改设计直至满足实验要求等优点,目前FPGA也被广泛应用于通信、自动控制、信息处理等诸多领域,因此进一步加强对其的研究非常有必要。基于此本文分析了FPGA的数字系统设计方法。

FPGA;数字系统;设计方法

1、现代数字系统的设计方法

随着可编程器件的出现和计算机技术的发展,使EDA技术得到了广泛应用,设计方法也因此发生了根本性的变化。由传统的“自底向上”的设计方法转变为一种新的“自顶向下”的设计方法,其设计流程如下:第一步,进行行为设计,确定电子系统或ASIC芯片的功能、性能及允许的芯片面积和成本等。第二步,进行结构设计,根据电子系统或芯片的特点,将其分解为接口清晰、相互关系明确、尽可能简单的子系统,得到一个总体结构。第三步,把结构转化为逻辑图,即进行逻辑设计。在这一步中,希望尽可能采用规则的逻辑结构或采用已经经过验证的逻辑单元或模块。第四步,进行电路设计,将逻辑图转化为电路图。最后一步是进行ASIC的版图设计,即将电路转换成版图,或者用可编程ASIC实现。

2、FPGA的特点及设计软件

FPGA通称为可编程逻辑器件,它们都是在PLA,PAL 和GAL等逻辑器件的基础上发展起来的,主要有Altera公司和Xilinx公司生产的系列产品。许多生产可编程器件的公司为了推广它们产品都有自已的开发软件,其中应用较广的有Altera 公司的MAX+pluaII 软件,它有以下主要优点: (1)开放的接口;(2)与结构无关的设计开发环境,具有强大的逻辑综合与优化功能;(3)支持各种HDL输入选项,支持VHDL硬件描述语言;(4)全集成化的输入开发环境;(5)丰富的设计库资源;(6)有丰富的在线帮助功能。因此特别适合初学者使用,可作为数字电路系统的设计和开发软件。在指导学生进行课程设计时,应先学习MAX+pluaII软件和VHDL语言的编程方法,掌握CPLD/FPGA实验开发系统的使用。

3、基于FPGA的数字系统设计方法

FPGA(Field-ProgrammableGateArray),即现场可编程门阵列,它是随着人们对技术的要求提高而发展的产物。这里使用FPGA来实现针对脉冲边沿触发型的单光子探测器符合计数器的设计。

针对脉冲边沿触发型的单光子探测器进行符合计数器的设计,为保证符合计数有意义,必须保证探测器是同时被触发的,即探测器对同一路触发脉冲边沿的响应保持较高的一致性。探测器输出的脉冲经过电路处理,为固定脉宽的脉冲。

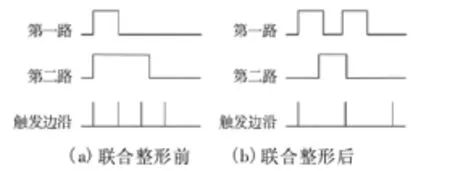

采用边沿检测法对信号进行采样,这也是FPGA最常用的检测方式。由于输入的脉冲信号对FPGA采样时钟来说是异步信号,并且两路信号从探测器输出到输入到FPGA内这期间引入的路径延时不一定具有严格的一致性,因此必须对输入的两路脉冲进行联合整形处理,即将它们跨越采样时钟边沿两侧但实际上属于同时到达的信号整形为同时到达信号,如图1:

图1

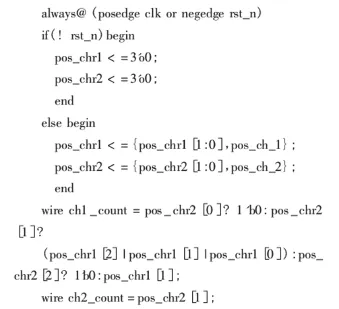

通过VerilogHDL语言进行功能程序编写,对两路信号进行联合整形的FPGA代码如下:

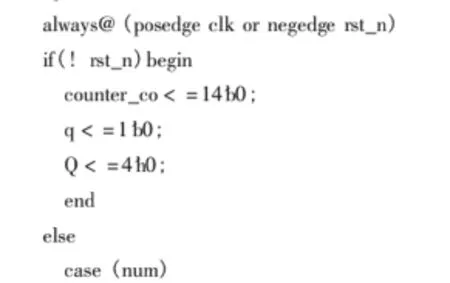

对两路信号完成整形后再对它们进行符合计数测量就不会再出现差错。由于只有触发时刻脉冲边沿触发型的单光子探测器才可能有信号的输出,因此对输出信号进行延时符合时要以触发时钟的周期为单位。在FPGA中对固定延时的控制可以通过计数器的方式实现,根据采样时钟和探测器触发时钟的周期关系,用延迟较小的那路信号启动计数器,在计数器达到指定计数时判断另外一路是否有信号到达。对采样时钟频率50M,探测器触发脉冲为5M时候的VerilogHDL代码如下:

cnt==20'hfffff为计数数据传出和清零重新计数的时刻,上述代码中考虑了该时钟周期内可能出现符合计数可能的情况。

通过QuartusⅡ调用ModelSim-Altera进行仿真,在0延迟下计算2000个符合脉冲(其中1000个上升沿错位),以及二路信号延迟一个触发时钟周期(T=200ns)计算1000个符合脉冲的仿真。

按键key用来控制延时的设置,延时状态用led来指示,001表示0延迟,010表示二路信号延迟一个触发时钟周期,led的状态控制和实现延时符合计数的状态机是相对应的。

4、FPGA发展

4.1 与信号处理器进行结合

在实际开发过程中,有不少对数字信号进行处理的方法。例如,使用DSP或者各种微型处理器等。而现在,FPGA同样可以被作为运算核心进行数字信号处理的系统的开发。特别是FPGA具有运算速度快这一优势,使FPGA能够适用于对处理速度要求越来越高的信号处理系统。

4.2 IP核库的使用

Altera与Xilinx等公司均为自己的FPGA产品开发了相应的IP核库,IP核大体可分为两类:一种是开发厂商将硬件及其配套接口作为IP硬核嵌入到FPGA当中。另一种是通过Verilog/VHDL等语言编写的具有各种功能的IP软核,开发者可以在程序中直接调用这些IP模块,并对模块的部分参数进行设置,以完成一些重复且复杂的功能,大大减少了开发者的工作量以及大幅降低了系统开发设计难度。

4.3 SOPC技术的发展

SOPC技术是一种基于FPGA的SOC解决方案,实现SOPC的方法主要有以下三种:一是将IP硬核嵌入FPGA的SOPC系统;二是将IP软核嵌入FPGA的SOPC系统;三是基于HardCopy技术的SOPC系统。

总之,FPGA具有很多优势,因此也是得多了进一步应用。本文分析了FPGA的数字系统设计,以期提供一些借鉴。

[1]叶忠彬.基于FPGA的数字频率合成系统的设计与实现[D].电子科技大学,2011.

[2]梁彬.基于FPGA的PCM数字解码系统的设计[D].电子科技大学,2003.

[3]王永维.一种基于FPGA的数字秒表设计方法[J].电子元器件应用,2012,01:10-13.