0.18 μm CMOS器件SEL仿真和设计

2017-02-27李燕妃吴建伟谢儒彬洪根深

李燕妃,吴建伟,谢儒彬,洪根深

(中国电子科技集团公司第58研究所,江苏无锡214072)

0.18 μm CMOS器件SEL仿真和设计

李燕妃,吴建伟,谢儒彬,洪根深

(中国电子科技集团公司第58研究所,江苏无锡214072)

宇宙空间存在大量高能粒子,这些粒子会导致空间系统中的CMOS集成电路发生单粒子闩锁。基于0.18 μm CMOS工艺,利用TCAD器件模拟仿真软件,开展CMOS反相器的单粒子闩锁效应研究。结合单粒子闩锁效应的触发机制,分析粒子入射位置、工作电压、工作温度、有源区距阱接触距离、NMOS和PMOS间距等因素对SEL敏感性的影响,并通过工艺加固得出最优的设计结构。重离子试验表明,采用3.2 μm外延工艺,可提高SRAM电路抗SEL能力,当L1、L2分别为0.86 μm和0.28 μm时,其单粒子闩锁阈值高达99.75 MeV·cm2/mg。

单粒子闩锁;TCAD;加固;重离子试验;外延工艺

1 引言

在CMOS集成电路中,相邻的N型区和P型区之间存在两个寄生双极晶体管构成的PNPN可控硅结构(SCR,Silicon controlled rectifier),在空间辐射环境下,该结构被触发导通,在电源与地之间形成低阻抗大电流通路,导致电路无法正常工作甚至烧毁。这种现象称为单粒子闩锁(SEL,Single Event Latch-up)[1~3]。重离子导致的单粒子闩锁现象最早在1979年被发现[4],随后的研究表明,空间环境中的质子和中子也会导致单粒子闩锁[5~9]。近年来越来越多的CMOS电路应用于航空航天领域。随着工艺尺寸的缩小,单粒子闩锁效应带来的安全隐患随之显著增加,因此要使芯片在恶劣的辐照环境中正常工作,必须对集成电路进行抗SEL加固。

本文基于半导体器件仿真工具(TCAD),研究抗辐射0.18 μm体硅CMOS器件的单粒子闩锁效应,在保证芯片面积小的情况下,采用工艺加固方案提高电路的抗单粒子闩锁能力,最后通过重离子试验,验证不同外延层厚度条件下电路的单粒子闩锁能力。

2 单粒子闩锁原理

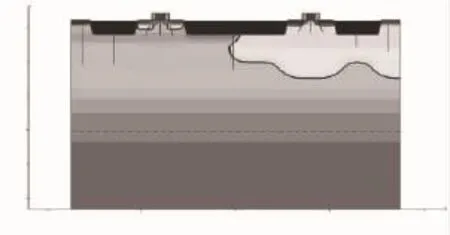

CMOS集成工艺中存在着寄生元器件,主要包括横向NPN双极晶体管T1、纵向PNP双极晶体管T2和电阻R1~R4。图1是体硅CMOS器件的寄生SCR结构及其等效电路,NMOS的源极和体接触接地,PMOS的源极和体接触电位是Vdd。单粒子闩锁触发过程如下:在CMOS器件中,高能粒子沿着其入射轨迹电离出大量的电子-空穴对,在电场和浓度梯度的作用下,过剩电子会向PMOS的源极移动,过剩的空穴会向NMOS的源极移动,载流子的定向移动形成了电流,电流流过阱或衬底中的电阻,在其中一个寄生双极晶体管(T1)的发射结产生压降,当电压降足够大时,使得T1的发射结正向导通。T1的集电极电流流过另外一个寄生晶体管(T2)的基极,该电流足够大时,产生的电压降使得T2正偏导通,T2的集电极电流进一步触发T1,使得T1的集电极电流增加。由于SCR器件的正反馈特性,流过的电流不断增加,最终导致整块芯片发生失效。

图1 CMOS器件剖面结构及等效寄生电路

3 单粒子闩锁仿真

本文采用Synopsys公司的Sentarus TCAD工艺和器件仿真模拟软件,开展CMOS器件单粒子闩锁响应特性的研究。基于抗辐射0.18 μm CMOS工艺,模拟二维CMOS器件结构,见图2。CMOS电路采用高掺杂的P+衬底和低掺杂的P-外延层,高掺杂衬底减小了衬底电阻,提高了CMOS电路的抗单粒子闩锁能力。

图2 CMOS器件结构示意图

在本文的研究中,定义入射粒子为重离子,入射粒子的能量用线性能量传输(LET,Linear Energy Transfer)表示。采用的物理模型包括载流子迁移率模型、载流子复合模型、载流子产生模型、有效本征载流子浓度模型、载流子浓度对寿命影响的SRH复合、俄歇复合、载流子之间散射、迁移率随掺杂浓度的变化以及重离子等模型。其中,重离子产生的电子-空穴对的浓度沿轨迹方向的空间分布采用高斯分布,特征半径0.1 μm,电子-空穴对的浓度随时间的分布也采用高斯分布进行建模。

3.1 SEL的敏感区域

进行SEL仿真时,单粒子轰击点的轨迹选取非常重要,不同的轰击轨迹所产生的收集电流是不同的。现在的主流仿真轨迹主要是垂直器件表面的入射方向,通过对比不同入射粒子轨迹下器件收集电流随入射时间的变化来确定CMOS器件的敏感区域。按图1的连接方式,将NMOS的源极和体接触接地,PMOS的源极和体接触连接Vdd,NMOS和PMOS的漏极相连浮空,NMOS和PMOS的栅极连接输入电压Vin。

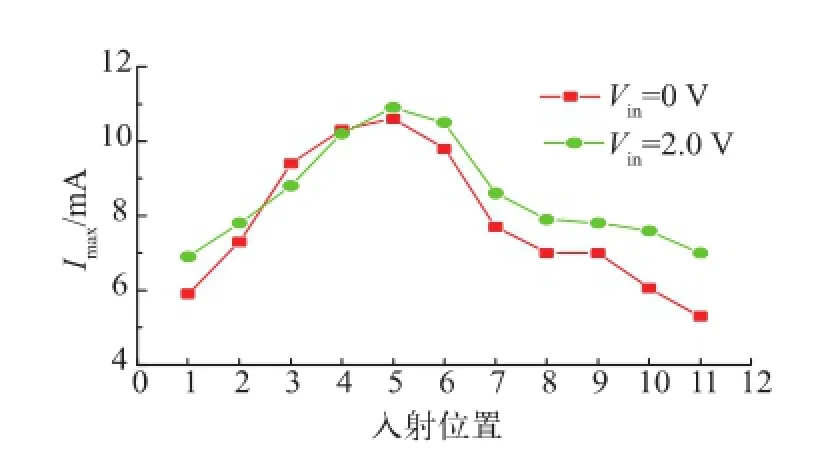

为研究粒子入射轨迹对器件闩锁效应的影响,本文共选取11个入射点(如图2),分别在输入电压为0 V和2.0 V的情况下进行轰击模拟。模拟过程中,NMOS和PMOS的漏极间距L1为0.86 μm,体接触距离NMOS和PMOS源区的距离L2为0.28μm,粒子垂直入射器件表面,入射能量LET值为100 MeV·cm2/mg,工作温度为300 K。图3所示为不同输入电压条件下PMOS器件的最大源极收集电流随入射点的变化情况。相比输入电压0 V的情况,输入电压为2.0 V时PMOS器件的源极收集电流增加。通过模拟分析可以看出无论输入高压还是低压,CMOS器件发生单粒子闩锁的敏感区域基本都在远离体接触的有源区附近,最大的电流收集点在NMOS器件的漏极。因此,重离子入射的最敏感点在NMOS器件的漏/体结。

图3 不同入射位置对应的PMOS源极收集电流

3.2 温度对SEL的影响

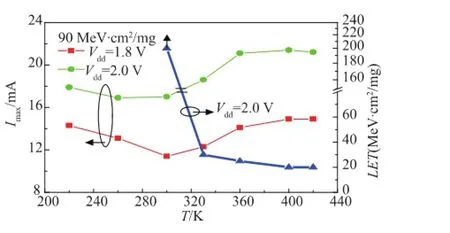

仿真中,NMOS和PMOS的漏极间距L1为0.86 μm,体接触距离NMOS和PMOS源区的距离L2为0.28 μm。CMOS器件的Vin输入电压0 V,结合器件敏感区的分析,选择对SEL较敏感的NMOS管的漏/体结进行重离子垂直轰击模拟,研究PMOS器件的最大源极收集电流和LET阈值随温度变化的关系,模拟温度范围为220~420 K。

由图4可见,当工作温度从300 K增加到420 K时,PMOS器件的最大源极收集电流先增加并接近饱和。这是因为随着温度升高,半导体中本征载流子浓度迅速增加,电流密度随之增大,CMOS闩锁电流显著增加。温度从300 K降至220 K时,CMOS的最大收集电流增加。随着工作电压增加,CMOS器件中电场强度增大,PMOS的源极对体电流的收集能力增加,相比1.8 V的情况,当Vdd为2.0 V时,PMOS的源极收集电流增加了5~7 mA。随着工作温度的增加,CMOS器件发生闩锁的LET值逐渐减小。这是由于散射作用,硅中的电阻随着温度的升高而呈指数增加,寄生电阻的增加会降低阱中要达到二极管压降所需的电流,使得两个寄生的晶体管更容易发生导通,进而增加了闩锁的敏感性。

图5所示是不同工作温度下PMOS源极收集电流随时间的变化关系曲线。粒子垂直入射器件表面,入射能量LET值为90 MeV·cm2/mg,工作电压2.0 V。可以看出,在工作温度300 K时,粒子入射引起了较大的电流脉冲,但很快就恢复到了正常的工作状态,并不能使电路发生闩锁。随着工作温度的增加,粒子入射引起的大电流无法恢复,电流保持在15 mA以上,CMOS电路发生单粒子闩锁效应。

图4 PMOS源极最大收集电流和闩锁LET阈值随温度变化情况

图5 不同工作温度下PMOS源极收集电流随时间变化情况

3.3 L1、L2和外延厚度对SEL的影响

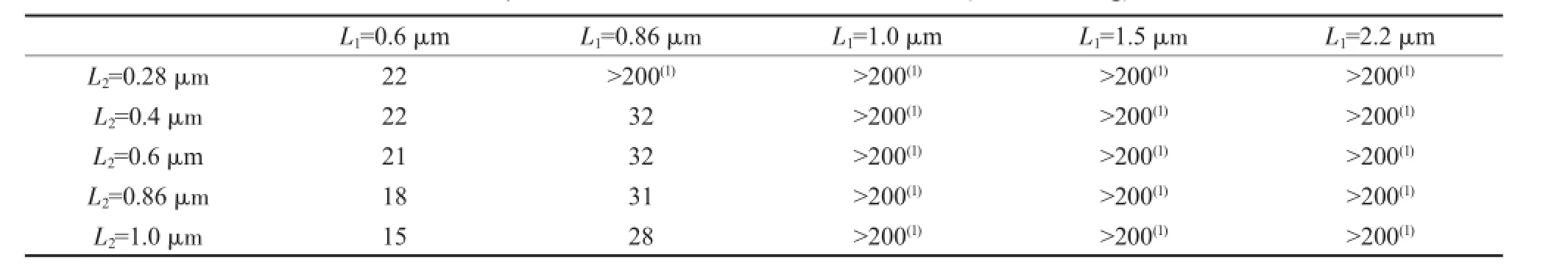

单粒子闩锁效应受两个寄生双极晶体管的放大倍数和电阻的影响,为了提高抗SEL的水平,我们对标准CMOS器件的尺寸L1、L2进行仿真模拟,研究不同的MOS间距和接触位置对SEL敏感性的影响。同时,采用外延工艺降低衬底电阻,提高CMOS器件的抗SEL能力。仿真模拟时,选用P型掺杂外延材料,外延层电阻率10~20 Ω·cm,外延衬底电阻率0.01 Ω·cm,工作温度300 K,工作电压2.0 V,输入电压2.0 V,设置粒子垂直入射NMOS管漏/体结。表1、表2分别是3.2 μm和4.0 μm外延工艺的CMOS器件发生单粒子闩锁LET阈值。

表1 3.2 μm外延工艺下,单粒子闩锁LET阈值(MeV·cm2/mg)

表2 4.0 μm外延工艺下单粒子闩锁LET阈值(MeV·cm2/mg)

由表1、表2可见,随着体接触距离L2的增加,电路的SEL敏感性提高。这是因为接触电阻R1和R2阻值增大,对于给定的电流意味着寄生双极晶体管的压降增大,CMOS电路发生闩锁的正反馈作用得到增强。NMOS和PMOS间距L1增加,导致电阻R3和R4的阻值增加,根据串联电路的特性,寄生双极晶体管T1和T2的发射结压降减小,降低了CMOS电路发生闩锁的敏感性。当L1=1.0 μm时,L2从0.28 μm增加到1.0 μm,3.2 μm外延工艺CMOS器件的单粒子闩锁LET阈值超过200 MeV·cm2/mg,而4.0 μm外延工艺CMOS器件的单粒子闩锁阈值不超过18 MeV·cm2/mg。可见,在版图结构一致的情况下,采用3.2 μm外延工艺可以提高电路的抗SEL能力。当L1≥1.5 μm时,两种外延工艺的CMOS器件抗SEL能力高达200 MeV·cm2/mg以上,然而大大增加了版图面积。当L1≤0.86 μm时,4.0 μm外延工艺CMOS器件容易发生SEL效应。因此,版图尺寸选择L1=0.86μm、L2=0.28 μm时,采用3.2 μm外延工艺可以使得电路的单粒子闩锁LET阈值超过200 MeV·cm2/mg。

4 电路试验验证

采用0.18 μm CMOS工艺实现的电路样品进行重离子辐照试验,辐照离子为能量1985.5 MeV的209Bi离子,被测器件均经过正面开封装处理且处于正常工作状态。电路采用双电压工作方式,即内核采用电源管理电路产生1.8 V工作电压,而与PAD接口电路则采用3.3 V供电电压,产生摆幅为3.3 V的电平。图6是SRAM单粒子测试系统测试流程图,开始测试后先确定被测芯片在未开启束流情况下的存储数据是否正确,即写入测试向量并验证,验证无误后再开启束流,进行被测芯片的单粒子效应数据对比测试。

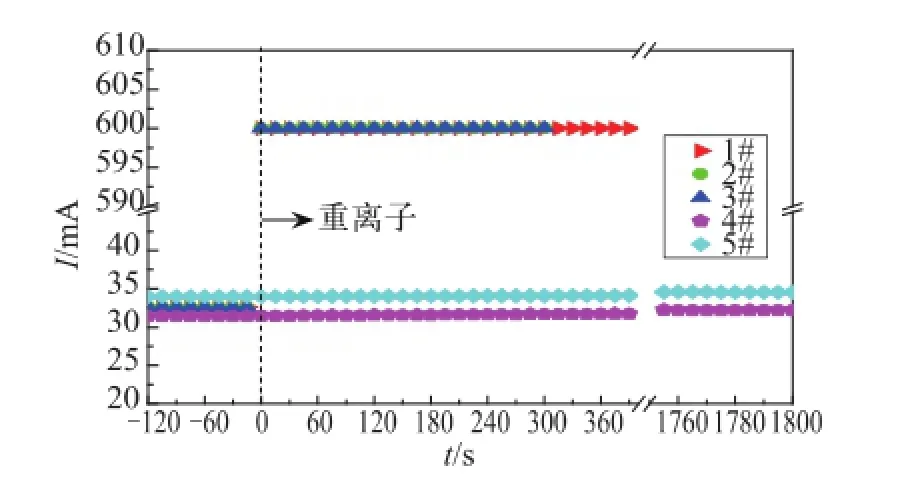

通过前面的仿真发现,电路工作温度对单粒子闩锁效应影响很大,但目前国内单粒子辐照试验中电路只能采用常温工作,因此,辐照试验采用温度300 K。图7所示是SRAM电路样品的SEL试验监测电流随辐照时间的变化关系曲线。电路样品共5颗,L1=0.86μm,L2=0.28 μm,其中1#~3#是4.0 μm外延工艺,4#、5#是3.2 μm外延工艺,入射粒子的能量LET值为99.75 MeV·cm2/mg。单粒子入射前,5颗电路样品的电流较低,电路性能正常。重离子辐照后,1#~3#样品电路在出束后电流高达600 mA,说明电路发生单粒子闩锁。4#和5#样品电路在辐照过程中输出电流分别为32 mA和34 mA,电路没有发生闩锁效应。试验表明,3.2μm外延工艺可以提高CMOS电路的抗SEL水平。

图6 SRAM单粒子测试系统测试流程

图7 输出电流随辐照时间的变化关系

5 结论

本文简要分析了单粒子闩锁效应的机理,基于TCAD模拟器研究CMOS电路发生闩锁的敏感区,并研究工作电压、工作温度、体接触距源区间距、NMOS和PMOS间距、外延工艺对单粒子闩锁敏感性的影响。仿真模拟表明,工作电压和工作温度对电路的SEL敏感性影响很大,调整寄生电阻大小可以有效抑制单粒子闩锁的发生,同时考虑到芯片版图面积,可以通过工艺加固提高电路抗SEL水平。单粒子试验证明,采用3.2 μm外延工艺可以有效减小版图设计面积,并提高电路的抗单粒子闩锁能力。

[1]Bruguier G,Palau J M.Single Particle Induced Latchup[J]. IEEE Transactions on Nuclear Science,1996,43(2): 522-532.

[2]Leavy J F,Poll R A.Radiation Induced Integrated Circuit Latchup[J].IEEE Transactions on Nuclear Science,1969, NS-16:96-103.

[3]Troutman R R,Zappe H P.A Transient Analysis of Latchup in Bulk CMOS[J].IEEE Transactions on Nuclear Science, 1983,ED-30(2):170-179.

[4]Kolasinski W A,Blake J B,Anthony J K,et al.Simulation of Cosmic Ray Induced Soft Errors and Latch-up in Integrated Circuit Computer Memories[J].IEEE Transactions on Nuclear Science,1979,26(6):5087-5091.

[5]Petersen E L.The Relationship of Proton and Heavy Ion Thresholds[J].IEEE Transactions on Nuclear Science,1992, 39:1600-1604.

[6]McNulty P J,Abdel-Kader W G.Simple Model for Proton-induced Latch-up[J].IEEE Transactions on Nuclear Science,1993,40:1947-1951.

[7]Levinson J,Barak J,Zentner A,et al.On the Angular Dependence of Pronton Induced Events and Charge Collection[J].IEEE Transactions on Nuclear Science,1994, 41:2098-2102.

[8]Schwank J R,Shaneyflt M R,Baggio J,et al.Effects of Angle of Incidence on Proton and Neutron-induced Single-event Latchup[J].IEEE Transactions on Nuclear Science,2006,53:3122-3131.

[9]Normand E,Wert J L,Majewski P P,et al.Single Event Upset and Latchup Measurements in Avionics Devices Using the WNR Neutron Beam and a New Neutron-induced Latchup Model[C].NSREC Radiation Effects Data Workshop,1995:33-38.

作者简介:

宋长庚(1984—),男,河北人,本科,从事NAND flash工艺整合研发工作。

Simulation and Design of SEL for 0.18 μm CMOS Devices

LI Yanfei,WU Jianwei,XIE Rubin,HONG Genshen

(China Electronics Technology Group Corporation No.58 Research Institute,Wuxi 214072,China)

The high-energy particles of large quantities from outer space may lead to Single Event Latch-up (SEL)in CMOS devices.The paper conducts studies on SEL for CMOS inverter using 0.18 μm CMOS technology and the TCAD method.The triggering mechanism of SEL is at first discussed for further analysis on particle incident position,voltage,temperature,distance between active region and body,NMOS and PMOS spacing,as well as radiation-hardened process.Then the optimal structure is obtained.The heavy ion test performed thereafter shows that in the 3.2 μm epitaxial process the SRAM circuit has a high LET threshold of 99.75 MeV·cm2/mg with L1=0.86 μm and L2=0.28 μm.

single event latch-up;TCAD;radiation-hardened;heavy ion test;epitaxial process

TN406

A

1681-1070(2017)02-0043-05

李燕妃(1987—),女,福建福安人,硕士研究生,毕业于电子科技大学微电子学与固体电子学专业,现从事抗辐射集成电路工艺集成技术研究。

2016-10-14