基于FPGA的Rijndael-Ecc加密系统的实现

2017-02-27吉兵陈振娇王兆尹范炯

吉兵,陈振娇,王兆尹,范炯

(中国电子科技集团公司第58研究所,江苏无锡214072)

基于FPGA的Rijndael-Ecc加密系统的实现

吉兵,陈振娇,王兆尹,范炯

(中国电子科技集团公司第58研究所,江苏无锡214072)

针对目前物联网易被攻击的特点,提出一种基于FPGA的Rijndael-ECC混合加密系统。方案采用Rijndael模块对数据进行加密,用散列函数加密算法处理数据得到数据摘要,用ECC加密算法实现对摘要的签名和私钥的加密,各模块采用并行执行的处理方式。同时利用流水线思想对Rijndael的轮单元结构进行了改进,提高了整个加密系统的工作效率,完全满足了物联网对于稳定性、功耗以及处理速度的要求,给数据传输的安全性提供了高强度的保障。

FPGA;Rijndael;椭圆曲线加密算法;数字签名

1 引言

物联网的广泛使用带来了诸多类型的安全威胁,随着片上系统(SoC)和低功耗嵌入式技术的飞速发展,使得物联网广泛应用于国防军事、生物医疗、城市交通、国际反恐等诸多需严格保障信息安全的领域,因此如何为物联网络提供更可靠的安全保障已经成为研究的热点[1]。

自2013年以来,随着物联网概念的火热,市面上出现了大量基于物联网开发的智能传感器设备,从智能家居到医疗卫生,这些设备与我们的安全密不可分。近年来关于黑客频繁入侵智能终端的报道越来越多,对于人们的安全隐私造成了极大的威胁,由于安全系统本身商业价值较低的原因,使得物联网安全发展十分缓慢。值得注意的是自2015年开始,美国已出台了一系列关于物联网设备安全和隐私的规定。我国目前对于物联网设备安全还没有明确规定,安全问题一直是现代生活中的一部分,对于物联网设备的保护应当出现在其发展中的各个阶段,新的安全漏洞会不断涌现,因此有关于物联网安全问题的研究具有十分重要的价值。

目前在加密领域主要有两种较为流行的加密算法:对称加密算法和非对称加密算法。Rijndael作为美国政府加密标准(AES)的加密算法有着高效安全的优势,但其密钥管理较为复杂,并不完全适用于物联网开放式的工作环境,而椭圆曲线加密算法(ECC)有着十分简单的密钥管理系统,非常适用于物联网,但其工作效率远不如Rijndael加密算法,对于这两种加密算法的研究往往都是分开进行并无交集。为了更好地适用于物联网的工作环境,本文将两种算法进行结合,提出了一种基于FPGA的Rijndael-ECC混合加密系统的设计方案。

2 数据加密模块设计

本文所设计的系统主要包含两大功能:数据加密和身份认证。Rijndael负责数据与签名的加密传输,ECC算法主要用于实现ECDSA签名系统。为了保证整个系统的高效运行,本文将对各主要底层模块进行单独分析和设计,最后利用各模块搭建出整个加密系统。

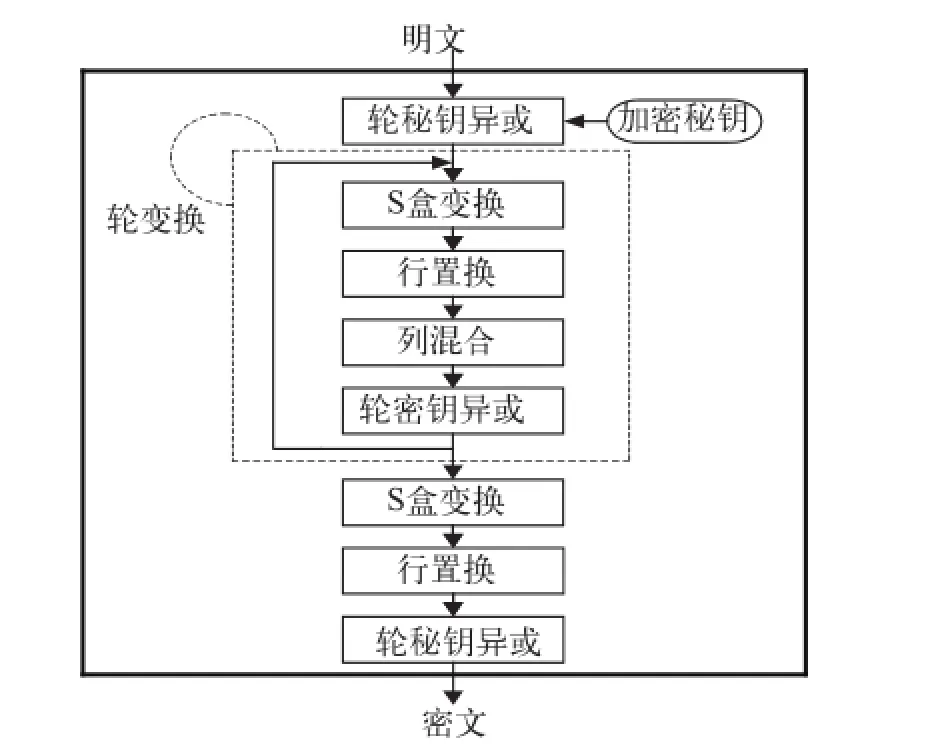

2.1 Rijndael算法基本结构

Rijndael算法的分组长度和密钥长度的设计十分灵活且安全性高。其算法基于排列和置换的迭代型分组的密码,能够有效防御各种攻击和线性密码分析[2]。它可以使用128位、192位和256位密钥,并且使用128位(16 B)分组加密和解密数据,转换的轮数Nr由秘钥长度m和分组长度n共同决定,AES加密的每一轮均由轮密钥异或、S盒变换、行置换和列混合4个变换组成[3],过程如图1所示。

图1 Rijndael加密流程图

2.2 基于FPGA的Rijndale模块设计

基于图1分析,可以发现Rijndale加密算法基本包含位移、异或、代换、混合这几个操作。已知位移操作不需要门电路,异或也比较简单。相对来说复杂的运算就是代换和混合操作,细分可分为字节的正逆代换、列混淆和逆列混淆[4]。因此对于Rijndale设计,用硬件描述完成这些复杂的组合逻辑电路是设计的难点。如今在高性能的硬件设计领域,流水线设计是当今速度最快也是比较成熟的一种技术手段。本文根据Rijndale加密流程各个步骤不同的运算方式,分别采用了并行处理和内部流水线两种混合的设计方案。

由图1中可以看出Rjindale加密算法是一个N次迭代的过程,每一轮的循环是加密过程最重要的步骤,因此我们将轮单元结构进行展开分析,如图2所示。

图2 Rijndale轮单元基本结构

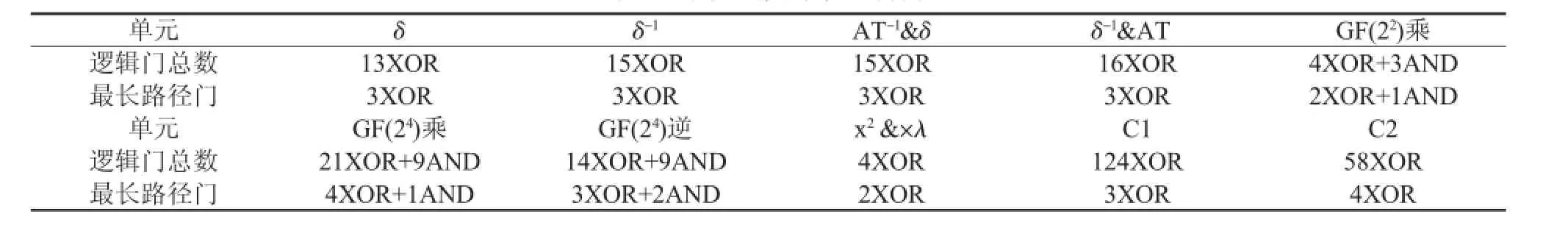

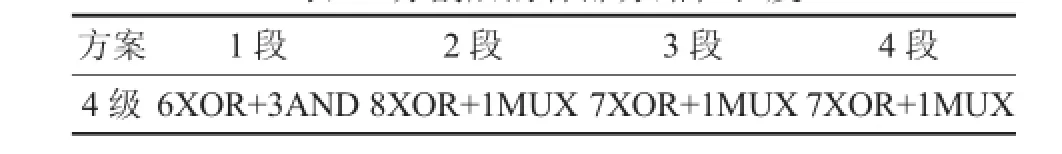

根据所示轮加密运算的内部逻辑单元运算,根据门等效原理[5],表1所示为各个单元的等效逻辑门个数。

根据表1所示的各个运算所需要的总逻辑门数、路径逻辑门以及延时逻辑门数,我们对轮单元结构进行优化设计,对很长的工作路径进行合理划分,确保分割模块可以获得较大的时钟频率。如果所设计的流水线级数过多,虽然运算单元的工作频率会越高,但是系统所消耗的资源或者面积就会越大。

表1 路径长度等效逻辑门

图3 Rijndale轮单元结构改进

表2 分割后的各部分路径长度

如表2结果所示,在关键路径上插入缓存器,将时间路径最大限度地均匀分割,将复杂的逻辑组合与简单的逻辑进行均分,使得单短组合逻辑简单化,缩短了路径,提高了每段逻辑组合的运算速度,使Rijndael在FPGA上实现了较高的吞吐率,进而带来了较高的系统工作效率。

Rijndael加密流程的另一个重要环节就是n轮密钥的生成,传统方案中密钥的生成总是要等待轮迭代的执行,密钥扩展单元就产生了大量空闲时间,十分浪费系统资源,利用FPGA平台自身的优势,使得轮迭代和密钥扩展单元两个模块同时执行,节约了密钥生成所消耗的时间,提高了整个加密流程的运行速度。

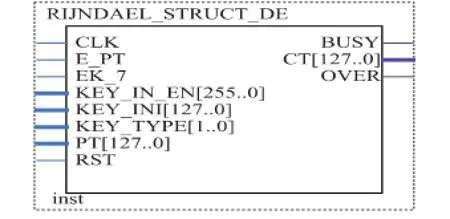

2.3 Rijndale电路模块的实现

为了保证整个加密系统的复用性和可升级性,原则上对能够单独设计的功能进行模块化设计以方便后续的使用与单独的方针测试。如图4所示为基于Quartus II 9.0的Rijndael加密程序的数字电路模块。

图4 Rijndale电路模块

3 ECDSA数字签名设计

3.1 ECC模块化设计

对于以广播的通信方式进行数据传递的物联网来说,这种开放式的特点相对容易受到非法窃听或者攻击。ECC公钥密码体制刚好具有极其相似的通信形式,而密码体制却具有极高安全性,因此二者的结合可有效地提高通信的安全性[6]。

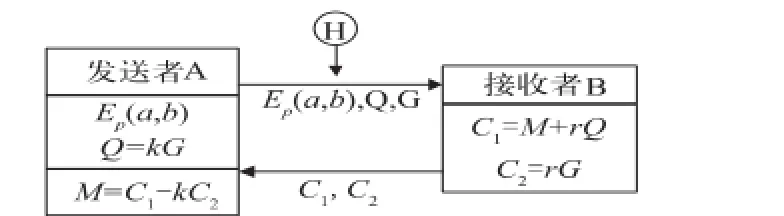

ECC算法的实现是在这两个基本的伽罗瓦域(Galois fields)中的一个:大素数阶域GF(p)或者是特征值为2的GF(2m)域。目前这两个域被公认可以提供相同的安全级别,本文将重点研究在有限域GF(2m)上运算[7],因为它可以在硬件中更有效地利用模2运算。本文所建立的ECC通信模型如图5所示。

图5 ECC通信模型

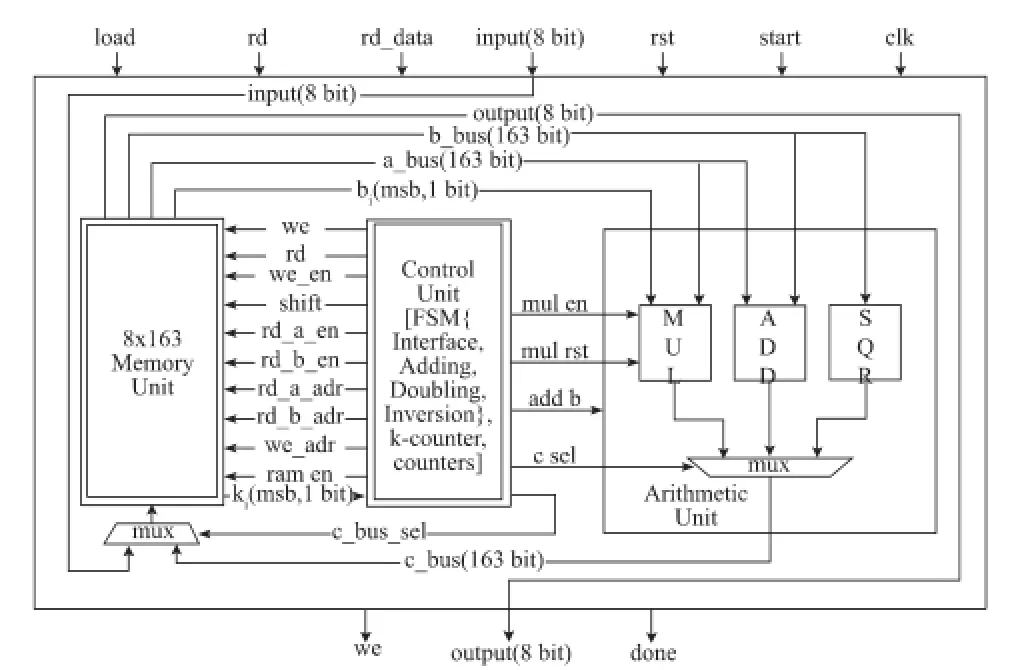

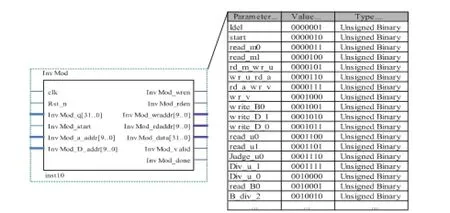

基于ECC加密算法的通信模型,本文设计了如图6所示的ECC算法的结构框图,并且为了方便算法在FPGA上的高效实现,本文将模运算的逆、加、乘等调用比较频繁的操作进行了单独设计,图7、图8为部分电路图。

图6 ECC电路框图

图7 模乘和模平方运算器件

图8 模逆运算逻辑器件

3.2 数据摘要模块

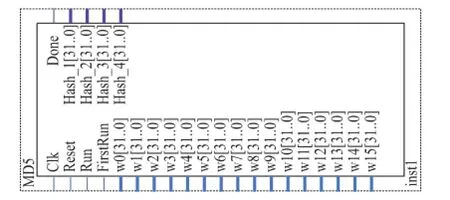

一个加密系统要具备比较完整的抗攻击能力,不仅要能防御被动攻击,同时也要能抵抗主动攻击,加密数据仅仅只能保证被动攻击的安全性,对于主动攻击,身份认证是强有力的手段,消息摘要是实现身份认证的核心技术[8]。本文将采用较为成熟的算法MD5,将其移植到FPGA上进行实现,如图9所示。

图9 基于Quartus II的MD5电路器件

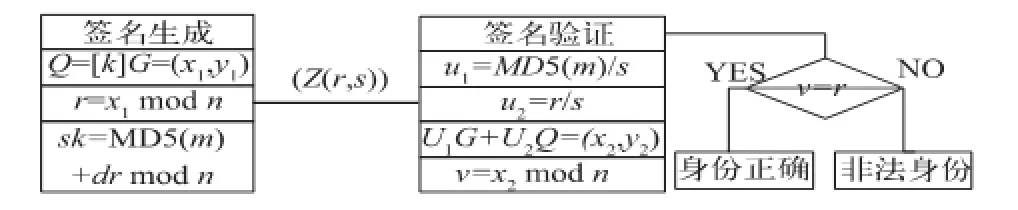

3.3 数字签名方案

在数据通信中,我们可以使用数字签名来对访问节点的身份进行认证,以确保信息的可靠性,本文将采用ECC密码体制对数据摘要进行加密等处理的方案产生数字签名,为了易于硬件算法的实现,将采用基于Montgomery的ECDSA签名算法[9],如图10所示为基于ECC的数字签名方案。

图10 数字签名流程

4 Rijindale-ECC加密系统的实现

4.1 系统加密模块

近年来我国农村空心化、留守化、衰败化的问题比较突出。交通不便、教育水平有限、医疗卫生欠缺、就业形势严峻、基础设施不完善等问题,使得乡村越来越难满足现代人的生产生活需求。不少乡村劳动力外流,只有老人、小孩留守家园。另外,传统社会维系邻里的乡贤宗法体系、农耕劳作体系、风水匠作体系已趋瓦解,在当下重构民主管理、团结互助、和睦友善的邻里关系迫在眉睫。

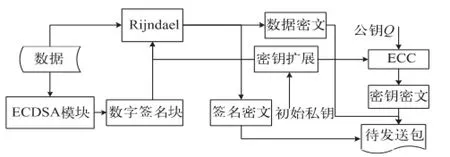

本文从安全、高效、灵活以及通用性的特点出发,结合1、2节中涉及的加解密、密钥安全、签名认证等底层模块,如图11所示给出了加密过程的具体步骤:

(1)对将要发送的数据作预处理,使用摘要算法得到数据摘要,Rijndael算法得到数据密文;

(2)ECC加密模块对密钥进行伪装得到密钥数据码;

(3)ECDSA签名算法对数据摘要进行签名处理得到唯一数字签名;

(4)Rijndael模块继续对签名进行加密处理得到签名码;

(5)对所有密文进行打包发送。

图11 加密系统

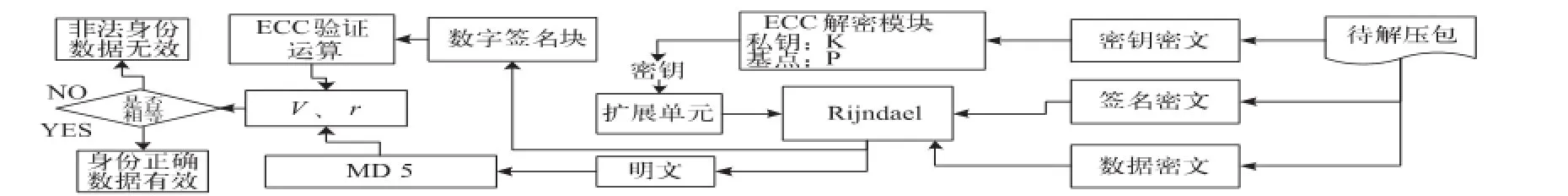

4.2 系统解密模块

解密系统如图12所示。

(2)调用ECC密码系统对密钥密文进行解密运算,解密出Rijndael加密所使用的密钥。

(3)调用Rijndael加密算法对签名和数据做解密操作,从中分理出签名信息和明文数据。

(4)调用MD5模块对明文信息进行处理,得到摘要信息;将摘要信息和签名信息送入ECC签名验证模块,分别得到信息r和v。

(5)当且仅当v=r时,身份可确认且信息有效,将数据送入下一环节;否则,身份错误并粉碎数据。

图12 解密系统

4.3 测试数据

本文采用基于EP4CE115的FPGA平台对加密系统进行开发实现,使用Quartus II 9.1综合仿真平台和ModelSim SE 6.5仿真软件[10]对每一个低层单元进行单独仿真和分析,可以更好地反映出系统的工作效率。

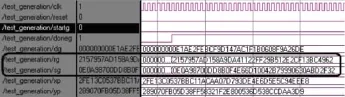

在Rijndael模块综合测试中,我们将加密流程中的字代换、行位移、列混合等过程中的关键变量信号添加到仿真文件中,可以更直观地看到每一步骤的变换过程,如图13所示。

图13 Rijndael加解密仿真图

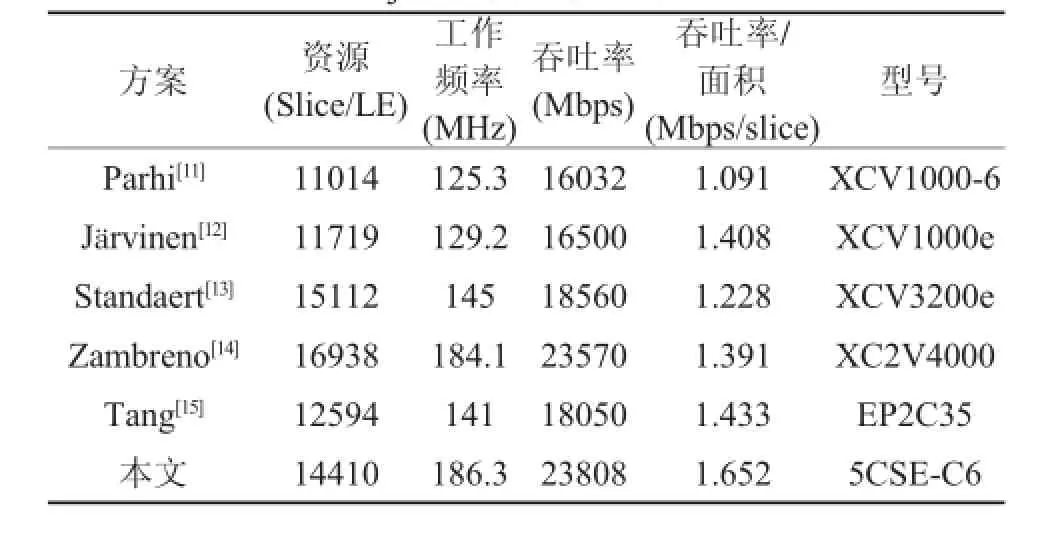

由图13可以看到Rijndael加密算法的4个基本工作步骤:轮密钥异或(add)、S盒变换(sub)、行置换(shift)和列混合(mix)。仅从仿真图来看,基于流水线设计的轮单元工作正常,相比传统方案中顺序执行的处理方法,本设计在一定程度上提高了加密的速度,具体仿真参数如表3所示。

表3 Rijndael算法模块综合测试

基于流水线的设计方案理论上会占用更多的资源,表3可以看出本方案在资源占用率上并无优势,但在吞吐率上有较大的提升,结果显示本方案的吞吐率达到了23808 Mbps,在牺牲了部分资源的情况下使得系统工作效率有了较为明显的提升。最终经过计算,在吞吐率/面积比这个衡量系统是否高效的指标上,本文设计具有较为明显的优势。

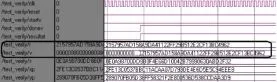

从图14和图15可以清楚地看出通过ECC加密算法得到的签名为rg=2157957AD158…,加密后的签名sg=0e0a987…,数字签名校验结果如图16所示,v=r=2157957AD158…,验证了本系统工作的正确性和可靠性。

图14 ECC仿真图

图15 加密系统仿真图

图16 签名校验仿真图

5 总结

本文根据物联网数据传输的特点,提出了基于FPGA的Rijndael-Ecc加密方案并得到了实现,测试数据也表明在一定程度上提高了数据传输的安全性,灵活性的设计方案也为继续优化加密系统做了良好的铺垫,今后将继续研究在系统工作效率不变的前提下进一步优化系统所占面积。

[1]BlilatA,Bouayad A,ElHouda ChaouiN,etal.Wireless sensor network:Security challenges[C].Network Security and Systems(JNS2),2012 NationalDaysof.IEEE,2012:68-72.

[2]Johnson D,Menezes A,Vanstone S.The elliptic curve digital signature algorithm(ECDSA)[J].International Journal of Information Security,2001,1(1):36-63.

[3]Herrera-Alzu I,López-Vallejo M.Design techniques for Xilinx Virtex FPGA configuration memory scrubbers[J]. IEEE Transactions on Nuclear Science,2013,60:376-385.

[4]Kaminsky A,Kurdziel M,Radziszowski S.An overview of cryptanalysis research for the advanced encryption standard; proceedings of the Military Communications Conference[C]. IEEE,2010-MILCOM 2010,F,2010.

[5]ZHI L.Reseach of Image Encryption Algorithm Based on S-DES;proceedings of the Computer Science and Electronics Engineering(ICCSEE)[C].IEEE,2012 International Conference on,F,2012.

[6]RIEBLER H,KENTER T,PLESSL C,et al.Reconstructing AES Key Schedules from Decayed Memory with FPGAs; proceedings of the Field-Programmable Custom Computing Machines(FCCM)[C].2014 IEEE 22nd Annual International Symposium on,F,2014.

[7]SUN J,ZHAO G,LI X.An Improved Public Key Encryption Algorithm Based on Chebyshev Polynomials[J]. Telkomnika Indonesian Journal of Electrical Engineering, 2013,11(2):864-70.

[8]Elbirt A J,Yip W,Chetwynd B,et al.An FPGA-based performance evaluation of the AES block cipher candidate algorithm finalists[J].Very Large Scale Integration(VLSI) Systems,IEEE Transactions on,2001,9(4):545-557.

[9]Shim J H,Kim D W,Kang Y K,et al.A Rijndael cryptoprocessor using shared on-the-fly key scheduler[C]. ASIC,2002.Proceedings.2002 IEEE Asia-Pacific Conference on.IEEE,2002:89-92.

[10]ZHU Y,ZHANG H,BAO Y.Study of the AES Realization Method on the Reconfigurable Hardware;proceedings of the Computer Sciences and Applications(CSA)[C].2013International Conference on,F,2013.

[11]ZHANG X,PARHI K K.High-speed VLSI architectures for the AES algorithm[J].Very Large Scale Integration (VLSI)Systems,IEEE Transactions on,2004,12(9): 957-67.

[12]J RVINEN K U,TOMMISKA M T,SKYTT J O.A fully pipelined memoryless 17.8 Gbps AES-128 encryptor; proceedings of the Proceedings of the 2003 ACM/SIGDA eleventh international symposium on Field programmable gate arrays[C].F,ACM,2003.

[13]STANDAERT F-X,ROUVROY G,QUISQUATER J-J,et al.Efficient implementation of Rijndael encryption in reconfigurable hardware:improvements and design tradeoffs[M].Cryptographic Hardware and Embedded Systems-CHES 2003.Springer.2003:334-50.

[14]ZAMBRENO J,NGUYEN D,CHOUDHARY A. Exploring area/delay tradeoffs in an AES FPGA implementation[M].Field Programmable Logic and Application.Springer.2004:575-85.

[15]JUN T,LIEJUN W.An improved rijndael encryption algorithm based on niosii[J].Information Technology Journal,2013,12(7):1434-8.

Rijndael-Ecc Encryption System Based on FPGA

JI Bing,CHEN Zhenjiao,WANG Zhaoyin,FAN Jiong

(China Electronic Technology Group Corporation No.58 Research Institute,Wuxi 214072,China)

According to the characteristics of the development of the Internet of things,a Rijndael-ECC encryption system based on FPGA is proposed.The scheme adopts the Rijndael module to encrypt data,using the hash function algorithm to get the data summary.ECC encryption algorithm is used to implement for the signature and encryption private key.Each module adopts parallel processing method.The structure of the wheel unit is improved by pipeline system.The work efficiency of the whole encryption system is improved. Fully meet the Internet of things to the requirement of stability,power consumption and processing speed.The security of data transmission is provided with high strength.

FPGA;Rijndael;ECC;ECDSA

TP309

A

1681-1070(2017)02-0028-05

2016-10-31