一种SATA III失调锁相环扩频时钟产生器设计

2016-12-20唐龙飞

龙 强 ,田 泽,唐龙飞,王 晋

(1.中航工业西安航空计算技术研究所,陕西 西安 710068;2.集成电路与微系统设计航空科技重点实验室,陕西 西安 710068)

一种SATA III失调锁相环扩频时钟产生器设计

龙 强1,2,田 泽1,2,唐龙飞1,2,王 晋1,2

(1.中航工业西安航空计算技术研究所,陕西 西安 710068;2.集成电路与微系统设计航空科技重点实验室,陕西 西安 710068)

扩频时钟产生器可以分散频率谐波的能量、减小单位带宽内的辐射能量,因此,扩频时钟产生器广泛应用在SATA III等系统中。给出了一种基于失调锁相环技术的SATA III扩频时钟产生器的设计方法。在扩频时钟产生器中,一个低频扩频信号和一个直接数字频率合成器进行频率合成,然后和一个高频信号混频,产生一个更高的调制参考源。扩频时钟产生器采用1.2 V 0.13 μm CMOS工艺,功耗为21.16 mW,主要的频率功率减小了16 dB,芯片面积0.7*0.45 mm2。测试结果表明,采用失调锁相环技术,扩频时钟产生器具有较低的时钟抖动,较小的EMI辐射功率,较好地满足了SATA III的需求 。

扩频时钟产生器;锁相环;SATA III;失调

0 引言

电磁干扰是电子产品尤其是SOC(片上系统)中一个必须处理的严重问题。扩频时钟技术是降低电磁干扰的影响最有效的方法之一。扩频时钟技术将中心频率附近的能量分散到一个较宽的带宽中,因此减小了时钟频率的基波和高次谐波的电磁干扰。在参考文献[1]中,给出了几种扩频技术,第一种扩频技术是通过直接调制压控振荡器的控制电压来达到输出信号的扩频,但是工艺的变化会影响工作频率的精度[2]。第二种方法是通过结合相位差值技术的多相位输出时钟源来实现扩频功能,但是相位差值器的非线性会严重降低扩频时钟的性能[3]。第三种方法是用精确的数字控制来调制分频器[4],通过小数频率合成器的辅助来实现高精度的扩频时钟,但是这种方法会引入低频杂散,必须通过Sigma-Delta调制器来进行噪声整形[5],因此,带宽被锁相环的窄带宽或者非线性而限制在一定的范围内,同时也增加的电路设计的复杂度。

针对上述几种扩频时钟产生器的优缺点,本文提出了一种失调锁相环扩频时钟产生器的结构,失调锁相环技术通过调制输入参考信号来实现扩频功能。采用较高的输入参考时钟频率可以增大带宽、减小参考时钟的时钟周期,当任何噪声注入到环路的时候,鉴频鉴相器(PFD)可以快速地校准输入误差,在扩频时钟产生器的输出端达到较低的本征抖动。

1 系统结构

1.1 失调锁相环

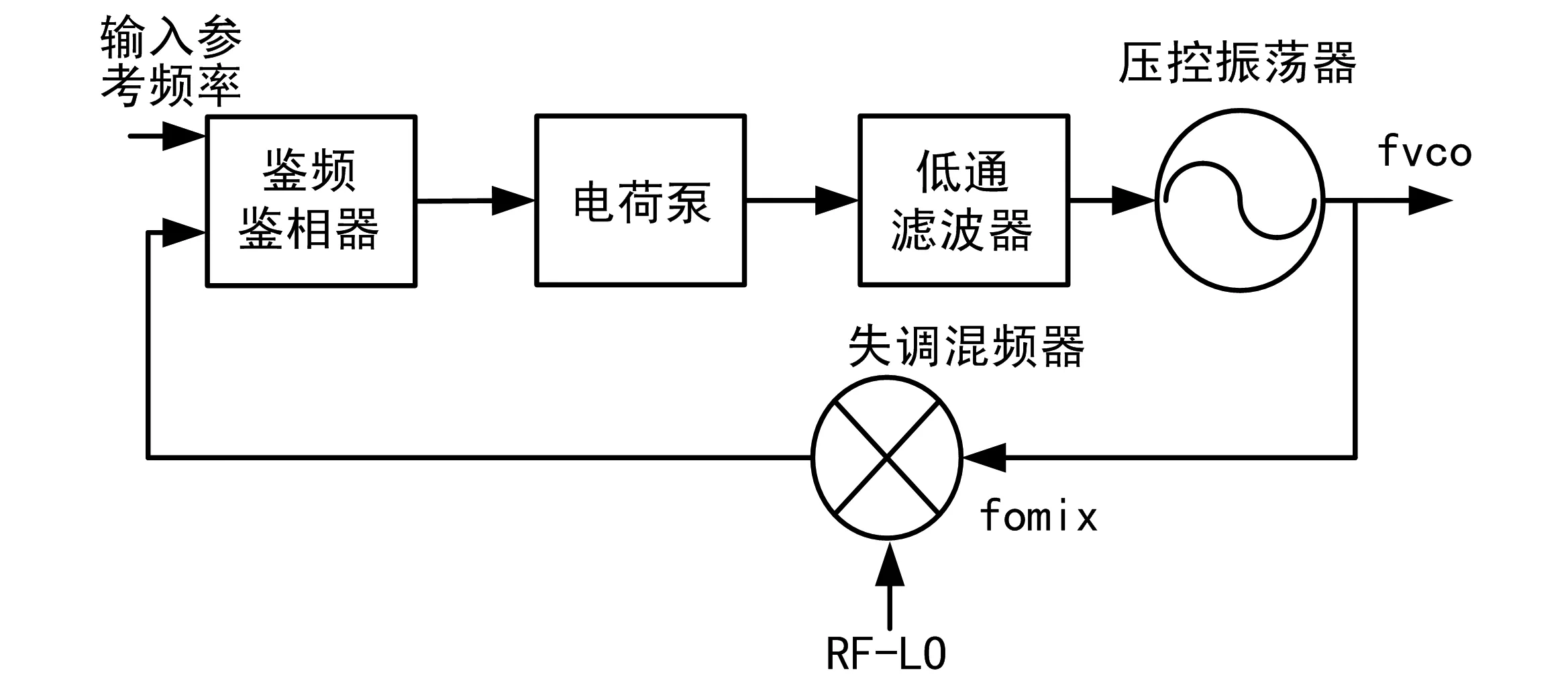

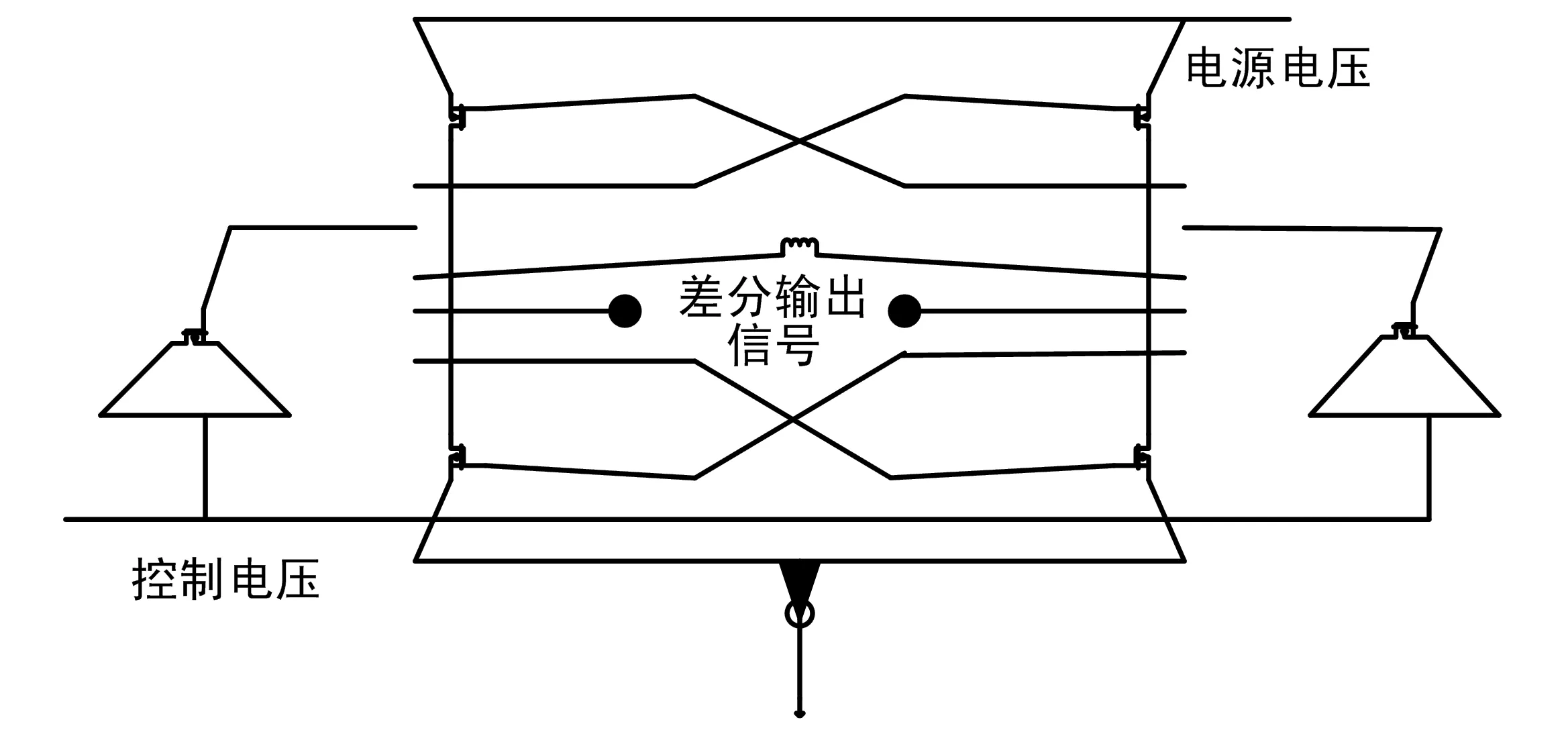

失调锁相环广泛应用在低成本全球移动通信(GSM)手持终端的发射路径中。失调锁相环由一个经典的锁相环和失调下混频器构成,其系统架构如图1所示[6]。

图1 失调锁相环系统架构

失调锁相环将调制的中频信号混频至射频载波频率,并跟踪带通滤波器的滤波信号,在不需要双工器的情况下可以抑制GSM接收频带内的噪声信号。失调锁相环与经典锁相环的不同,在于失调锁相环的压控振荡器的输出不变,而重新产生频率调制参考输入。失调锁相环的这种特性适用于低成本和低功耗的无线收发器等应用领域。

1.2 扩频时钟产生器架构

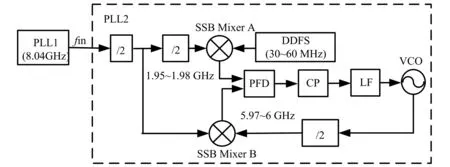

基于失调锁相环OPLL和直接数字频率合成器(DDFS)的扩频时钟产生器的电路结构如图2所示。

图2 扩频时钟产生器

扩频时钟产生器由2个环路构成,环路1产生一个高频参考时钟使得环路2具有更宽的带宽。环路2是一个失调锁相环,将扩频时钟的输出锁定在调制的参考输入信号上面。通过选择合适的带宽,级联的锁相环具有较小的抖动[7-9]。如果第一级锁相环可以实现一个适度频率的低相位噪声压控振荡器,那么通过锁相环的级联可以大大减轻参考频率和压控振荡器的相位噪声问题。DDFS产生一个30~60 MHz的扩频信号,扩频信号和环路1的输出信号进行单边带混频,为PFD产生一个参考时钟信号。在不被Sigma-Delta量化噪声影响的情况下,DDFS对于低频调制来说具有较小的频率分辨率和快速的频率切换。为了简化和验证基于失调锁相环的扩频时钟产生器的功能,DDFS信号和环路2的8.04 GHz的参考源由片外提供。

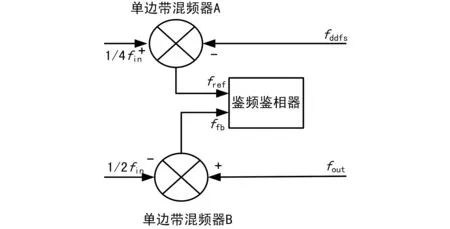

扩频时钟产生器中的失调锁相环的工作原理如图3所示。信号fin/4和fddfs通过混频器A混频,在PFD的输入端产生一个fref=fin/4-fddfs的参考信号,参考信号介于1.95~1.98 GHz之间;混频器B将fin/4和输出信号fout相混频,在PFD的反馈端口产生一个fdb=fout-fin/2的反馈信号。

图3 失调锁相环工作原理

当失调锁相环锁定在参考信号fref时,反馈信号fdb和参考信号fref完全等价,如式(1)所示:

(1)

得到:

(2)

fout介于5.97~6 GHz之间。

1.3 带内噪声

在典型的锁相环中,压控振荡器的相位噪声、参考信号的抖动和锁相环其他模块的噪声在输出端引入了抖动,在小于锁相环的环路带宽处的频偏处的抖动贡献表现为带内噪声。锁相环的带内噪声严重依赖于锁相环的输出频率和参考频率。低频抖动取决于电荷泵的噪声,电荷泵噪声电流转换成输出相位噪声的传输函数如式3所示[8]:

(3)

式中,SiCP为电荷泵的电流噪声谱,ICP为电荷泵电流,N为分频比。N/ICP与锁相环的环路带宽成反比,由式(3)可知,环路带宽越大,带内噪声越小;同时,在大的带宽下,VCO贡献较小的噪声,因此在输出端产生较小的抖动。本文设计的失调锁相环的带宽为5 MHz,远大于典型锁相环的带宽和DDFS 33 kHz的调制频率。

2 电路结构

2.1 单边带混频器

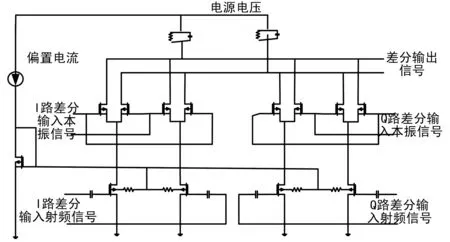

单边带混频器I/Q信号的失配影响其性能,因此,混频器的输出信号不是一个理想的正弦信号;除了失配之外,由于单边带混频器的输入信号谐波的交叉乘积项引入的非线性会在整个频带内引入杂散。在本文中,采用双平衡单边带混频器,双平衡单边带混频器如图4所示,双平衡单边带混频器取消了尾电流,提高了混频器的线性度,同时可以提高混频器的电压裕度,适合高速运算[10]。

图4 双平衡单边带混频器

2.2 压控振荡器

本文采用了一个采用片上电感的LC互补压控振荡器,压控振荡器具有低相位噪声、低功耗的特点,压控振荡器的电路图如图5所示。

图5 压控振荡器

采用NMOS和PMOS互补的结构,降低了压控振荡器的功耗,提高了压控振荡器的输出信号的幅度,降低了压控振荡器的噪声。采用了一个差分的电感,极大地减小了电感所占用的芯片面积。由于积累型的NMOS可变电容器具有单调的C-V曲线,因此采用了这种结构,保证了VCO具有固定的增益,同时可变电容器提供的15%的调谐范围较好的补偿了PVT的变化对VCO增益的影响。在仿真的情况下,VCO在1 MHz的频率偏移处达到了-110 dBc/Hz的相位噪声[11]。

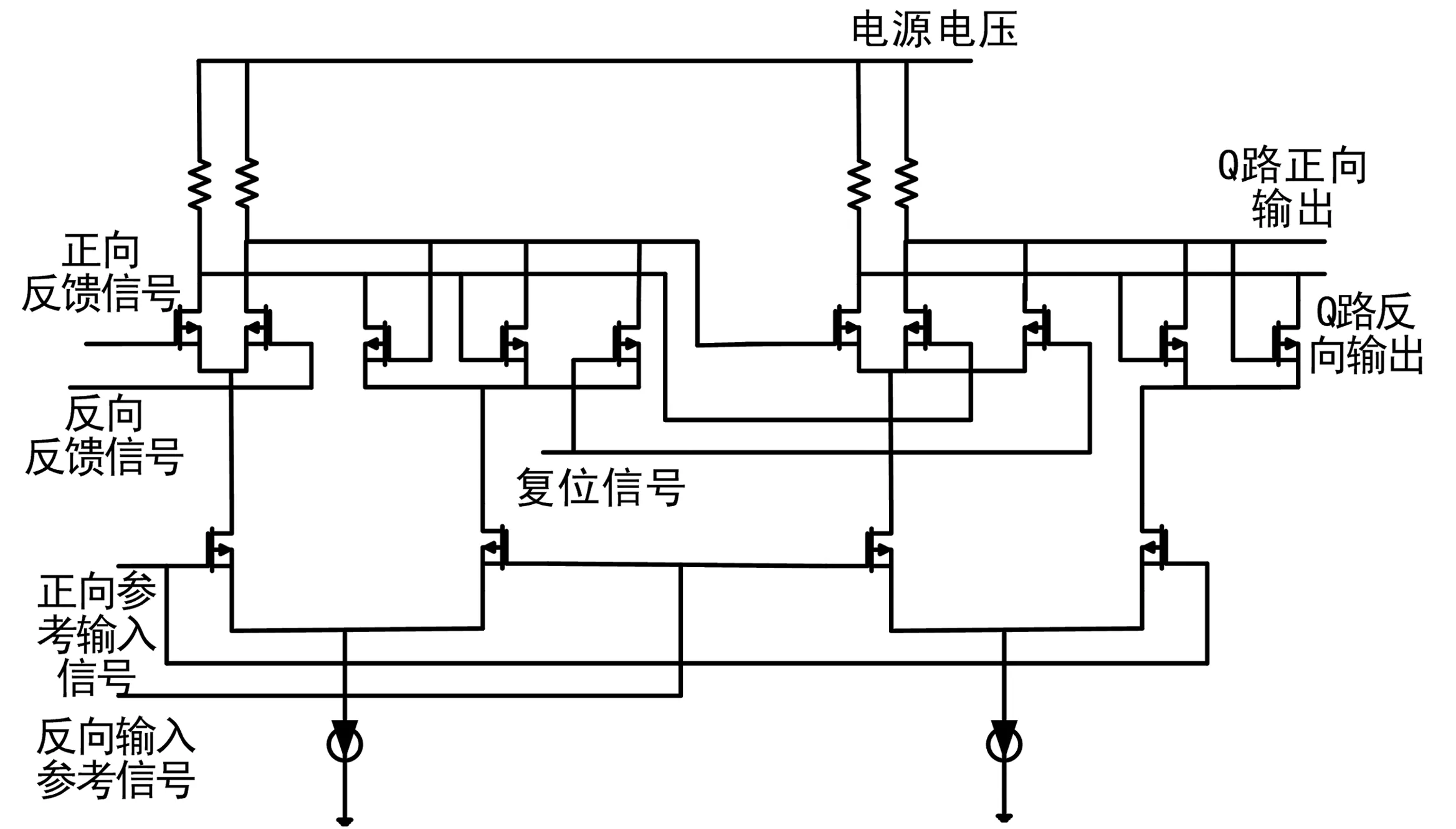

2.3 鉴频鉴相器

由于鉴频鉴相器采用高频的输入参考频率,因此,本文采用了预充电的鉴频鉴相器[11],它由2个同样的带有异步复位信号的D触发器构成,输出信号的激活直接依赖于输入信号,因此它不存在同时使电荷泵的UP、DN信号同时开启的门延迟,对电荷泵的充放电电流的失配的要求大幅降低。预充电鉴频鉴相器的电路图如图6所示。

图6 鉴频鉴相器电路图

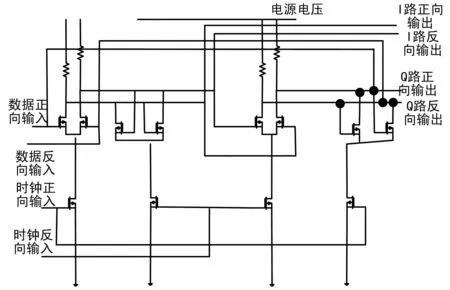

2.4 分频器

单边带混频器通过正交信号来产生2个频率的加、减操作。所采用的压控振荡器具有很高的震荡频率,为了适应高速分频的需求,分频器采用了无尾电流的CML电路,产生单边带混频器所需要的5.97~6 GHz的正交信号[12]。分频器的电路图如图7所示。分频器由2个CML D触发器构成主从结构,在设计过程中综合考虑电路的功耗和速度,采用合适的晶体管尺寸。

图7 CML分频器

3 测试结果分析

本文设计的扩频时钟产生器采用TSMC 0.13 μm CMOS工艺,芯片显微照片如图8所示。

图8 扩频时钟产生器芯片显微照片

8.04 GHz的射频输入信号和4相正交频率调制信号由安捷伦N4901A和泰克AWG520片外产生。

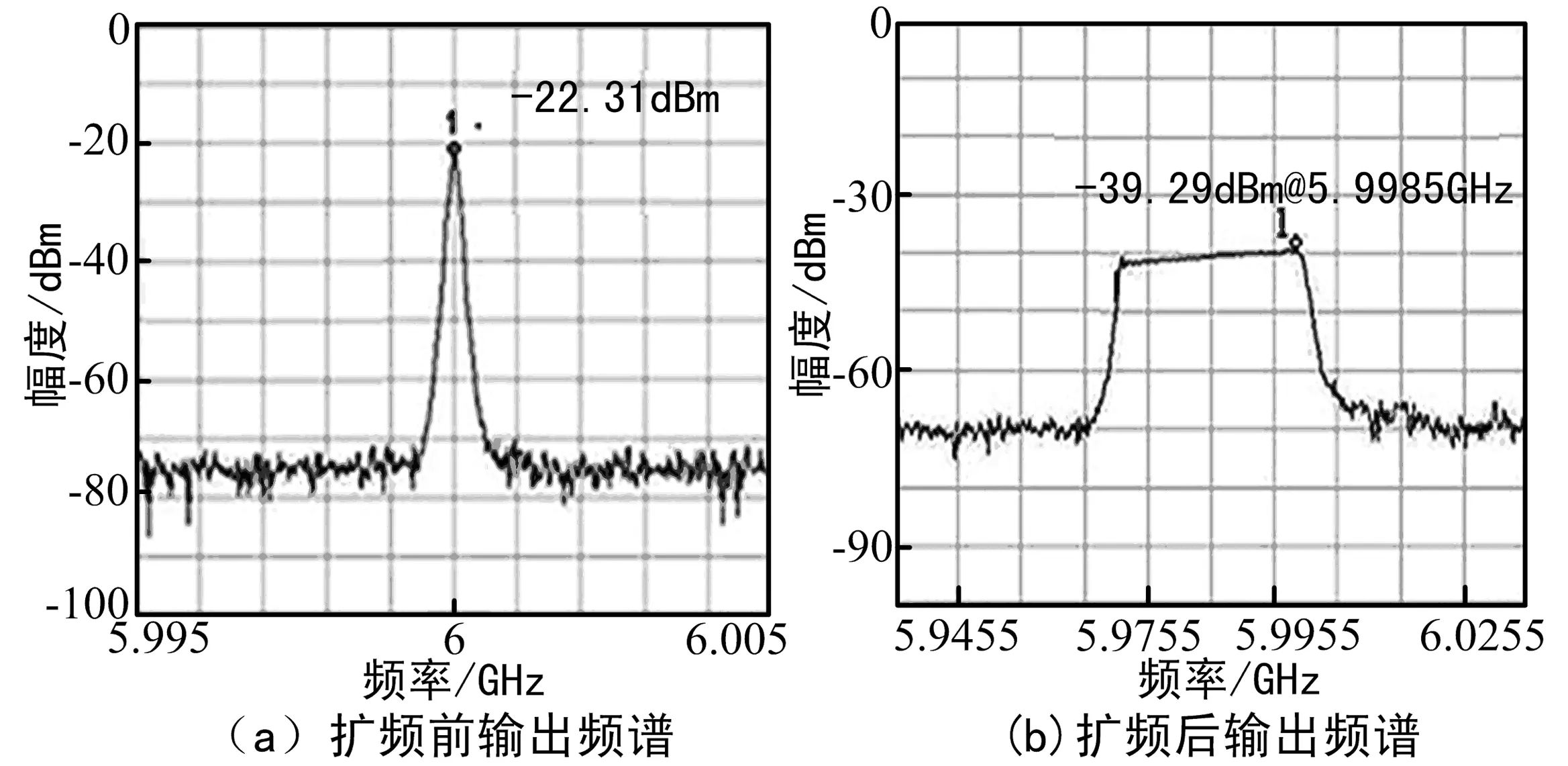

输出信号扩频之前与扩频之后的频谱如图9所示,通过对比2个输出频谱,可以轻易地得出,采用33 kHz的三角波调制输入参考频率,电磁干扰减小了19.98 dB,向下扩频了30 MHz,满足SATA III扩频5 000 ppm的设计要求。

图9 输出频谱

在1.2 V的电源电压下,扩频时钟产生器消耗21.16 mW的功率,也满足了电子类产品低功耗的需求。整个芯片面积仅有0.7*0.45 mm2。

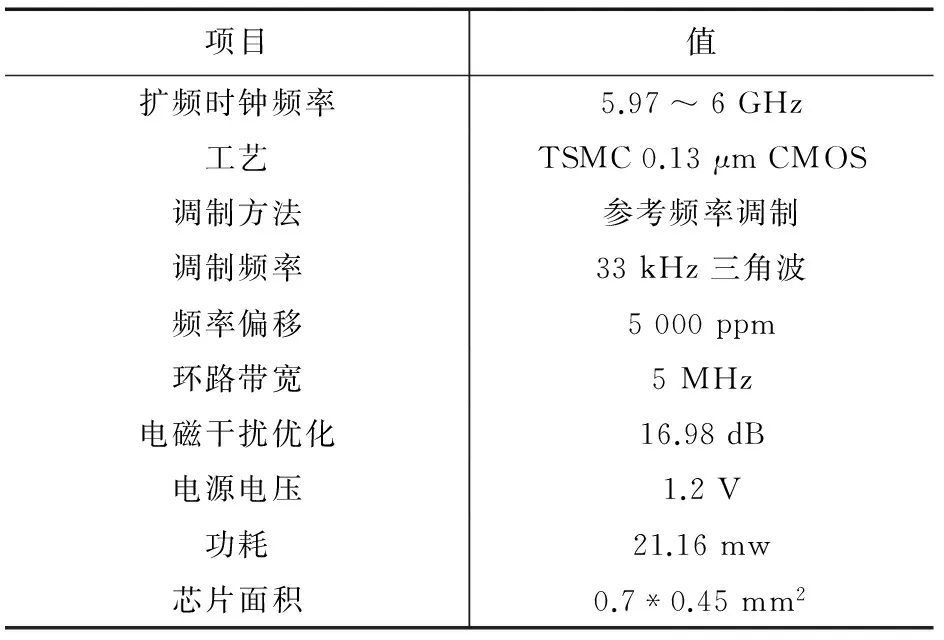

扩频时钟产生器的性能指标如表1所示。

表1 扩频时钟产生器性能指标

4 结束语

采用失调锁相环技术和DDFS技术实现了具有扩频功能的三角波调制扩频时钟产生器,详细分析了扩频时钟产生器的系统架构以及带内噪声,并给出了扩频时钟产生器中压控振荡器、分频器和鉴频鉴相器的设计电路,最后给出了实验结果,各项指标满足了SATA III对扩频时钟的要求。

[1] Hardin K,Fessler J T,Bush D R.Spread Spectrum Clock Generation for the Reduction of Radiated Emissions[C]∥Proc IEEE Int Symp On Electromagnetic Compatibility,1994:227-231.

[2] H S Li,Y C Cheng,D Puar.Dual-Loop Spread-Spectrum Clock Generator[C]∥ Proc IEEE Int.Solid-State Circuit Conf.Feb,1999:184-185.

[3] Aoyama M.3Gbps,5000ppm Spread Spectrum SerDes PHY with Frequency Tracking Phase Interpolators for Serial ATA[C]∥Proc.VLSI Circuits Symp.Jun.2003:107-110.

[4] Kokubo M.Spread-spectrum Clock Generator for Serial ATA Using Fractional PLL Controlled by Modulator with Level Shifter[C]∥Proc.IEEE Int.Solid-State Circuit Conf .,Feb.2005:160-161 .

[5] Lee H R,Kim O,Ahn G,et al.A Low Jitter 5000ppm Spread Spectrum Clock Generator for Multi-channel SATA Transceiver in 0.18 mm CMOS[C]∥Proc.IEEE Int.Solid-State Circuit Conf Feb.2005:162-163

[6] Yamawaki T.A 2.7-V GSM RF Transceiver IC[J].IEEE J.Solid-State Circuits,1997,32 :2089-2096.

[7] Razavi B.The Role of PLLs in Future Wireline Transmitters[J].IEEE Trans Circuits Syst.I,2009(56):1786-1793.

[8] Remco C H.A 2.5-10-GHz Clock Multiplier Unit With 0.22-ps RMS Jitter in Standard 0.18um CMOS[J].IEEE J.Solid-State Circuits,2004(39):1862-1872.

[9] Jieh-Tsorng Wu.A 2V 100MHz CMOS Vector Modulator[C]∥ Proc.IEEE Int.Solid-State Circuit Conf.,Feb.1997:80-81.

[10]Hsu J M.A 0.18-um CMOS Offset-PLL Up-conversion Modulation Loop IC for DCS 1800 Transmitter[J].IEEE J.Solid-State Circuits,2003(38):603-613.

[11]蔡鹏飞,李青平,杨 懿,等.基于谐波混频技术的宽带频综的设计[J].无线电通信技术,2013,39(4):73-75.

[12]张会珂,徐松毅,石 柳.多进制正交扩频技术在散射通信中的应用[J].无线电通信技术,2015,41(2):82-84.

Design on a SATA III SSCG Based on Offset Phase Locked Loop

LONG Qiang1,2,TIAN Ze1,2,TANG Long-fei1,2,WANG Jin1,2

(1.Aeronautical Computing Technique Research Institute,AVIC,Xi'an Shaanxi 710068,China;2.Aeronautical Science and Technique Key laboratory of Integrate circuit and Micro-system Design,Xi'an Shaanxi 710068,China)

In this paper,a spread spectrum clock generator(SSCG)based on Offset phase-locked loop(OPLL)technique for Serial AT Attachment 3(SATA III)is given.The SSCG can spread the energy of frequency harmonics and reduce the radiated power per unit bandwidth,so,the spread spectrum generator is widely applied in SATA III system.In the proposed architecture,a low frequency spread spectrum signal is synthesized by a direct digital frequency synthesizer(DDFS)and mixed with a high frequency signal to produce a higher modulated reference clock.The SSCG is manufactured by using a 0.13um CMOS process technology,and the chip area is 0.7*0.45mm2,the main tone power is reduced by 16dB and the power consumption is only 21.16mW from power supply of 1.2V.The test results show that the SSCG has low clock jitter,low EMI radiate power by using OPLL technology,which can satisfy the requirement of SATA III.

SSCG;OPLL;SATA III;EMI

10.3969/j.issn.1003-3114.2016.06.19

龙 强,田 泽,唐龙飞,等.一种SATA III失调锁相环扩频时钟产生器设计[J].无线电通信技术,2016,42(6):73-76.

2016-07-19

龙 强(1979—),男,工程师,博士,主要研究方向为:射频集成电路锁相环以及射频前端。田 泽(1967—),男,研究员,博士,主要研究方向为:VLSI设计、SoC设计方法学、嵌入式微处理器体系结构与VLSI实现、嵌入式应用系统开发。

TN792

A

1003-3114(2016)06-73-4