一种超低功耗的低压差线性稳压器环路补偿方法

2016-12-20刘晨来新泉钟龙杰杨伟

刘晨,来新泉,钟龙杰,杨伟

(1.西安电子科技大学CAD研究所,710071,西安;2.空军工程大学防空反导学院,710051,西安)

一种超低功耗的低压差线性稳压器环路补偿方法

刘晨1,2,来新泉1,钟龙杰1,杨伟1

(1.西安电子科技大学CAD研究所,710071,西安;2.空军工程大学防空反导学院,710051,西安)

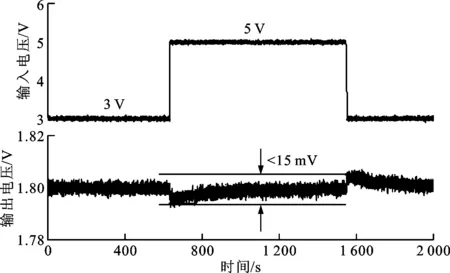

针对低压差线性稳压器(LDO)电路设计中为改善环路补偿的稳定性增加电流缓冲电路而带来额外功耗的问题,提出一种嵌入式LDO环路补偿方法。该方法在原LDO的误差放大器模块中,嵌入一个由晶体管和电容组成的电流缓冲电路,该结构与误差放大器的共源共栅输出级共用晶体管,由于整体电路中不增加新元器件,因此消除了引入缓冲电路所带来的额外功耗。仿真实验验证了加入电流缓冲电路后系统环路稳定性能得到了改善。采用联华电子公司0.5 μm 5 V的CMOS工艺线在LDO中进行了投片验证,实测芯片静态功耗电流仅为50 μA,当输入电压从3 V跳变到5 V时,输出电压的上冲与下冲都小于15 mV,负载电阻从18 kΩ跳变到9 Ω时,输出电压的最大变化小于20 mV。投片测试结果表明,该补偿方法可在提高系统环路稳定性的同时消除额外功耗。

集成电路设计;环路补偿;嵌入式结构;电流缓冲技术

在常用的低压差线性稳压器(LDO)设计中,为了提高转换效率,输出大负载电流,功率管需要具有较大的尺寸,但大尺寸必然会引入大电容,产生低频极点,影响环路稳定性[1]。

目前,环路稳定性的补偿方法大体分为两类:等效串联电阻(ESR)低频零点补偿[2-3]和密勒补偿[4-6]。其中,ESR低频零点补偿利用输出电容与其等效串联电阻形成一个低频零点,来抵消一个非主极点的附加相移,从而达到环路稳定性的要求。但是,在单位增益带宽内,要想获得精确的零极点对消是一件比较困难的事[2],而且当输出电容较大(如微法级),输出电流发生较大的阶跃性跳变时,输出电容的ESR会导致较大的输出过冲电压[3]。密勒补偿利用密勒等效定理,产生极点分裂的效果,使系统在带宽内获得足够的相位裕度,使环路能够稳定地工作。但是,密勒补偿在进行环路补偿的同时,也形成了前馈通路[4],故不仅有反馈电流流过补偿电容,同时前馈电流也流过了补偿电容,由此产生了右半平面的零点。如果控制不当,会引起更加严重的稳定性问题[5]。

电流缓冲技术是对密勒补偿技术的改进[6],该技术使流过补偿电容的电流具有了方向性,即仅有反馈电流能够流过补偿电容,很好地抑制了右半平面零点的产生,使系统环路的控制更加简单,可靠性增强,而且电流缓冲补偿技术并不需要ESR低频零点对环路进行补偿就可以获得很好的稳定性[7-8]。然而,增加电流缓冲电路会增加额外的电流支路,导致额外功耗。本文针对增加稳定电路带来额外功耗问题提出了一种改进的环路补偿电路结构。该结构利用LDO电路和电流缓冲电路共用晶体管,在改善稳定性的同时消除了额外功耗。

1 电流缓冲技术基本原理

1.1 极点分裂原理

密勒补偿与电流缓冲技术都利用了极点分裂的方式来达到环路稳定的目的,这里简述一下极点分裂的基本原理。

以一个两级运算放大器(简称运放)为例,gm1、gm2分别是第1级与第2级运放的跨导增益,R1与C1分别是第1级运放的输出电阻与输出电容,RL与CL分别是第2级运放的负载电阻与负载电容,Cc是补偿电容,两级运放的结构如图1所示。

图1 两级运放结构图

从图1中可以得到两级运放的电压总增益

Av=-Av1Av2

(1)

式中:Av1与Av2分别是第1级与第2级的电压增益,其表达式为

Av1=gm1R1

(2)

Av2=gm2RL

(3)

两级运放的传输函数为

(4)

式中:a≈Av2CcR1;b≈CLCcR1RL。

当系统的2个极点相距较远时,可以从式(4)中得到系统的零极点表达式

(5)

(6)

(7)

式中:z是系统零点频率;pd是主极点频率;pnd是次极点频率。

从系统的2个极点的表达式中可以很清楚地看到,如果系统中某些参数的改变使得系数a变大,则系统的2个极点会朝着相反方向移动,即主极点频率pd向着低频方向移动,而次极点频率pnd则向着高频方向移动,此时2个极点间的频距逐渐增大,形成了极点分裂效应[9]。本文2.3节就是利用该理论分析环路的稳定性。

1.2 电流缓冲技术分析

从式(5)可以看出,系统零点是1个右半平面的零点,与左半平面零点不同的是,它会在系统的相频响应中引入-90°的附加相移,从而使系统的环路稳定性变得更差,而这个右半平面零点的产生是补偿电容形成前馈通路的结果。图1中补偿电容Cc是双向的,即在反馈电流流过电容Cc的同时,也有前馈电流流过。当前馈电流流过补偿电容时,在输出节点上产生了1个输出信号。该信号在相位上与输入信号相同,而与放大器输出信号的相位相反,当该输出信号与放大器的输出信号大小相等时,就会产生1个零点,且是右半平面的零点。要想消除这个右半平面的零点,就必须阻断由补偿电容形成的前馈通路。

传统电流缓冲技术的电路结构如图2所示,其中Mcb是共栅级放大器,Vout1是前级运放的输出、Vout是运放gm的输出,小信号输入电流加在Mcb源极电流上,而漏端是输出级。由于没有电流损失,电流增益为1,而且Mcb的输入电阻较小,输出电阻较大,达到阻抗变换的作用,所以Mcb称为电流缓冲器[10]。

图2 电流缓冲补偿结构图

从图2中可以看出,由于串联了Mcb,使流过补偿电容的电流具有方向性,阻断了从Vout1到Vout的前馈通路,抑制了右半平面零点的产生[11]。

分析图2可知,电流缓冲技术实际上是密勒补偿的一种改进形式,但是图2中传统电流缓冲补偿需要电路提供额外的电流,这就增大了整个芯片的功率损耗。下面针对图2中的电路结构进行改进。

2 改进的电流缓冲技术及其应用

低压差线性稳压器(LDO)电路结构简单、易于集成,是目前十分流行的电源变换器[12]。本节以LDO为对象,利用电流缓冲技术的嵌入式结构进行LDO电路的改进。

2.1 嵌入式LDO电路结构

整个LDO电路由误差放大器、前馈通路、驱动级和功率级所组成,其结构如图3所示。

图3 嵌入式LDO电路框图

LDO的目的是输出恒定电压Vout,整个系统是一个负反馈环路。将输出电压的采样电压VFB与基准电压VREF做比较,其结果作为反馈信号来控制功率管MP0的开启程度,从而达到稳定输出电压的效果。

在LDO电路中,误差放大器的作用是当输出电压的分压值VFB不等于参考电压值VREF时,将这一误差电压放大;驱动级位于误差放大器的输出与功率管的输入之间,目的在于更好地驱动功率管。功率级由功率管MP0、负载电容CL与采样电阻R1、R2构成。前馈通路在电路启动时,跳过缓冲级建立一个从误差放大器直接到功率管的通路,从而大大减少了电路从启动到稳态的建立时间[13],显著改善了电路的瞬态响应。

起环路稳定作用的电流缓冲电路被嵌入进了误差放大器模块,通过共用元器件,达到消除额外功耗的目的。

2.2 超低功耗LDO环路补偿的电路设计

本文利用嵌入式结构进行LDO环路补偿的电路设计,即在原LDO的误差放大器模块中,嵌入一个由晶体管和电容组成的电流缓冲电路,本文设计的超低功耗LDO环路补偿的电路如图4所示。图中,电流缓冲电路由共栅级MN7与补偿电容Cc组成,特点在于该电路与原LDO电路的共源共栅输出级共用了MN7和MN9,分别替代了图2中Mcb和Ic的电路功能。其优点在于进行环路补偿的同时,不需要提供额外的电流给补偿电路,从结构设计上消除了引入电流缓冲电路所带来的额外功率。

Vb1~Vb4为后级电路的偏置电压;Vf1、Vf2为前馈电路的输入电压;Vea为后级驱动的输入电压;MP1~MP9为PMOS晶体管;MN1~MN9为NMOS晶体管;GND为信号地图4 本文误差放大器电路图

电路中其他元器件,晶体管MN1、MP1、MP2、MP3为整个电路提供了电压与电流偏置。晶体管MN2、MN3组成了第1级源极跟随器,进行电平移位操作,使得输入电平范围更加适合下一级放大电路。晶体管MP5~MP8,以及晶体管MN6~MN9组成了第2级折叠式共源共栅放大器,提供高增益与高输出阻抗。

下面,详细地分析LDO电路中采用嵌入式电流缓冲技术后对系统环路稳定性的影响。

2.3 消除额外功耗后环路稳定性分析

LDO的小信号等效电路如图5所示,其中gm1是折叠共源共栅运放的等效跨导,v1、Ro1与Co1分别是折叠共源共栅运放的输出电压、输出电阻与输出电容,gm2是驱动缓冲级的跨导,v2、Ro2与Co2分别是驱动缓冲级的输出电压、输出电阻与输出电容,gmp是功率级的等效跨导。

图5 LDO的小信号等效图

由小信号等效图可以写出各节点的电流方程,如式(8)~(11)所示

(8)

(9)

(10)

(11)

缓冲级的增益如式(12)所示

gm2Ro2≈1

(12)

联立式(8)~(12),并且忽略驱动缓冲级的输出电阻Ro2与输出电容Co2,可以得到电路的输出vout与输入vs之间的关系如下

1+CLRLs+CcRLRo1gmps+

(13)

从图3的电阻分压网络(R1和R2)可知

(14)

式中:B为反馈系数。将式(14)代入到式(13)中可得系统的传输函数

1+(CLRL+CcRLRo1gmp)s+

(15)

注意到,式(15)分母的一阶分量中包含项CcRLRo1gmp,该项可以写为

CcRLRo1gmp=gmpRLCcRo1=Av2CcRo1

(16)

式(16)中,Av2Cc是密勒等效电容,与传统密勒补偿中的等效电容(1+Av2)Cc不同,这也从另一方面说明了电流缓冲器对前馈通路的阻断,而分子中的-BRo1RLgm1gmp则是系统的环路增益。

因为LDO的极点会随着负载的变化而变化,所以需要在不同的负载情况下对系统进行讨论。

(1)当负载为轻载时,输出极点为主极点,此时可以从式(15)中得到主极点的频率pd和次极点的频率pnd分别为

(17)

(18)

而零点与另一个极点相对消,此处便不再给出。与式(6)、(7)相比,式(17)、(18)并没有发生极点分裂。

(2)当负载为重载时,输出极点在高频,而由密勒等效电容产生的极点成为了主极点,这同样可从式(15)中得到主极点的频率和次极点的频率分别为

(19)

(20)

与轻载时的情况一样,也有1对零极点对消。与式(6)、(7)相比,式(19)、(20)发生了极点分裂,当增大gmpCc时,主极点向低频方向移动,而次极点向高频方向移动。当gmpCc取值适当时,可以使单位增益带宽内仅存有1个极点,保证了足够的相位裕度,获得了很好的稳定性。

可以看到,通过电流缓冲技术嵌入式结构可以使LDO在整个负载电流范围内稳定地工作,且仅需要很小的补偿电容,在该设计中补偿电容Cc只有4 pF,就当前的CMOS工作技术可以轻易地将该电容集成于芯片中。

3 电路仿真验证与实测结果分析

为了验证本文电流缓冲补偿技术的正确性与有效性,采用计算机仿真做初步验证,然后将芯片制造出来进行实际测试验证。计算机仿真使用CADENCE公司提供的基于Linux操作系统的前端设计仿真环境平台,在平台中调用的仿真器为Synopsis公司提供的HspiceS,仿真器所使用的器件模型为联华电子公司所提供的0.5 μm 5 V CMOS器件模型。

3.1 电路仿真及实测结果分析

在CADENCE仿真平台中,按照设计LDO的电路图并设输出电容是0.22 μF,得到环路增益和相位裕度的仿真结果如图6所示。从图6中可以看出,在全载、轻载以及空载3种情况下,单位增益带宽内都仅有1个极点,且由负载电容与其等效串联电阻所产生的零点处在带宽外的高频处,这也验证了前文所述的电流缓冲补偿技术并不需要ESR零点的补偿就可以获得很好的频率响应。通常,设计裕度大于45°时,LDO的稳定性认定为可接受[1]。经仿真验证,本文设计的LDO在全负载范围内最小的相位裕度为55°。

图6 本文LDO的环路增益与相位裕度仿真结果

以下为实际测试电路2个关键指标输入线性调整率和负载线性调整率的结果。

输入线性调整率。在负载电容为0.22 μF、负载电阻为18 Ω的情况下,设计的稳压器在输入电压从3 V到5 V变化时输出电压的瞬态响应曲线如图7所示。输出电压的变化小于15 mV,即该稳压器的输入电压的变化对于输出电压的影响可以忽略。

图7 本文LDO的线性瞬态响应曲线

图8 本文LDO的负载瞬态响应曲线

负载线性调整率。在输出电压为1.8 V、负载电容为0.22 μF的情况下,LDO的负载电阻从18 kΩ跳变到9 Ω时输出电压的变化情况如图8所示。输出电压的最大变化小于20 mV,略微大于输出电压的1%,这20 mV的变化包括了输出上冲与下冲。测试结果表明该LDO有良好的瞬态特性。

以上的实测结果显示,嵌入式结构电流缓冲技术在稳定性和瞬态响应特性这2个重要性能指标上能够达到传统电流缓冲技术水平。

同时测试结果表明,所设计的稳压器的输入电压范围从2.5 V到5.5 V,最小输出电压为1.8 V,最小漏失电压仅为0.5 V,具有较高的电压转换效率。其静态电流最大只有50 μA,这就在很大程度上降低了整个电路的功率损耗,并且可提供的最大负载电流为150 mA。

3.2 实测参数对比及结果分析

嵌入式电流缓冲电路同其他环路补偿电路参数指标的比较,如表1所示。其他环路补偿电路选取相近参考文献[11,14]的电路参数指标。

表1 本文电路与参考文献电路的参数比较

注:Imax是芯片最大的输出电流;IQ是芯片本身所消耗的电流;Vout是芯片所支持的输出电压;Cout是芯片所需要的滤波电容;Vo是芯片输出电压在经历空负载输出电流到满负载输出电流时输出电压的变化峰值;RPSR为电源抑制比。

由表1可见:①本文设计的芯片在静态功耗电流方面消耗很小,文献[11]和文献[14]的静态功耗电流分别为111 μA和60 μA,而本文设计芯片的静态功耗电流仅为50 μA;②本设计拥有非常好的瞬态响应能力(空载到满载的电压跳变为20 mV,远小于其他设计)。通常来讲瞬态响应能力和环路带宽是相关的,良好的瞬态响应需要良好的环路补偿设计支持[1]。这很好地反映了本文所提出的嵌入式结构电流缓冲技术的有效性。

4 结 论

本文提出了一种电流缓冲技术的嵌入式结构,利用嵌入式电流缓冲电路对反馈系统进行环路补偿,在消除传统电流缓冲带来的额外功耗的前提下,抑制了右半平面零点的产生,提高了环路的稳定性。将本文设计结果应用到低压差电源稳压器中,并采用联华电子公司0.5 μm 5 V的CMOS工艺生产出实际芯片,实测数据有力地验证了本文方法的有效性。

[1] 毕查德·拉扎维. 模拟CMOS集成电路设计 [M]. 西安: 西安交通大学出版社, 2003: 303-305.

[2] 张显库, 袁杨. 具有不稳定零极点对消的结构图等效问题 [J]. 计算技术与自动化, 2010, 29(3): 6-8. ZHANG Xianku, YUAN Yang. Problem of block diagram algebra with unstable pole-zero cancellation [J]. Computing Technology and Automation, 2010, 29(3): 6-8.

[3] BLAKIEWICZ G. Output-capacitor less low-dropout regulator using a cascoded flipped voltage follower [J]. IET Circuits Devices & Systems, 2011, 5(5): 418-423.

[4] AHUJA B K. An improved frequency compensation technique for CMOS operational amplifiers [J]. IEEE Journal of Solid-State Circuits, 1983, 18(6): 629-633.

[5] RAJPUT S K, HEMANT B K. Two-stage high gain low power OpAmp with current buffer compensation [C]∥Proceedings of 2013 Global High Tech Congress on Electronics. Piscataway, NJ, USA: IEEE, 2013: 121-124.

[6] ZABRODA O, MURMANN B. Eliminating complex conjugate poles in two-stage operational amplifiers with current buffer Miller compensation [J]. Analog Integration Circuit Signal Process, 2014, 81(2): 361-365.

[7] WANG Wei, YAN Zushu, MAK P I. Micropower two-stage amplifier employing recycling current-buffer Miller compensation [C]∥Proceedings of 2014 IEEE International Symposium on Circuits and Systems. Piscataway, NJ, USA: IEEE, 2014: 1889-1892.

[8] 陈颖玉, 郑金棋, 王慧贞. 一种新型大功率无损缓冲Buck变换器的研究 [J]. 电力电子技术, 2015, 49(6): 94-98. CHEN Yingyu, ZHENG Jinqi, WANG Huizhen. Research on a novel high-power buck converter using loss-less snubber [J]. Power Electronics, 2015, 49(6): 94-98.

[9] SANSEN W M C. Analog design essentials [M]. Berlin, Germany: Springer Inc., 2006: 102-105.

[10]GRAY P R, MEYER R G. MOS operational amplifier design: a tutorial overview [J]. IEEE Journal of Solid-State Circuits, 1982, 17(6): 969-982.

[11]GARIMELLA A, FURTH P M, SURKANTI P R. Current buffer compensation topologies for LDOs with improved transient performance [J]. Analog Integrated Circuits and Signal Processing, 2012, 73(1): 131-142.

[12]AL-SHYOUKH M, LEE H, PEREZ R. A transient-enhanced low-quiescent current low-dropout regulator with buffer impedance attenuation [J]. IEEE Journal of Solid-State Circuits, 2007, 42(8): 1732-1742.

[13]BRIAN M K. Understanding the load-transient response of LDOs [J]. Analog Applications Journal, 2000(9): 19-23.

[14]YEONG T L, CHI C U, MEI C J. A low dropout regulator using current buffer compensation technique [C]∥Proceedings of 2010 International Conference on Solid-State and Integrated Circuit Technology. Piscataway, NJ, USA: IEEE, 2010: 144-146.

(编辑 刘杨)

A Loop Compensation Method of Low Dropout Regulator with Ultra Low Power

LIU Chen1,2,LAI Xinquan1,ZHONG Longjie1,YANG Wei1

(1. Institute of Electronic CAD, Xidian University, Xi’an 710071, China; 2. School of Air and Missile Defense, AFEU, Xi’an 710051, China)

An embedded loop compensation method of LDO is proposed to solve the problem that the current buffer technique overcomes the drawback of traditional miller compensation, but consumes extra power. It merges the current buffer into the fold-back amplifier, so that the LDO circuit and the current buffer circuit share the transistor, and the loop stability of the circuit can be improved without adding the components. The principle of the proposed compensation method is analyzed and described in detail. The method is tested in a low-dropout voltage regulator using UMC 0.5 μm 5 V CMOS technology, and the results show that chip static power current has only 50 μA, and both the output voltage overshoot and undershoot are below 15 mV when the input voltage changes from 3 V to 5 V. The maximum change of the output voltage is less than 20 mV when the load resistance reduces from 18 kΩ to 9 Ω. The measurement results show that the embedded structure eliminates the extra power loss and improves loop stability.

IC design; loop compensation; embedded structure; current buffer technique

2015-06-03。 作者简介:刘晨(1977—),男,博士生;来新泉(通信作者),男,教授,博士生导师。 基金项目:国家自然科学基金资助项目(61106026);中央高校基本科研业务费资助项目(JB150222)。

时间:2015-11-05

网络出版地址:http:∥www.cnki.net/kcms/detail/61.1069.T.20151105.1950.002.html

10.7652/xjtuxb201601021

TN911.7

A

0253-987X(2016)01-0139-06