基于FPGA的同步计数器的优化结构分析*

2016-11-26钟强刘鹏飞刘宝军胡宗进秦绪栋

钟强,刘鹏飞,刘宝军,胡宗进,秦绪栋

(烟台大学,烟台 264005)

基于FPGA的同步计数器的优化结构分析*

钟强,刘鹏飞,刘宝军,胡宗进,秦绪栋

(烟台大学,烟台264005)

在数字信号处理中,同步计数器是一种非常重要的器件,在很多场所会用到。在基于现场可编程门阵列(FPGA)器件的开发过程中,人们往往不会注意所用到的同步计数器内部的具体设计。本文从资源利用率和速率两个方面,对FPGA开发综合工具自动综合出来的同步计数器进行分析,并且提出一种结构优化的同步计数器,并将两种同步计数器进行对比,得出了两者的优缺点及适用的场合。

同步计数器;FPGA;资源利用率;速率

引 言

计数是一种最简单基本的运算,计数器就是实现这种运算的逻辑电路,计数器在数字电路系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能[1]。在FPGA设计中,同步计数器无处不在,往往被大量的应用。作为最基本的逻辑电路,计数器的性能直接影响整体电路的性能,甚至会决定项目的成败。

在FPGA设计中,同步计数器的设计有多种方法,可以自己设计,也可以用Quartus软件的综合工具自动综合出来。本文主要从资源和速率两方面对软件自动综合出来的同步计数器进行分析,并在此基础上提出一种优化的同步计数器,可以更好地应用到FPGA设计中去。

1 同步计数器的基本原理

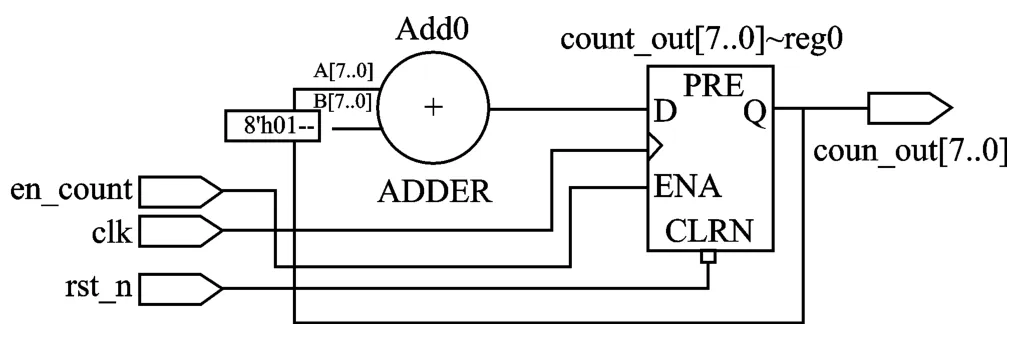

简单来说,计数器就是为了计数,是为某些问题提供一种计量单位,正是因为有了数目的区分,一切才会显得更加有条理[2]。在数字电路中,计数器主要是记录脉冲的个数,每到来一个脉冲,计数器的数值就会加1,当计数器计满时,就会归零重新计数,同时输出一个进位信号,如图1所示。

图1 同步加法计数器

计数器有同步和异步之分,简单来说,当脉冲到来时,要更新的所有触发器同时反转的计数器是同步计数器,而要更新的触发器有的先翻转,有的后翻转,这就是异步计数器[3]。本文主要介绍在FPGA中应用最广泛的同步触发器。

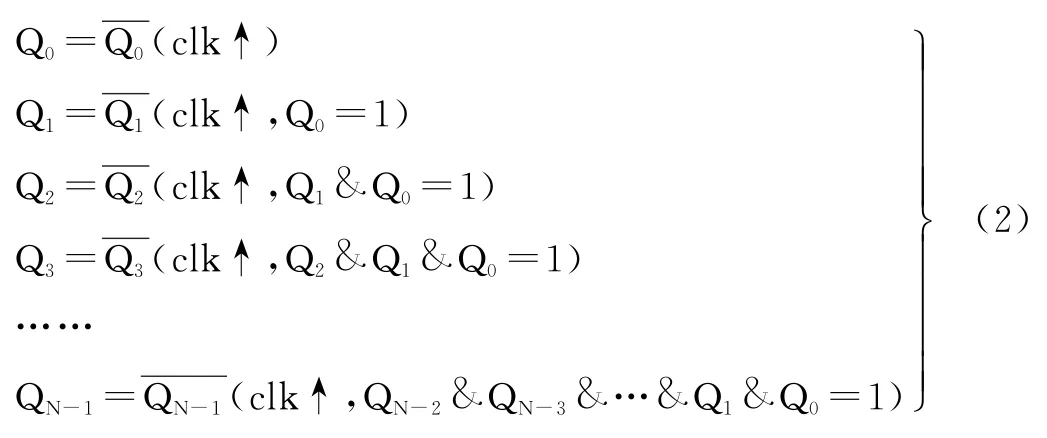

首先介绍一下N位的同步计数器的数学模型,如下所示:

式中,QN表示计数器的每一位输出值,所有的QN组成了整个计数器的输出值count。每一位QN满足式(2)所示的关系,clk指的是计数脉冲,在FPGA中往往是时钟的上升沿或者下降沿是QN的取反操作,当满足括号内的条件时,就会执行。

在FPGA设计中,计数器往往需要加上使能功能来控制其是否工作,使能输入E的每一位和计数器的输出QN满足如下关系:

把式(2)和式(3)合到一起,可以得到带有使能功能的计数器模型,如式(4)所示,这就是同步计数器的基本原理。

2 基于FPGA自动综合的同步计数器

FPGA器件由于其灵活的现场可编辑性,被广泛应用于各种数字信号处理的场所。FPGA的开发语言有两种, Verilog和VHDL各有千秋,从简单易懂、方便上手的角度出发,人们往往选用Verilog语言。Veriog语言是一种硬件描述性语言,它是以文本形式来描述数字系统硬件结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能[5-6]。

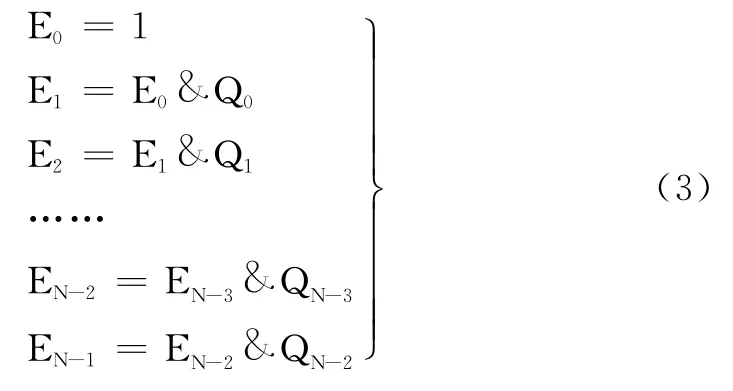

采用Veriog语言设计同步计数器时,仅仅从功能上来描述和设计该模块,然后FPGA的编程软件(例如Quartus)会自动综合,其内部的电路组成往往不去关注。而计数器的设计有很多方法,不同的设计会直接影响计数器的性能。

图2是仅仅从功能上出发,利用Verilog语言编写的8位同步计数器,从图中可以看出,count_out是计数器的输出,当计数器使能,即en_count的值为1的时候,每到来一个上升沿,count_out的值就会加1,这就实现了计数的功能。

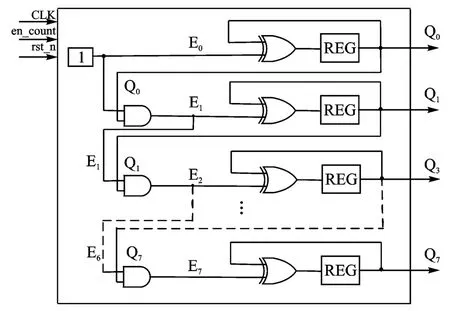

利用Quartus软件可以得到图3所示的算法顶层的RTL视图,但该图还是无法看出电路的内部结构。进一步深入分析,可以得到具体的门级别的电路设计。在Quartus软件中,门级的电路视图过于庞杂,不利于直观分析,稍加工后得到图4。

图4就是要分析的FPGA工具自动综合出的同步计数器门级电路图,从图中可以看出,它采用的是串行进位的设计方法。串行的进位设计,用到的仅仅是两输入的与门,比较简单,容易实现。但是串行的进位方式,产生进位信号的时间较长,需要从低位到高位逐级传送,花费时间较长。

图2 同步计数器的Verilog语言设计

图3 同步计数器的顶层RTL视图

图4 同步计数器的门级电路图

在FPGA设计中,数据运算的速率是比较看重的一个指标,速率越快,意味着延时越短,对数据进行实时处理的能力就越好。在图4的基础上进行改进,提出一种并行进位的设计方法,可以进一步提高运算速率。

3 同步计数器的优化设计

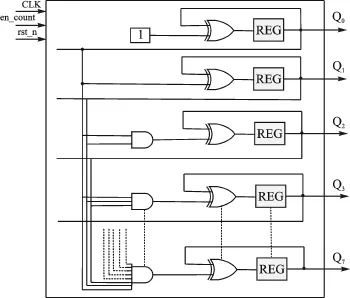

在第2节中,分析了基于串行进位设计的同步计数器延时较长,进而提出一种并行进位设计的同步计数器,如图5所示。

图5 优化后的同步计数器的门级电路图

在图5中,电路进位采用并行进位的方式,进位信号不需要再逐级传送,这样产生进位信号的时间就会缩短,延迟就会大大缩小。但同时也可以看出,并行进位的方式所需要的与门不仅仅是两输入的,随着计数器位数的增加,所用到的与门的输入端也随之增加,这无形中加剧了对资源的消耗。

4 实验仿真及数据分析

实验用的FPGA芯片采用Altera公司的Cyclone IV E系列中的EP4CE115F29C7,该芯片逻辑资源丰富,运行时钟速度快,广泛地应用于数字信号处理方面。系统编译软件采用Altera公司的Quartus II软件,该软件是Altera公司的综合性PLD/FPGA开发软件,支持原理图、VHDL、Verilog HDL以及AHDL(Altera Hardware Description Language)等多种设计输入形式[7-9]。系统仿真工具选用ModelSim软件,该软件属于Altera公司自主开发、专门用于FPGA器件的功能仿真,能直观地看出器件对数据处理后的结果。

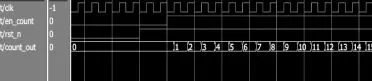

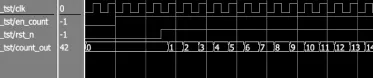

首先对两种同步计数器的算法进行ModelSim软件仿真,仿真结果如图6、图7所示。

图6 未优化的同步计数器仿真图

从图6和图7中可以看出,两个图的仿真结果完全一致,在使能端使能(即en_count=1)之后,每当有上升沿到来时,计数器就会加1,这就说明优化后的算法正确,可以实现计数的功能。

图7 优化后的同步计数器仿真图

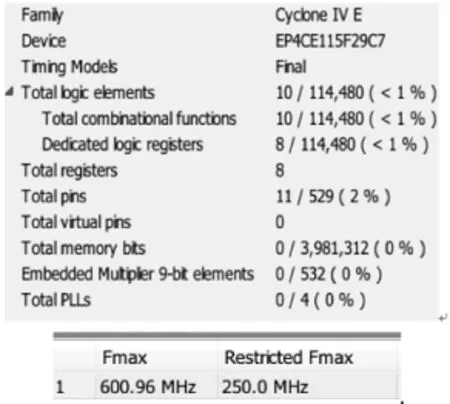

然后通过Quartus II软件查看两种设计方法所消耗的资源和速率,图8是未优化的同步计数器所消耗的资源及运行过程中的最高速率,图9是优化后的同步计数器所消耗的资源及运行过程中的最高速率。

图8 未优化的同步计数器资源及速率

图9 优化后的同步计数器仿真图

Altera公司的FPGA器件的可编程逻辑资源来自于逻辑阵列块(LAB),而每个LAB是由多个逻辑宏单元LE (logic elements)组成[10]。LE作为最基本的可编程单元,它的使用量代表了所设计算法的资源消耗程度。

从图8和图9中可以看出,未优化的同步计数器消耗了8个LE,优化之后消耗了10个LE,优化后的同步计数器比未优化的多使用了25%的资源,这是因为并行进位的方式比串行进位的方式更加复杂。从运行速率

30

Optimization Structure Analysis of Synchronous Counter Based on FPGA

Zhong Qiang,Liu Pengfei,Liu Baojun,Hu Zongjin,Qin Xudong

(Yantai University,Yantai 264005,China)

In the digital signal processing,the synchronous counter is a very important device,it is used in many fields.In the development of FPGA,the inside specific design of the synchronous counter is not paid attention to.In this paper,the synchronous counter of the automatic synthesis of FPGA development tools is analyzed in two aspects of the resource utilization and the rate,and a kind of synchronous counter with optimized structure is proposed.Finally,the two kinds of synchronous counter are compared,and the advantages and disadvantages are obtained.

synchronous counter;FPGA;resource utilization ratio;rate

TN79

A

烟台大学研究生科技创新基金(基金编号:YDYB1615)。