Zynq平台的TTP/C总线控制器同步算法设计

2016-11-26陈飞张天宏张文豪

陈飞,张天宏,张文豪

(南京航空航天大学 江苏省航空动力系统重点实验室,南京 210016)

Zynq平台的TTP/C总线控制器同步算法设计

陈飞,张天宏,张文豪

(南京航空航天大学江苏省航空动力系统重点实验室,南京210016)

为了保证TTP/C集群内各个节点之间时钟基准的一致性,设计了一种基于Welch-lynch中值增量修正法的时钟同步算法,充分利用了Zynq芯片的可编程逻辑单元和程序处理单元,在自主设计的TTP/C总线控制器上对时钟同步算法进行实验。实验表明,所设计的时钟同步算法能够保证各个测试节点的时钟同步误差在±30μs范围内。

时钟同步;Zynq;TTP/C;Welch-lynch

引 言

由欧洲委员会资助开发的分布式实时容错系统TTA (Time-Triggered Architecture,时间触发构架),不仅解决了以往事件触发方式因随机发送数据引起的可预测性低的问题,而且很好地解决了多任务数据传输时存在的通信延迟和时间偏移不确定等问题。1993年,在TTA架构的基础上,TTP/C(Time-Triggered Protocol/Automotive Class C,时间触发协议C类标准)被首次提出,其是一种用于互联电子模块的、分布式容错实时系统的通信协议,主要的面向对象是航空航天领域[1]。与面向汽车电子领域的TTP/A协议相比,TTP/C协议规范在安全性、可用性和可组合性等方面具有更加严苛的要求,更符合分布式实时系统对数据总线的性能要求。

节点间统一的时钟基准是TTP/C集群正常运行的基本前提,但温度、电压的变化和晶振老化等因素会使时钟源的频率偏离标称值。此外,单粒子反转事件也可能会导致某个节点本地时钟发生突变[2-4]。这些因素都会引起集群失去同步、发生时间槽混叠,进而导致节点之间通信失败。为了保证TTP/C集群各个节点之间工作时钟的一致性,本文设计了一种基于Welch-Lynch中值增量修正法的同步算法,以此修正各节点的本地时间,实现各节点的全局时间准确可靠,保证时间触发集群的通信可靠性和实时性。

1 时钟同步算法的原理

目前,时钟同步算法有很多种,如区间时钟同步法、概率时钟同步法和Welch-Lynch时钟同步法等[2,4]。其中,基于中值平均值的Welch-Lynch同步算法具有良好的单节点容错功能且易于实现,本文采用此算法,下面对该方法进行详细介绍。

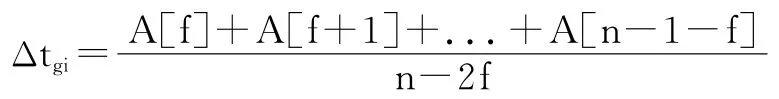

假设节点i在t时刻由TTP/C总线获得其他(n-1)个节点的本地时间pci(t),并在收到这些时间的时刻与节点i的本地时间作差得到(n-1)个时钟误差Δpcij(t)(1≤j ≤(n-1))。将这(n-1)个时钟误差使用冒泡法进行排序后,放到数组A[n-1]中,其中A[0]≤A[1]≤…≤A[n-2]。假设集群最多可容忍f个节点的故障,则节点i相对于全局时钟的误差为:

其中,为了保证能够容忍f个节点的故障,同步总节点数n≥(3f+1)。根据TTP/C协议的单节点故障要求,同步算法只能容忍单节点故障,当节点数少于4时,该算法不再具有同步能力[2,4]。

2 时钟同步算法的实现

基于Welch-lynch时钟同步法,本文利用Zynq的可编程逻辑单元实现TTP/C总线控制器各节点的时钟同步需求[5],如图1所示。1 MHz信号发生器利用100 MHz的时钟输入信号,依据时钟同步算法模块提供的临时分频系数计算产生标准1 MHz的时钟信号,供本地时钟计数器产生本地时钟。

图1 时钟同步模块架构图

Welch-lynch算法只是在理论上给出了一种计算节点本地时钟和全局时钟误差的方法,在具体实现时,还需要根据这个误差对节点的本地时钟进行校正。本文设计了一个临时分频系数,在100 MHz时钟驱动下,对本地时钟计算的标准1 MHz时钟脉冲进行修正,如图2所示。当不存在时间误差时,临时分频系数为100,1 MHz信号发生器在100 MHz时钟驱动下计数100次产生1个脉冲信号;当本地时钟比全局时钟快时,临时分频系数增大,1 MHz信号发生器产生的1 MHz时钟变慢,本地时钟与全局时钟的误差将会减小,直到不存在误差;反之临时分频系数减小,误差降低。

图2 标准脉冲频率修正原理

因此临时分频系数的产生对时钟同步的效果至关重要,时钟误差计算模块的工作原理如图3所示。

当(n-1)个时钟误差计算结束时,使能冒泡排序功能,将时钟误差数组进行升序排列,然后采用Welch-lynch算法计算时钟误差,并产生临时分频系数,对本地时钟进行校正。需要注意的是,受到时序的限制,冒泡排序法不能在一个时钟周期内完成,需要经过多个时钟周期分步实现。针对4个节点时的冒泡排序程序代码如下:

图3 时钟误差计算模块工作原理

3 时钟同步算法的验证

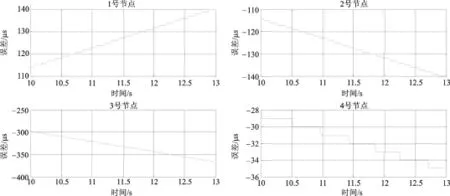

针对所设计的时钟同步算法,本文设计了一个包含上位机和4个测试节点的验证平台。在实验测试时,通过上位机界面对比集群中各个节点在未使用同步算法和使用同步算法的本地时钟和全局时钟的误差,来证明本文设计的同步时钟算法的有效性,图4为未使用同步算法时各个节点的工作状态,图5为使用本文所设计的同步算法后各个节点的工作状态。

图4 未使用同步算法的同步误差测试界面

图5 添加同步算法的时钟误差

图4中集群运行约13 min后,各个节点的本地时钟与全局时钟误差一直增大。由于各个节点误差值不同,所以图中各个节点的Y轴范围也不同。为了能够更直观地看出变化趋势,在表1中给出了和图4对应时间段每隔10 s的同步误差。由图4和表1可以得出以下结论:

①在不添加同步算法的条件下,随着时间的推移,本地时钟与全局时钟的误差随着时间的推移逐渐增大,这在一定程度上也体现了各个节点之间的本地时钟误差在逐渐增大;

②各个节点相对全局时钟误差正负和大小均不同,这是由于各个节点所使用的时钟晶振的稳定度不同而造成的;

③对比向负方向偏移量最大的节点3和向正方向偏移量最大的节点1可知,在150 s内,两个节点的时钟偏差最大可达:

(140-114)+(366-298)=94μs

则单位时间的最大偏差量为:

表1 每隔10 s各个节点的同步误差(单位:μs)

43

Synchronization Algorithm for TTP/C Bus Controller Based on Zynq

Chen Fei,Zhang Tianhong,Zhang Wenhao

(Jiangsu Province Key Laboratory of Aerospace Power System,Nanjing University of Aeronautics and Astronautics,Nanjing 210016,China)

A clock synchronization algorithm based on Welch-lynch is designed to ensure that the clock error between each node in the TTP/C cluster is within the range of requirements.The clock synchronization algorithm is tested on the TTP/C bus controller which is developed on the program and logic processing units of Zynq chip.The experiment results show that the clock error between each node is within±30μs,and the clock synchronization algorithm is effective.

clock synchronization;Zynq;TTP/C;Welch-lynch

V233.7

A