32位低功耗高速乘法器设计❋

2016-11-21张明英

张明英

(西安外事学院,西安710077)

32位低功耗高速乘法器设计❋

张明英

(西安外事学院,西安710077)

采用Verilog HDL硬件描述语言,设计了一个高性能、低功耗的32位定点乘法器。该乘法器通过对基4布斯算法、4∶2压缩器算法及最终加法器的优化设计,进一步提高了乘法的运算速度。另外,在设计中加入了操作数隔离、门控时钟等低功耗设计技术,从而大幅度减少了电路功耗。采用SMIC 0.18μm CMOS工艺,使用Synopsys的Design Compiler工具对电路进行逻辑综合。结果显示,最坏情况下的时间延迟为3.9ns,系统时钟频率可达256MHz,功耗小于37mW。

低功耗;高速乘法器;基4布斯算法;操作数隔离;门控时钟;CMOS工艺

1 引 言

乘法器是微处理器的核心部件之一,也是数字信号处理领域的基本单元。乘法运算的性能好坏直接关系到整个系统的性能。本设计主要从速度和功耗两个方面对乘法器进行了优化设计。在速度方面通过改进算法来改善运算速度;在功耗方面通过分析功耗产生的原因对其进行改善,有针对性的加入门控时钟等低功耗设计方法,最终使电路功耗大幅度降低。

2 低功耗高速乘法器设计

2.1低功耗设计

集成电路中的功耗损失主要由静态功耗和动态功耗两部分构成。其中,静态功耗主要是由亚阈值泄露电流所引起的功耗和由栅极泄露所引起的功耗;动态功耗包括晶体管翻转时,电源和地间瞬时短路所引起的功耗和电路工作时对负载充放电所消耗的功耗。整个集成电路的功耗为:

静态功耗与集成电路工艺有关,很难在设计中改变。在该乘法器设计中主要是想方设法降低电路的动态功耗。采用降低动态功耗的方法主要包括:

(1)门控时钟

一般情况下时钟信号(clk)直接接入电路中,只要clk发生变化,整个电路就会不断运转。设计中增加了门控时钟后,情况则会不同,当电路正常工作时,时钟门控使能信号为高,时钟正常翻转;当电路处于空闲状态时,时钟门控使能信号置低,这时候输入电路的clk一直为零,电路不再运行,电路将进入低功耗模式。所设计的门控时钟电路如图1所示,该电路由一个负锁存器和一个与门实现。

图1 门控时钟电路

电路工作原理为:负锁存器在clk为低时透明传输,en1信号上的毛刺仅出现在clk的低电平处,与clk进行与操作,可以将这部分毛刺消除掉。这样,gclk上就没有毛刺了。该电路输出的时钟gclk将接入电路中替代clk,当en为高电平时,电路正常工作;当en为低电平时gclk也为0,电路处于低功耗状态,这样就能极大减少电路的动态功耗。

(2)隔离操作数

采用隔离操作数的方法来降低功耗,其主要原理是在不进行乘法运算的时候,将这些模块的输入置0,不输入数据,输出结果不会发生变化;如果进行乘法运算时,再将输入端口打开。这种方法会对系统的动态功耗有较大改进,在芯片面积方面所增加的逻辑仅仅是几个多路选择器。

(3)状态编码优化

状态编码优化方法主要对电路中的状态机所产生的功耗进行优化,目的在于通过减小两个相邻状态之间的加权平均距离来减小开关活动性(状态转换时不变的比特位数)。选取编码的原则是:对于频繁切换的相邻状态,尽量采用相邻编码。例如,Gray码在任何两个连续的编码之间只有一位数值不同,在设计计数器时使用Gray码取代二进制码,可显著降低功耗。

2.2电路设计

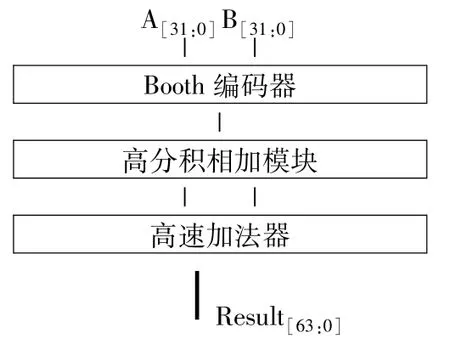

设计的低功耗高速乘法器的硬件框图如图2所示,该电路主要由Booth编码模块、部分积相加模块和高速宽位加法器模块组成。

图2 32位定点乘法器结构

2.2.1基4布斯编码模块

布斯编码是A.D.Booth在1951年提出的一种补码相乘算法,可以将符号位与数值位合并在一起参与运算,直接得出用补码表示的乘积,且正数和负数同等对待。传统的布斯算法以2为基,形成N项编码项、乘积项。为了提高运算速度,这里采用基4布斯算法,该算法可减少近一半的乘法乘积项,从而大大提高运算速度。该算法的原理如下所示。

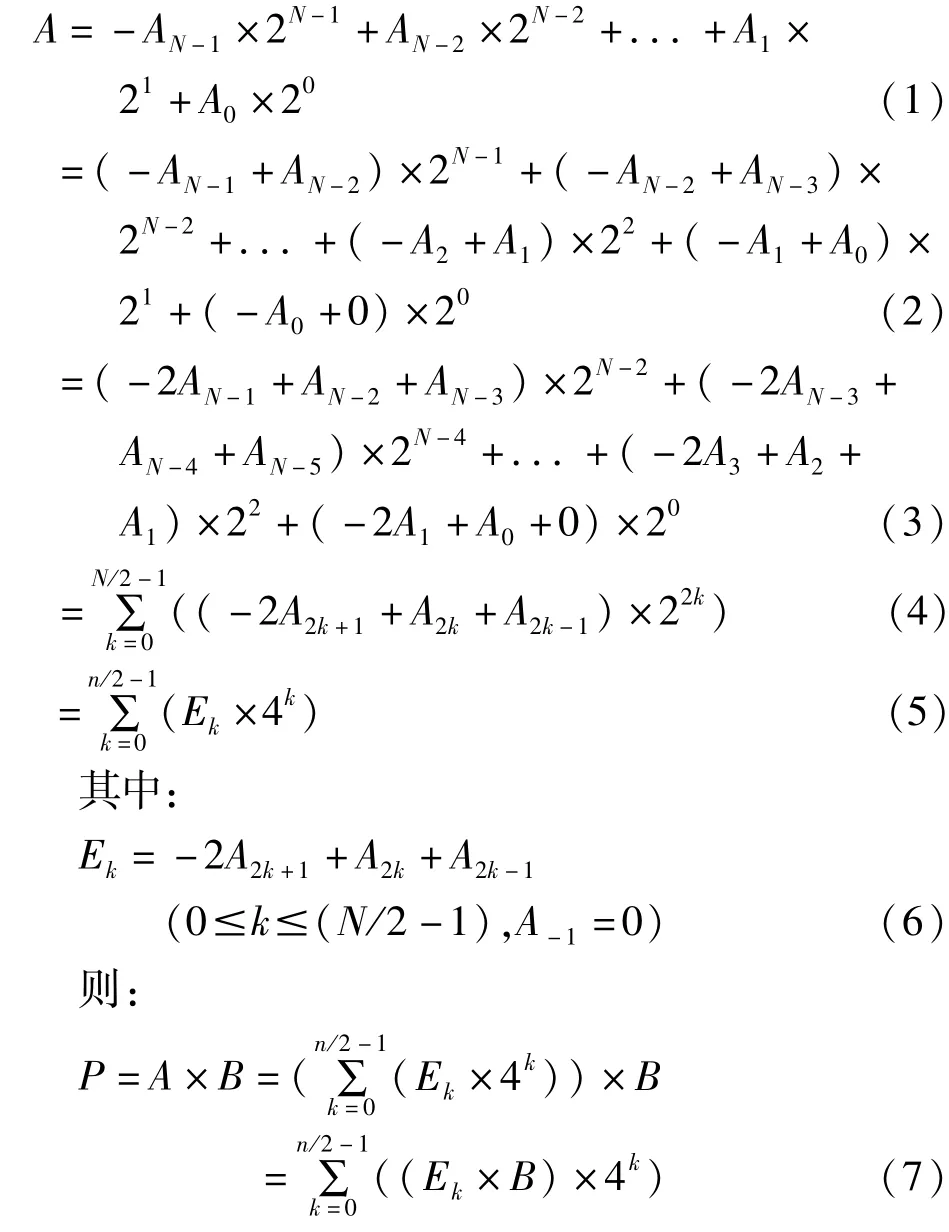

两个N(N为偶数)位补码表示的符号数相乘A×B,那么乘数A可表示为:

此即符号数的基4布斯算法,基4布斯编码一次考虑了三位:本位、相邻高位、相邻低位;处理了两位,形成(N/2)项编码项、乘积项,从而大大减少了运算量。对于无符号数,可将其高位作0扩展(扩展后位数也必须为偶数),并无影响。

2.2.2部分积相加电路

为了能够同时处理符号数和无符号数,需要将32位宽度扩展为34位宽度,从而由布斯编码器可得17个乘积项。由于乘积项有为负的,运算时需要进行取补运算,如果用一独立的取补逻辑会给电路带来额外的延迟和功耗。这里将取补逻辑中的加1运算,作为进位来处理,这样做可以有效减小电路延迟,当前一乘积项为负时,CC取值为01,否则为00。各乘积项要以权值对齐,各进位也要以权值对齐,新构成的乘积项阵列如下所示。

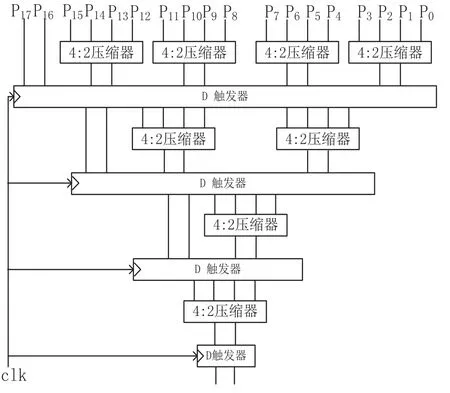

乘积项阵列已得到,还要将此阵列转换为最终结果,这就用到加法器阵列。最简单的方法是采用串行累加,但由于运算是串行的,延迟会比较大,需要17级加法器延迟。这里采用如图3所示的流水线结构。该结构采用并行操作,全部采用4∶2压缩器完成运算,布局规整,使执行层次降低为log2N,从而大大减小了电路延迟。

图3 压缩器构成的华莱士树流水线结构

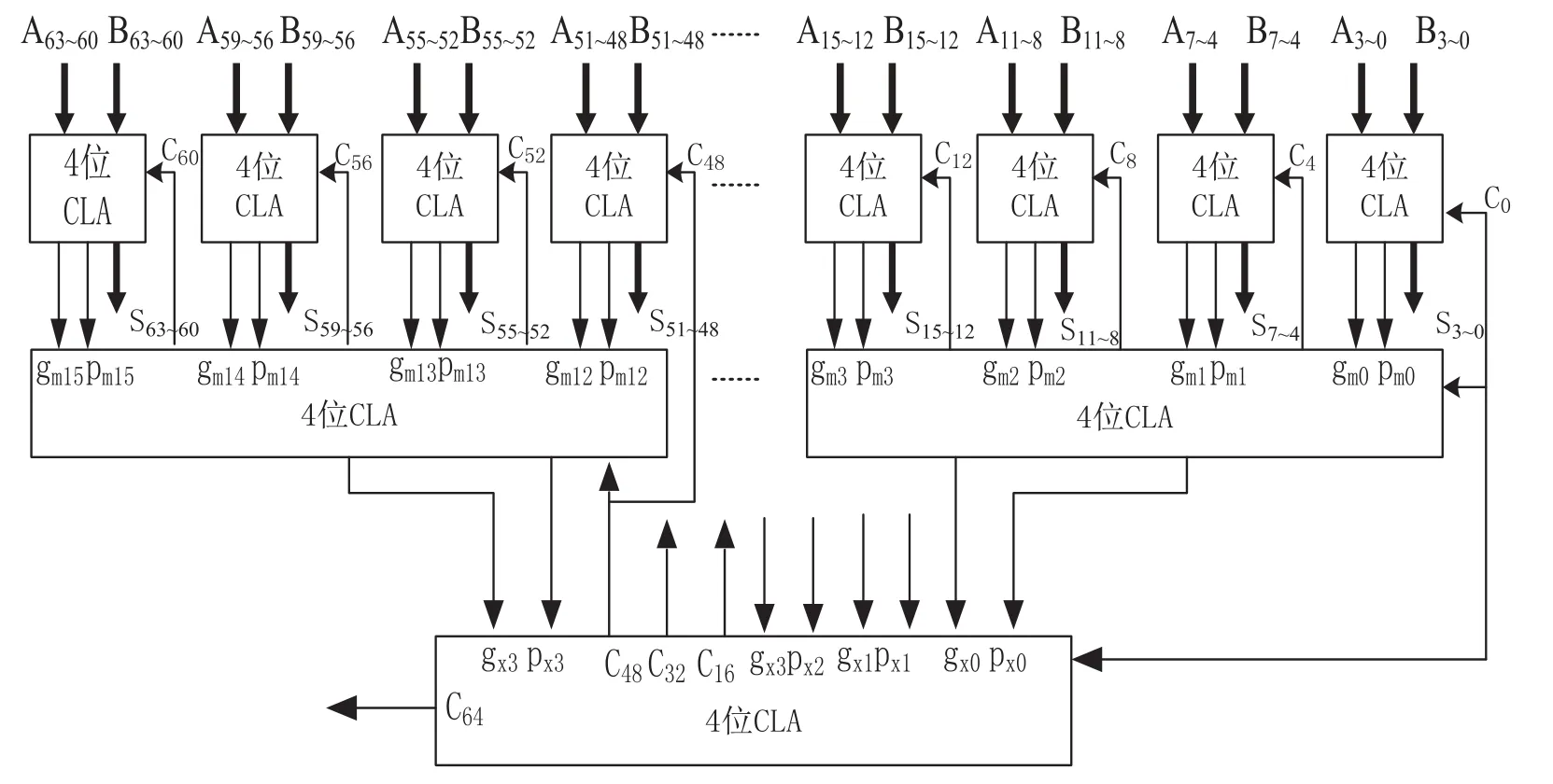

2.2.3高速宽位加法器设计

经华莱士树输出的两路64位数据相加后才能得到最终结果。本设计的64位加法器采用三级超前进位实现,如图4所示。该方法组内和组间都采用先行进位方式,其延迟和加法器的位数没有太大关系,不会随着位数的增加而延长时间。

图4 64位高速加法器结构

3 电路性能

根据系统设计要求,整个电路采用SMIC 0.18μm CMOS工艺实现,利用Modelsim软件对整个乘法器电路进行仿真,综合工具是Design compiler,功耗分析工具是PowerCompiler。Modelsim仿真结果如图5所示,clk为该乘法器的时钟,rst_n为复位信号。opdata1为被乘数,opdata2为乘数,result1为采用组合逻辑实现的输出结果,result2为采用流水线实现输出的结果,result3为理论计算结果。从仿真结果可以看出所设计电路的计算结果与理论计算结果一致,电路实现了正确功能,区别在于流水线结构的结果需要等待5个时钟周期才能输出。另外我们使用Synopsys的Design Compiler工具对流水线结构实现电路进行逻辑综合,最坏情况下的时间延迟为3.9ns,系统时钟频率可达256MHz,功耗小于37mw,与文献[2-3,5-6]所设计电路相比,速度有了较大提高。

图5 乘法器仿真结果

4 结束语

该设计对32bits定点乘法器各级电路结构进行了优化,与其他文献中设计方法相比,减少了乘法器各级的延迟和功耗。电路采用SMIC 0.18μm CMOS工艺实现,从设计结果可以看出:①与传统乘法器相比,大幅提高乘法器运算速度,其最大时钟频率可达256MHz;②与不加低功耗设计技术的乘法器电路相比,加入低功耗设计技术后大幅度降低了电路功耗。设计中全部采用4∶2压缩器实现新型Wallace树结构,设计规则、对称性好,易于ASIC实现。设计思想不仅可以在高速低功耗乘法器设计中能够提升电路性能,而且可以将这种设计加入其它硬件电路中,对系统性能都会有极大提升。

[1]周怡,李树国.一种改进的基4-Booth编码流水线大数乘法器设计[J].微电子学与计算机,2014,31(1):60-63.Zhou Yi,Li Shuguo.Design of pipeline large integer multiplier based on an implementation of radix-4 modified booth encoding[J].MICROELECTRONICS&COMPUTER,2014,31(1):60-63.

[2]翟召岳,韩志刚.基于Booth算法的32位流水线型乘法器设计[J].微电子学与计算机,2014,31(3):146-149.Zhai Zhaoyue,Han Zhigang.32 bit pipeline multiplier design based on booth encoder[J].MICROELECTRONICS&COMPUTER,2014,31(3):146-149.

[3]姚若河,徐新才.基于冗余符号数的定点乘法器的设计[J].华南理工大学学报(自然科学版),2014,42(3):27-34.Yao Ruohe,Xu Xincai.Design of a fixed-point multiplier based on redundant signed digit[J].Journal of South China University of Technology(Natural Science Edition),2014,42(3):27-34.

[4]李飞雄,蒋林.一种结构新颖的流水线Booth乘法器设计[J].电子科技,2013,26(8):46-48,67.Li Feixiong,Jiang Lin.A novel structure of the pipelined booth multiplier[J].Electronic Sci.&Tech.,2013,26(8):46-48,67.

[5]李军强,李东生,李奕磊,等.32×32高速乘法器的设计与实现[J].微电子学与计算机,2009,26(12):23-26,30.Li Junqiang,Li Dongsheng,Li Yilei,et al.32×32 Highspeed multiplier design and implemetation[J].MICROELECTRONICS&COMPUTER,2009,26(12):23-26,30.

[6]周婉婷,李磊.基4Booth编码的高速32×32乘法器的设计与实现[J].电子科技大学学报,2008,37(增刊):106-108.Zhou Wanting,Li Lei.A high-speed 32×32b multiplier implementation using improved radix-4 booth coders[J].Journal of University of Electronic Science and Technology of China,2008,37(suppl):106-108.

[7]蒋勇,罗玉平,马晏,等.基于FPGA的32位并行乘法器的设计与实现[J].计算机工程,2005,31(23):222-224.Jiang Yong,Luo Yuping,Ma Yan,et al.Design and implemetation of 32-bit parallel multiplier using FPGA[J].Computer Engineering,2005,31(23):222-224.

[8]杜慧敏,李宥谋,赵全良.基于Verilog的FPGA设计基础[M].西安:电子科技大学出版社,2006.Du Huimin,Li Youmou,Zhao Quanliang.FPAG Design Based on Verilog[M].Xi'an:XIDIAN UNIVERSITY PRESS,2006.

Design on 32-bit High-speed Low-power Multiplier

Zhang Mingying

(Xi'an International University,Xi'an 710077,China)

Using Verilog HDL hardware description language,a design of low power and high speed 32-bit fixed-point multiplier is presented.The speed of the multiplier,by means of optimization the design of radix-4 booth algorithm,4∶2 compressor and the final wide bit adder,is improved.In addition,the power consumption of the circuit is significantly reduced by means of performing the design techniques of operand isolation,clock gating and other low-power.Based on SMIC's 0.18μm CMOS process model,the circuit is synthesized by Synopsys's Design Compiler tool.The result shows that the maximum delay can be reduced to 3.9ns,the frequency of the system can reach 256MHz and the power consumption is less than 37mW.

Low-power;High speed multiplier;Radix-4 algorithm;Operand isolation;Clockgating;CMOS process

10.3969/j.issn.1002-2279.2016.01.005

TN409

A

1002-2279(2016)01-0018-04

❋陕西省教育厅课题(2013JK1146)

张明英(1980-),女,山东省潍坊市人,硕士研究生,讲师,主研方向:集成电路系统设计。

2015-03-30