高精度D/A转换器设计技术研究

2016-11-21王鹏

王 鹏

(中国电子科技集团公司第四十七研究所,沈阳110032)

·大规模集成电路设计、制造与应用·

高精度D/A转换器设计技术研究

王鹏

(中国电子科技集团公司第四十七研究所,沈阳110032)

针对采用多晶电阻实现的基于R-2R网络的高精度电压输出型D/A转换器由于多晶电阻匹配精度和修调精确度低导致转换器精度很难保证的缺点,探讨了采用开关管导通电阻匹配技术,开关管分段匹配技术,分段阶梯结构电阻网络等几种设计技术来提高转换器精度的方法,采用以上技术再结合电阻修调及精细的版图设计方法,可以实现超过12bits精度的D/A转换器。

R-2R电阻网络;D/A转换器;MOS开关;导通电阻;匹配;分段阶梯结构

1 引 言

随着计算机技术、数字信号处理技术、通信技术、多媒体技术的发展,高精度、高压D/A转换器被广泛应用在进程监测和工业自动控制等各个场合,D/A转换器日益显出更加重要的地位。精度达到12位、转换速率超过100KHz的电压输出型D/A转换器已经得到了广泛应用,更高精度和速度的D/A转换器也在逐步为应用系统所采用。近二十年来,集成电路的工艺与技术得到了快速发展,数字电路发展更加迅速,部分原来需要采用模拟电路结构来实现的芯片,都可以用数字电路来实现了,但是D/A转换器电路作为连接数字电路和模拟电路的重要接口仍然需采用模拟电路结构。基于R-2R电阻网络架构的D/A转换器因其功耗、面积和精度之间具有良好的折中等优点为大多数电压输出型D/A转换器所采用。

2 电压型D/A转换器架构分析

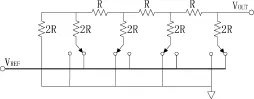

电压输出型D/A转换器的主体结构经常采用如图1所示的R-2R梯形电阻网络结合运算放大器作为输出缓冲器的架构。基于R-2R结构的D/A转换器是D/A转换器大家族中一个庞大的分支,这个结构使用的电阻个数少,要构成N位的数模转换器只需要3N个电阻,并且转换器的精度只与电阻的相对精度有关系,而与电阻的绝对精度无关。

基于R-2R结构电压模式的D/A转换器[1-2]通过将不同的数字代码输入控制开关管,把VOUT信号与参考电压VREF和地电位通过R-2R电阻网络连接起来,VOUT输出到后面的输出缓冲器中,这个输出缓冲器把输入的VOUT信号转换成最终的输出电压。如果将地电位替换成另一个负的参考电压,那么通过这种修改将可以使该结构实现双极性输出。

图1 电压模式R-2R梯形电阻网络DAC

通常构成R-2R电阻网络的电阻是稳定且十分精确并能进行校准的薄膜电阻,这种薄膜电阻的温度系数小于20ppm/℃,失配度能控制在0.005%以内。但现在通用的代工厂都无法提供这种高精度薄膜电阻加工技术,而采用多晶电阻替代方案的R-2R电阻网络由于多晶电阻匹配精度和修调精确度都远远低于薄膜电阻,转换器精度往往很难保证。因此,在现有工艺水平条件下需要采用一些电路优化设计技术来尽可能提高R-2R结构电压型D/A转换器的精度,满足设计目标。

3 D/A转换器电路设计技术

3.1开关管导通电阻匹配技术

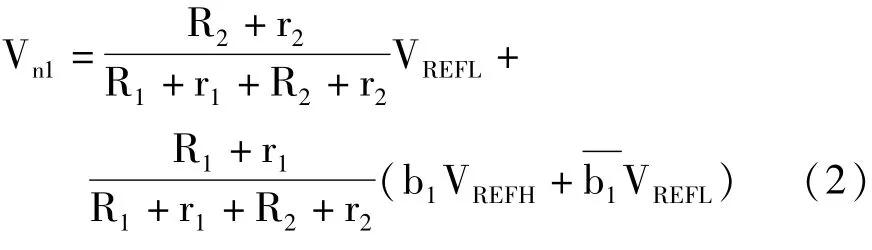

D/A转换器电路主体为一个如图1所示的R-2R开关电阻网络。对于一个基于R-2R网络的电压模式D/A转换器[3],其输出电压VOUT可以表示为式(1):

当考虑开关的导通电阻时,电阻网络的输出电压则会偏离以上的计算值,所以应当在开关电阻上予以补偿。但是在设计时精确计算和预计开关的导通电阻是困难的,因为没法控制工艺的变化,特别是开关和电阻相互独立,所以,用减小电阻值的方法补偿开关电阻是不可行的。通常可以采用开关间的相互匹配来解决这一问题。

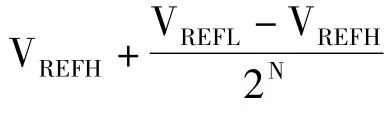

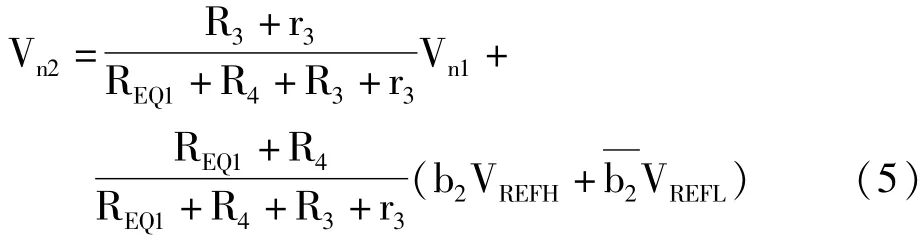

如图2所示,图中R1=R2=R3=2R,R4=R,开关导通电阻为rn且第一条支路开关始终接VREFL。对左边的两条支路作诺顿等效有:

图2 简化的包含开关电阻的D/A等效电路

对于理想的R-2R网络,希望:

求解式(2)和式(3)得r1=r2令r1=r2=r

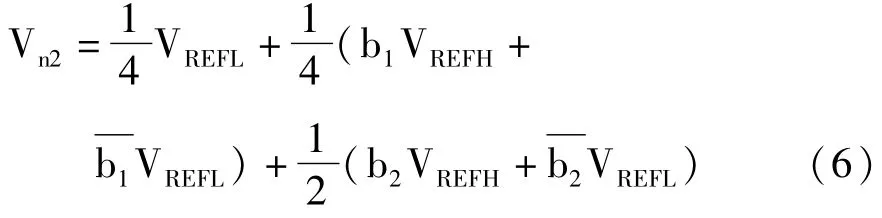

同理,求解Vn2的输出电压公式为:

同样对于理想的R-2R网络:

对式(4)、(5)及式(6)求解,得:

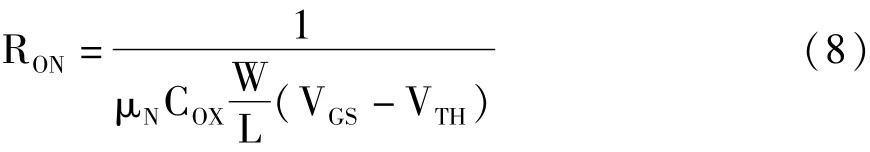

通过以上分析可知,为了抵消开关电阻对电阻网络精度和匹配的影响,可以将开关电阻按1/2比例缩小,而且开关电阻的电阻值和R-2R电阻网络的电阻值大小无关,所以对开关的导通电阻大小没有要求。对于MOS管,其导通电阻[4]为:

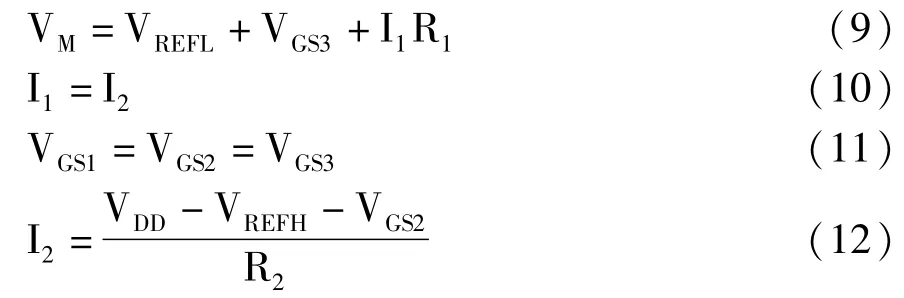

所以,要按比例缩小开关的导通电阻,可以在保持MOS管过驱动电压相同的情况下,按比例增加开关管的宽长比来实现。若选择电源电压VDD作为高参考电压VREFH端开关的栅电压,则此开关的过驱动电压为VDD-VREFH-VTH,为了使低参考电压端VREFL开关的过驱动电压与此相等而满足开关电阻按比例缩小的要求,需要一个特定的栅电压满足开关电阻按比例缩小的要求,这一个特定的栅电压VM可以用如下电路产生。

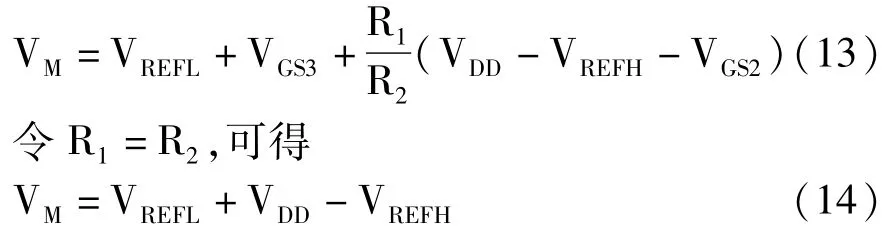

图中P1,P2,P3三个PMOS管宽长比相同且都工作在饱和区,由电路结构可得:

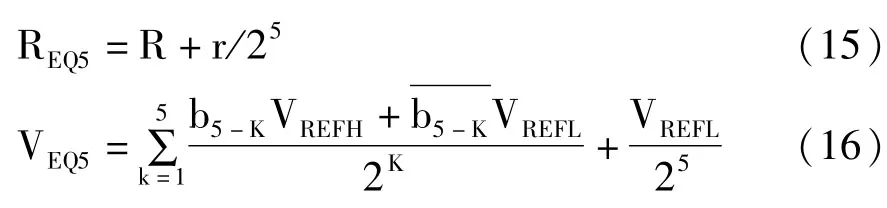

由式(9)-(12)可得:

图3 负参考源VREF-开关过驱动电压产生电路

由式(14)可得低参考电压端VREFL开关的过驱动电压也为VDD-VREFH-VTH,达到满足保持开关过驱动电压相同的要求。

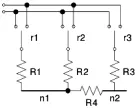

3.2开关管分段技术

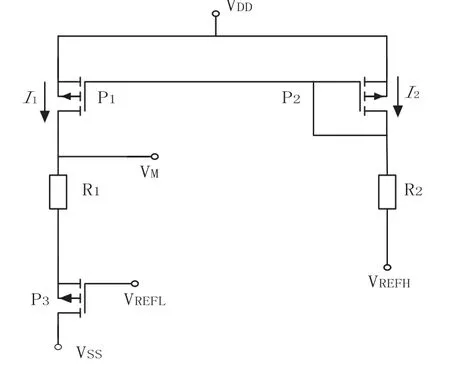

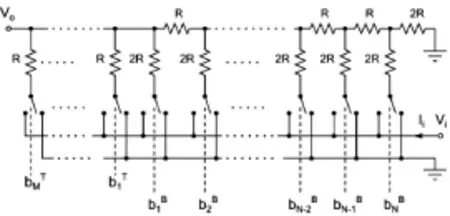

由3.1节分析可知,为了达到使开关导通电阻不影响R-2R电阻网络的性能,需要开关管在大范围内实现匹配。对于12位的D/A转换器,其最高位与最低位面积值比也是12位,即比值为212。如此大的差别,仅依靠改变MOS开关管宽度W的做法是不可取的,通常采用MOS管串联和并联相结合的方法。高位开关管的导通电阻靠改变MOS开关管的宽度W来实现,而低位则采用改变MOS开关管有效长度L的方法。但对于应用于高压工作(例如±15V电压),MOS开关管的最小长度L通常远大于特征尺寸,因此采用上述方法依然会有以下弊端:①最低位的开关管导通电阻过大,最高位导通电阻较小,因此失配较大,影响D/A转换器精度;②总体开关管的版图面积过大,增加了布局布线的难度,尤其是对于高压MOS开关管。为了解决上述问题,可以采用开关管导通电阻分段匹配技术[5-6],如图4所示。

图4 采用开关管分段的R-2R电阻网络

假设R-2R电阻网络按低5位和高7位进行分段,低5位的等效电阻为:

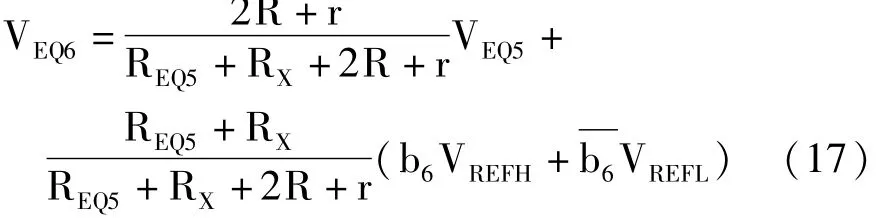

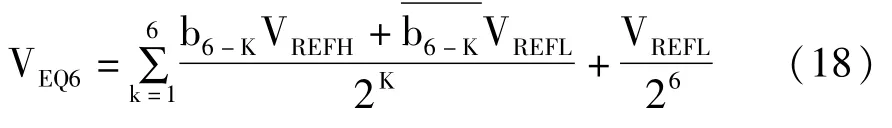

假设补偿开关的导通电阻为RX,且Bit6的开关导通电阻为r,则前六位的等效电压为:

对于理想不包含开关电阻的电阻网络前六位的等效电压为:

解式(15)-式(18)得到式(19):

3.3分段阶梯结构电阻网络

通常传统D/A转换器有R-2R阶梯结构和2NR结构两种典型架构,R-2R阶梯结构特点是速度快,但对电阻的匹配与温度特性要求很高,2NR阶梯结构非常简单,对电阻匹配要求也很低。但是,随着D/A转换器位数的增加,芯片面积也急剧增大,导致成本上升,并且,这种D/A转换器响应速度很慢,12位D/A转换器需要212个电阻,因此,该结构的设计只适用于低位数的DAC。

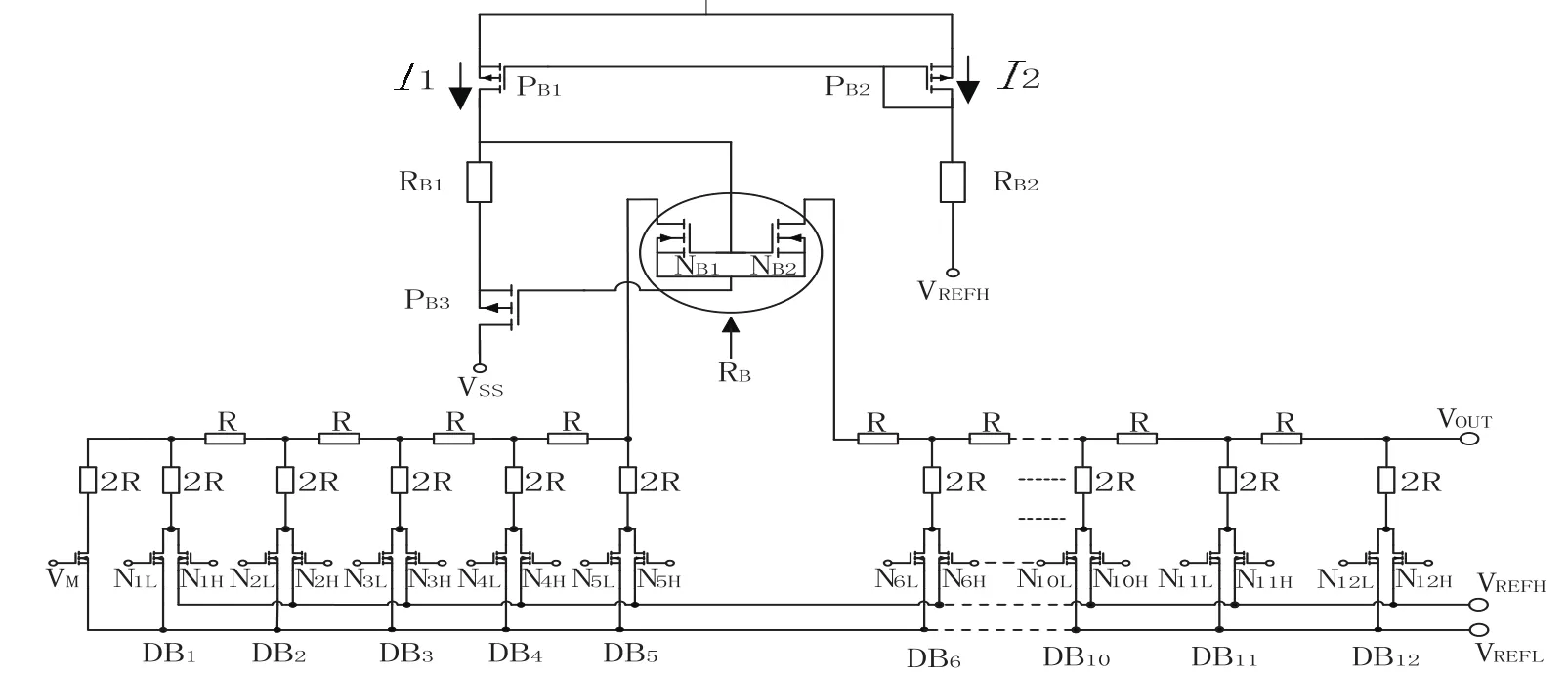

考虑如图1所示的标准R-2R电阻网络,会发现当输入码从011111…变为100000…(电压中值)的时候,梯形网络顶端2R的电流为1024LSB(等效电流),如果D/A转换器允许最大误差是1LSB(保证D/A转换器单调输出),对于12位的D/A转换器,则要求最高位的电阻匹配精度达到1/2048,即0.488%,对于采用多晶电阻实现的R-2R电阻网络达到如此高的匹配精度在版图及工艺上实现都是非常困难的。因此,为了降低电阻匹配要求同时又不占用太多的芯片面积,可以考虑采用R-2R结构与2NR结构相结合的分段阶梯结构D/A转换器[7-8],如图5所示。

图5 分段阶梯结构R-2R电阻网络

假设R-2R电阻网络的高4位采用基于温度计码译码的2NR电阻并联结构,则这4位有16种分段输入,每个分段控制128LSB的输出电流,这种分段能在器件精度要求较低的情况下获得很好的DNL值,对于采用4-8位分段的12位D/A转换器可以由8位的匹配精确设定一个12位转换器1/2LSB的DNL,同时这种分段技术可以有效减轻因D/A转换器输出变化而产生的瞬态脉冲面积。

分段阶梯结构中的关键是决定哪几位采用温度计码译码的电阻并联结构,最大程度地降低电阻匹配精度的要求,同时减小脉冲尖峰对D/A转换器的影响。很明显,使用电阻并联结构位数越多,对电阻匹配精度的要求越低,对尖峰脉冲的抑制效果越好,但电阻个数会呈2N指数增长,成本也急剧增加。因此,在选择电阻并联结构位数和版图面积上存在一个折中。同时应该注意这种分段结构虽然可以减小DNL误差,但是对D/A转换器INL的指标并没有什么改善。

4 结束语

针对采用多晶电阻实现的R-2R网络的高精度电压输出型D/A转换器由于多晶电阻匹配精度和修调精确度低而导致转换器精度难以保证的缺点,探讨了采用开关管导通电阻匹配技术,开关管分段匹配技术,分段阶梯结构电阻网络等几种设计技术来提高转换器精度的方法。通过采用以上技术并在版图设计中考虑加入冗余电阻单元,单元电阻串并联及电阻摆放位置中心对称等版图匹配方法和电阻网络修调算法,可有效降低电路对电阻匹配精度的要求,实现在一定的工艺条件下设计出精度更高、性能更好的D/A转换器。

[1]Walt Kester.Data Conversion Handbook[M].USA:ELSEVIER,2005.

[2]GUSTAVSSON M,WIKNER J J,TAN N N.CMOS Data Converter s for Communication[M].Boston:Kluwer Academic Publishers,2000.

[3]R.Jacob Baker.CMOS:MIXED-SIGNAL CIRCUIT DESIGN[M].USA:IEEE Press,2005.

[4]RAZAVI B.Design Of Analog CMOS Integrated Circuits[M].USA:Mc-Graw-Hill Press,2003.

[5]李娅,万辉.一种新颖的R-2R电阻网络[J].微电子学,2014,44(6):727-730.Li Ya,Wan Hui.A New R-2R Resistor Network[J].Microelectronics,2014,44(6):727-730.

[6]D Marche,Y Savaria.An improved switch compensation technique for inverted ladder DACs[J].IEEE Trans.Cir and Sys I:Reg.Papers,2009(6):1115-1124.

[7]马烨,李斌.一种高精度低成本10位D/A转换器的设计与实现[J].微电子学,2011,41(2):189-193.>Ma Ye,Li Bin.Design and Implementation of a High Precision and Low Cost 10Bit Digital to Analog Converter[J].Microelectronics,2011,41(2):189-193.

[8]D Marche,Y Savaria.Modeling R-2R Segmented-Ladder DACs[J].IEEE Trans Cir and Sys I:Reg Papers,2010,57(1):31-43.

High Accuracy D/A Converter Design Technique

Wang Peng

(The 47th Research Institute of China Electronics Technology Group Corporation,Shenyang 110032,China)

As match accuracy and calibration resolution of poly resistor is poor,the accuracy of voltage type D/A converter based on poly resister R-2R network is limited.By researching some design techniques such as switch conduct resistor match,segmented switch match and segmented-ladder resistor network technique,the accuracy of D/A converter can be improved.Combining with resistor calibration and fine layout design method,the techniques above mentioned can realize D/A converter with accuracy exceeding 12 bits.

R-2R Resistor Network;D/A Converter;MOS Switch;Conduct Resistor;Match;Segmented-Ladder

10.3969/j.issn.1002-2279.2016.01.001

TN4

A

1002-2279(2016)01-0001-04

王鹏(1974-),男,辽宁省沈阳市人,高级工程师,硕士研究生,主研方向:集成电路设计。

2015-05-20