嵌入式应用系统中高速PCB设计技术的研究及实现

2016-11-17李俊杰曹旭东梁华庆

李俊杰,曹旭东,梁华庆

(中国石油大学(北京)地球物理与信息工程学院,北京 102249)

嵌入式应用系统中高速PCB设计技术的研究及实现

李俊杰,曹旭东,梁华庆

(中国石油大学(北京)地球物理与信息工程学院,北京 102249)

为了能够消除高速PCB技术中信号完整性的问题,需要在高速PCB设计过程中解决时序、噪声、电磁干扰等关键问题;通过对嵌入式RTU的高速PCB设计过程中出现的串扰、电磁干扰、振铃和电源完整性等信号问题的研究,提出削弱或消除以上噪声的方法;用Altium Designer、PADS软件绘制电路原理图和PCB,借助Hyper Lynx和ADS仿真软件进行前端和后端可靠性验证,根据仿真结果确定元器件和接插件的布局以及走线规则,最后通过对完成布线的PCB进行信号完整性验证;设计的嵌入式RTU电路板通过电磁兼容测试,表明该方法能够有效抑制噪声,增强高速数字电路设计的稳定性,提高产品设计的成功率,对从事相关工作的人员有很重要的参考价值,在智能设备的升级替换和推进物联网的建设方面有重要的借鉴作用。

高速PCB;信号完整性;嵌入式;RTU

0 引言

现代的电子系统向着封装小、规模大、速度快的趋势发展,与此同时,超大规模集成电路中,芯片的密度越来越大,这就不可避免的会带来一些问题,即如何分析和处理高速电路设计中互连线和叠层特征等因素。当今电子产品的时钟频率达到几百上千MHz,信号的上升沿和下降沿变的越来越陡,因此,设计此类产品时,PCB的布局布线规则和板材介电常数对系统的电气特性至关重要。

高速PCB电路设计是当前众多电子产品研发的必要流程和重要环节,时序问题、噪声干扰、电磁滋扰等是高速PCB电路设计的主要难题,这些问题的解决将关系到系统设计的正常运行。

国内在高速电路板绘制方面的研究起步相对较晚,EDA生产厂商的软件分析能力和设计优化流程还不完善,研发设计高速PCB电路需要投入大量的人力和财力。如果仍然采用传统的设计方法,生产出来的产品可靠性小、成功率低。因此,嵌入式应用系统中高速PCB的研究具有很高的实用价值和广阔的市场前景。

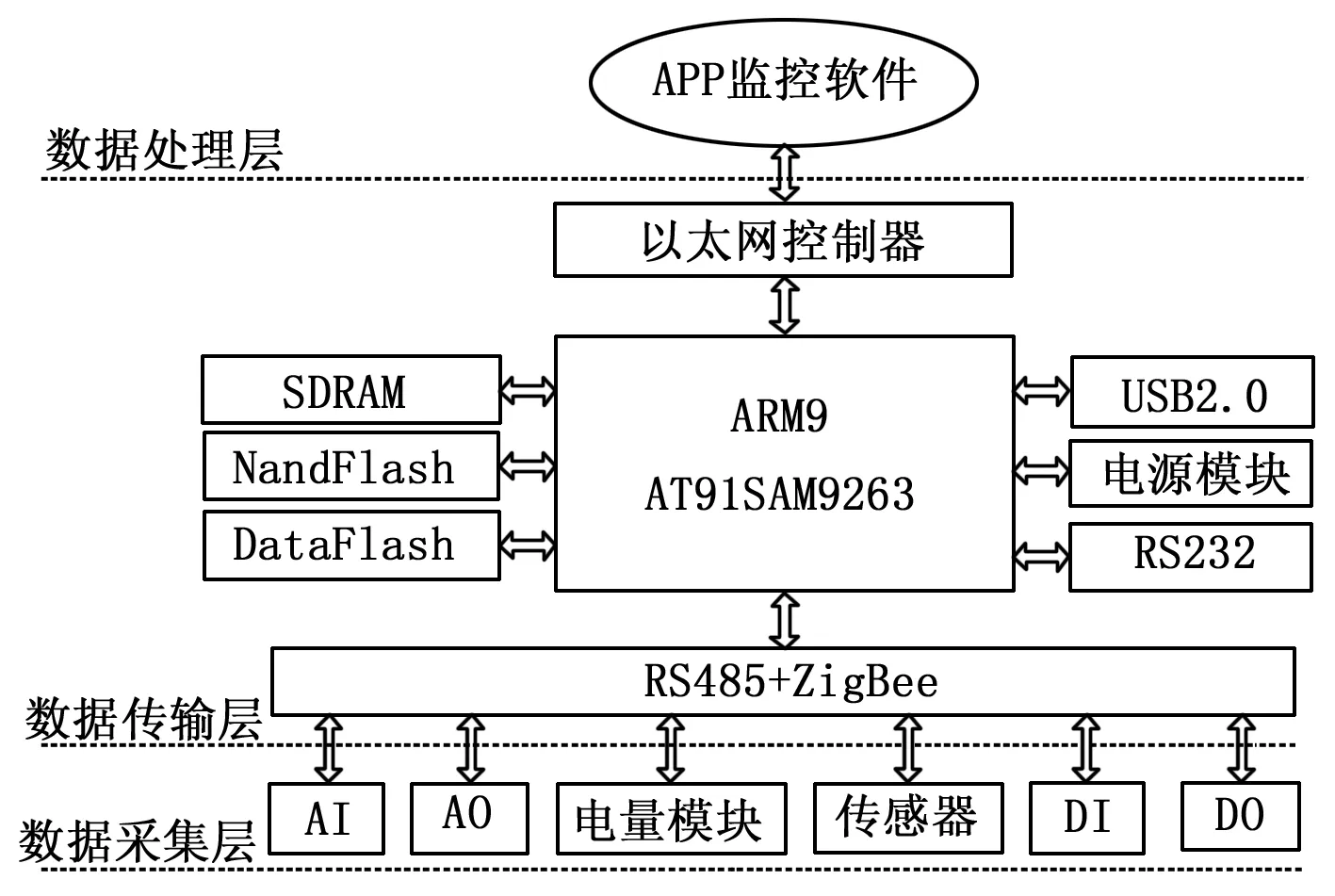

1 系统方案设计

图1所示为嵌入式RTU的功能框架,可以看出系统采用的是自上而下的通信结构,数据采集层包含电能单元、传感器单元和模拟量测量单元等;数据传输层的设备是网关,它通过Internet接收工程中心的命令调控上传数据采集层的数据;数据处理层由APP监控软件实现,实时处理、存储和分析数据,并将数据曲线面向用户操作界面,提高了数据采集的灵活性和管理效率。

图1 嵌入式RTU功能结构

2 RTU系统硬件构架

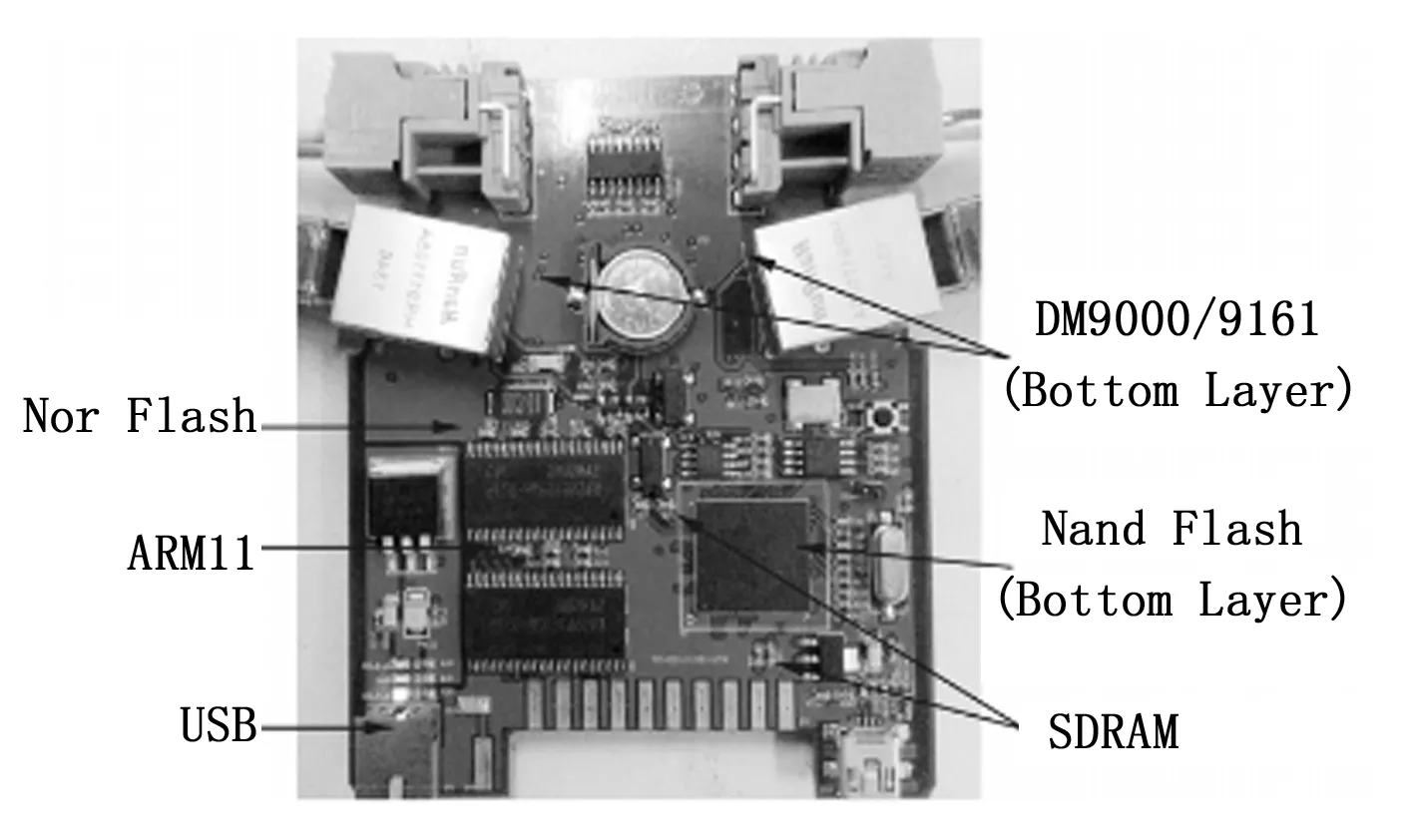

本嵌入式物联网RTU系统硬件主要由USB2.0、AT91SAM9263处理器、CAN、SDRAM、Nand Flash、Data Flash、以太网控制器、时钟芯片、 RS232/485接口、电源管理和数据采集部分组成。

该设计支持Linux操作系统,管理内存和设备的能力更强,可以实现复杂算法和通信协议的多任务实时性调度[2],负责网络连接、数据通信、配置采集设备等功能。图2是本文设计的RTU电路板。

图2 物联网RTU六层电路板

该系统支持IPv6和IPv4双栈协议,可以满足数据传输的及时性与实时性;在数据存储方面,满足在通信阻断下的本地存储,存储空间为8M;在通信接口方面,具备RS485、RS232、CAN总线等多种不同现场数据通信接口,支持Modbus RTU数据通信协议,可满足不同接口、不同通信速率的需求。

3 RTU系统PCB设计

3.1 系统PCB叠层设计

PCB叠层通常是2-32层,根据设计的难易程度选择。该RTU电路系统中元器件的封装密集、布局布线空间小、信号频率高等因素决定设置六层PCB,由上到下为Top电气层、电源网络内电层、信号电气层(InnerSignal1)、信号电气层(InnerSignal2)、地网络内电层、Bottom电气层。本系统中的FLASH和SDRAM都选为带状线结构,布线在PCB叠层参数中的InnerSignal 1和InnerSignal 2两层。

3.2 系统PCB约束规则制定

高速PCB电路设计过程中,信号线布线的间距、线长、线宽以及环路的就近处理将很大程度的影响到阻抗连续性和EMI等。元器件布局和布线的好坏关系到最终设计能否成功,因此必须合理制定PCB的约束规则。

Hyper Lynx具有干扰图表分析功能,可以采用IBIS模型精确模拟有损传输、差分信号和随频率变化的过孔模型[4]。利用其中的Line对系统中的主要网络在布线前仿真,改善高速PCB中的叠层结构和布线阻抗,根据仿真结果设计高速PCB网络的布线规则,提高设计效率。

3.2.1 阻抗控制规则

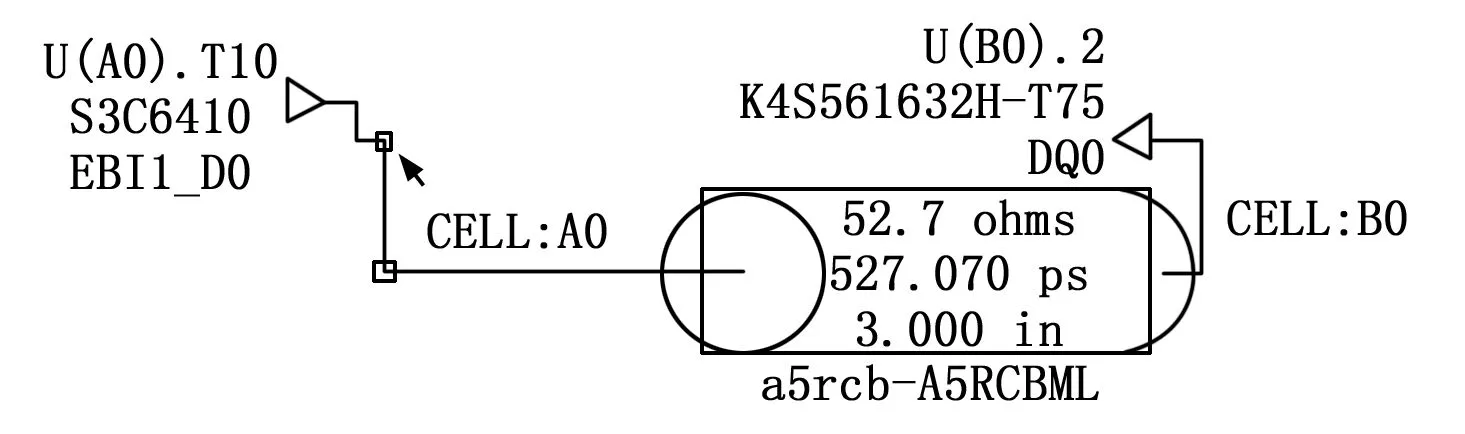

图3为本设计中主控芯片ARM9与存储芯片SDRAM之间的重要信号EBIO_D0-DQ0的Line仿真原理图。

图3 Line仿真原理图

指派AT91SAM9263的EBIO_D0管脚为驱动端,K4S561632H的DQ0管脚为接收端,传输线类型选择带状线(Stripline),线宽0.12 mm,线长76 mm,与上下两个参考层的距离为0.25 mm,驱动端输入220 MHz的激励源。

由于本设计的时序比较繁琐,因此在设计中布线长度延迟必须小于速率的1/6,板材选用电容率为4.3的,计算得信号延迟1.47×108 m/s。查看驱动端IBIS文件中上升沿dv/dt_r 一般为1.43 ns,因此走线最长为1/6×1.4×5.79=34 mm,根据反复试验,得出最小振铃的走线为8.89 mm。

根据设计的规则,带状信号线的阻抗是52.7 Ω,驱动侧的I/0阻抗是9.6 Ω,由此可得串联电阻的阻值为43.1 Ω。

3.2.2 布线参数规则

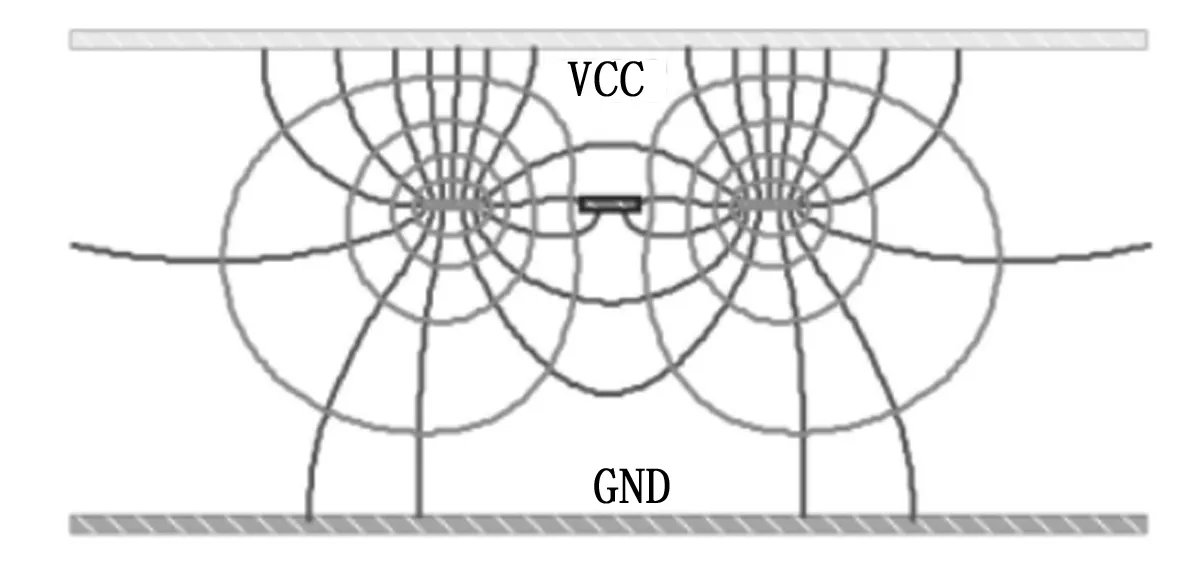

高速PCB电路在设计过程中,必须要注意控制高速信号的串扰布线,制定布线约束规则。在Line仿真原理图中配置三条关键信号线EBIO_D0-DQ0、EBIO_D1-DQ1、EBIO_D2-DQ2,布线都在Stripline层,与电源内电层和地内电层的距离分别为0.254 mm和0.508 mm,线宽为0.12 mm,线间距为3.05 mm ,耦合布线长度为8.89 mm,设计目标是串扰强度不超过165 mV,仿真结果如图4所示。

图4 串扰仿真图

图4中,由信号线向外散射的线条是电场线,以信号线为中心的环形线是磁场线,可见,串扰是容性耦合和感性耦合噪声的叠加。根据设计原理,适当加大三根信号线的距离可以消除串扰的噪声,但是由于布线密度大,调整信号线的距离会加大布线的面积,因此,在保持PCB电路板大小不变的情况下,不仅需要最大程度的改变线与线之间的距离,电路板中的信号层尽可能接近参考平面。将线间距变为0.38 mm,将内层带状线与电源层距离变为0.203 mm,带状线与地层距离调整为0.46 mm,图5为调整后的仿真结果。

图5 调整后的串扰仿真图

综上所述,在绘制PCB之前,通过Hyper Lynx软件做前端仿真,最终制定系统高速信号线的约束规则为:线宽0.12 mm;线间距0.38 mm;走线长8.89 mm。

3.3 系统PCB板级仿真

高速PCB设计中,前端仿真使用理想传输线模型,一次只能对有限数量的信号线进行仿真,而PCB后端仿真中的传输线是实际的PCB走线,掺杂了过孔、切换层次等影响特征阻抗的因素,这种情况下得到的仿真结果真实性强[5]。

在系统核心电路的设计过程中,单端信号的终端匹配电阻要求在40~60 Ω之间,信号线的相互串扰阈值为165 mV。而且,为了让DM9000和DM9161网络控制器能够自适应100 Mbps的通信速率,差分阻抗必须匹配在100±5 Ω范围之内。这里仍然使用Mentor Graphic公司的Hyper Lynx仿真软件对SDRAM总线、以太网差分总线、电源完整性和电磁兼容性进行了PCB板级仿真。

3.3.1 SDRAM总线设计

在设计带状线时,串扰和过孔是生成时延的主要原因。即便按照Line仿真工具确定的布线规则来绘制PCB,在项目的研发中,不可避免地碰到元器件管脚太多和电路板尺寸有限等问题,所以,利用Board仿真工具对多个网络进行适当的仿真是必须的。

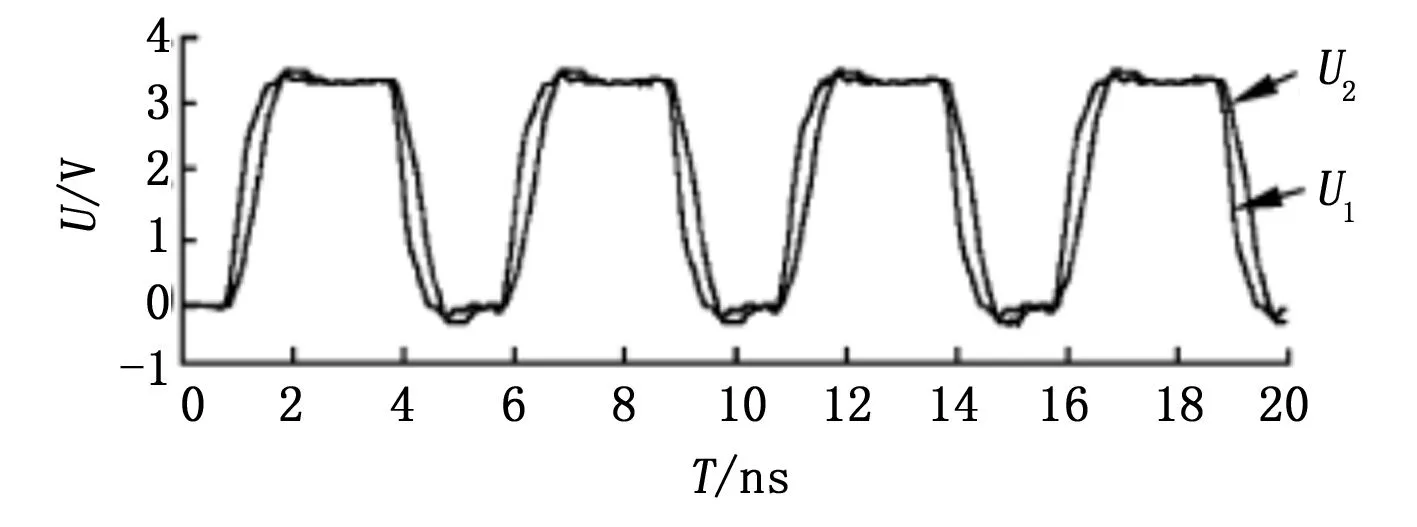

根据仿真,虚线网络EBI_D0和EBI_D2的串扰强度大于165 mV,这两条网络对EBI_D1的进行攻击,查找耦合地方,是因为图中黄色标示区域蛇形线间距不合适。可知,加大布线间距就不会存在这样的问题,但是,我们更应该关心为什么攻击网络有如此强的干扰,可能是因为在实际的布线过程中,端接电阻选取不恰当,造成阻抗不匹配的原因。目前选取的端接电阻阻值为43.1 Ω,在220 MHz的激励情况下,网络EBI_D1的分析仿真波形如图6所示。

图6 Board板级D1的仿真图

由图6可以看出EBI_D1传输线发生阻抗突变,信号波形已经发生畸变。虽然不会造成系统无法启动,但是设计出来的产品运作的稳定性无法保障。回到Board仿真,使用过孔和有损仿真,运行Wizard向导,把EBI_D0、EBI_D1、EBI_D1端接电阻阻值改为46.9 Ω。此时仿真分析,被害网络和进攻网络的串扰如图7所示,网络的信号已经得到改善,在EBI_D1上引起的干扰强度也明显降低。

图7 改变串接电阻后的仿真图

3.3.2 Enternet差分总线设计

Hyper Lynx的Board仿真模块具有针对高速、“3GIO”互连设计的特点,根据差分信号总线的标准使用超快速的串行数据通路、源同步技术,为高速PCB设计提供了方便、高效的解决方案[6]。本系统中的DM9000和DM9161都有两对高速信号差分总线:TX+、TX-和RX+、RX-,差分阻抗必须为100 Ω,从其传输原理不难得到差分阻抗的计算公式为:

式中,Z是每条信号线的传输阻抗,它对有用信号的通信距离和抗噪声能力有重要影响。这里选择DM9000的发送差分对网络TP_E_TX+和TP_E_TX-,为了减少反射的影响,在信号线最后都并联100 Ω电阻,同时使能过孔模型,如图8所示,当前设计的差分阻抗为102.1 Ω。

图8 网络控制器差分阻抗仿真图

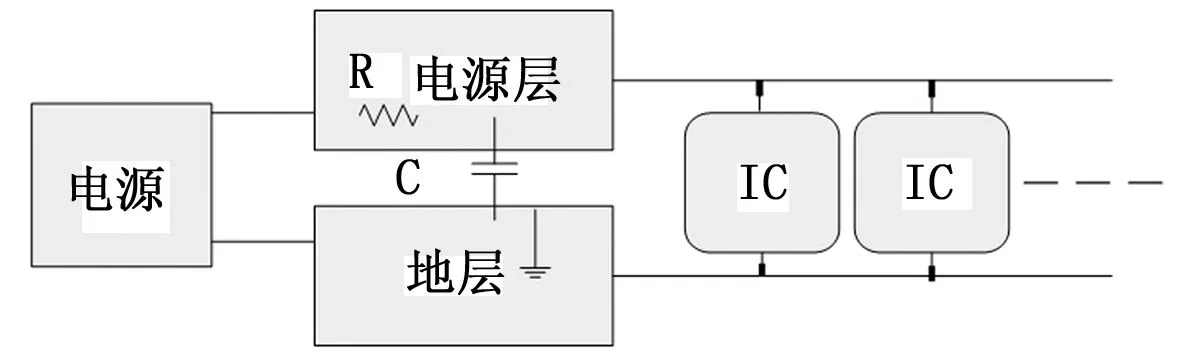

3.3.3 系统电源完整性设计

如图9所示为基本的电源分布模型,电流通过电源层传输到各负载,然后由地层形成回路。

图9 基本电源分布模型

在绘制高速PCB过程中,要计算电路系统中每个单元的功耗,正确布局并适当增大电源网络的宽度。

归纳6个层面的电源完整性,最大压降为2.1 mV,靠近于0.06%,电流的最大密度为16.3 mA/m2,在适当范围内,如果电流密度大于50 m A/m2会造成PCB板升温,对运行过程中的主要芯片和信号线造成影响。铜皮宽度的适当加大可减小电流密度,如果条件不允许,可以加厚信号导线的厚度,降低PCB板的温度。

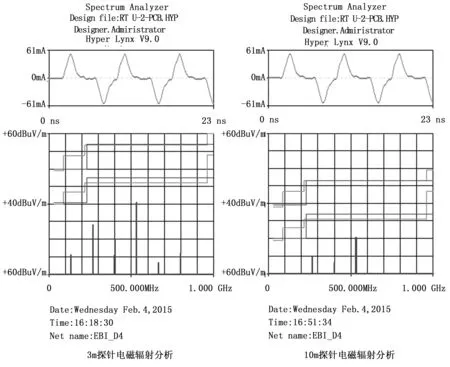

3.3.4 系统电磁兼容性分析

电磁干扰通常是以耦合的形式掺杂有用信号作为载体传导。本设计中使用Hyper Lynx仿真软件对初步设计完成的PCB做辐射强度分析。选择ARM9和SDRAM之间的关键信号线D4,分别设置探针位置3 m和10 m,在220 MHz激励源的情况下,得到FCC和CISPR国际标准的仿真数据,如图10所示。

图10 信号线D4电磁辐射仿真分析

从仿真结果可知,距离PCB越近,受电路板的辐射影响越强,且随着传输信号的频率不同而变化。在设计高速数字电路时除了优化电路板本身的抗干扰性能,还要尽可能的降低产品对外的噪声辐射。

4 网络通信测试

把制作好的Uboot、内核和文件系统下载到电路板中,PC机连接网关的调试串口,给电路板上电,在Secure CRT终端中可以看到串口的打印信息,说明内核和文件系统移植成功,电路板启动正常。在终端用#ifconfig命令查看电路板两个网口eth0、eth1的IPv4地址为192168115和192168118,IPv6地址为fe80::5a76:75ff:fe10:57/64和fe80::1034:56ff:fe78:9000/64,而且eth0的HWaddr是58:76:75:10:00:57,这正是在DM9000驱动程序的dm9000_plat_data结构体中定义的。

用ping命令与IPv4地址为192168166的虚拟机进行数据通信,双方各自收发10个数据包,在Redhat平台用wireshark工具监控网络通信,数据包丢失率为0。

5 结论

在高速PCB的设计过程中,本文解决了时序、噪声、电磁干扰等关键问题,提出了削弱或消除在高速PCB设计过程中出现的串扰、电磁干扰、振铃和电源完整性等信号问题,设计的高速PCB成功克服了信号完整性问题。

设计的基于嵌入式处理器ARM9的IPv4/IPv6双协议栈物联网RTU,经过连通性测试、协议转换测试、远程控制等多方面测试,表明功能和性能指标稳定。该方案适用于10/100 MHz以太网接口模式,并实现了全双工通信方式的自动识别,能够有效地利用宽带资源,提升网络数据的传输速度。

测试结果表明此方案设计的嵌入式RTU系统工作稳定,在智能设备的升级替换和推进物联网的建设方面有重要的借鉴作用。

[1] 邵 鹏.信号/电源完整性仿真分析与实践第1版[M].北京:电子工业出版社,2012.

[2] 吴 蕾.基于ARM9的车载彩色液晶仪表显示平台设计[D].哈尔滨:哈尔滨工程大学,2009.

[3] 朱亚地.高速PCB信号反射及串扰仿真分析[D].西安:西安电子科技大学,2012.

[4] GangDing, Sahinoglu, Orlik et al. Tree-Based Data Broadcast in IEEE 802.15.4 and ZigBee Networks. IEEE transactions on mobile computing, 2006, 5(11): 1565-1568.

[5] 闫铁铮.高速PCB信号完整性分析及硬件系统设计中的应用[D].厦门:厦门大学,2009.

[6] 胡海欣.高速PCB板级信号完整性问题研究[D].长沙:国防科技大学,2004.

[7] GangDing, Sahinoglu, Orlik, et al. Tree-Based Data Broadcast in IEEE 802.15.4 and ZigBee Networks[J]. IEEE transactions on mobile computing, 2006, 5(11): 1565-1568.

[8] Stevens W R. TCP/IP详解第1版[M]. 范建华,译.北京:机械工业出版社,2000.

[9] 杜 晓,雷治军.一种嵌入式IPv4/IPv6双协议栈的实现[J].计算机应用,2008,28(2):407.

Design of High-speed PCB Technology in Embedded Application System

Li Junjie, Cao Xudong, Liang Huaqing

(College of Geophysics and Information Engineering, China University of Petroleum-Beijing, Beijing 102249, China)

In order to eliminate the incompleteness of signals in high-speed PCB technology, there are some key issues should be solved, including timing, noise, electromagnetic and so on, in the design process of the high-speed PCB technology. In the process of high-speed PCB of embedded RTU, this paper studies the problems like crosstalk, electromagnetic interference, ringing effect and power integrity and so on, and proposes the ways to weaken or eliminate those noises. Circuit schematics and PCB are drawn by using Altium Designer, PADS software and the reliability of the front and rear parts is verified by means of Hyper Lynx and ADS simulation software. At the same time, the layout of components and connectors and wiring rules are determined based on the simulation results. Finally, this paper verifies the completeness of signal through the wiring of the PCB. The electromagnetic compatibility test shows that this method can suppress noise effectively, enhance the reliability of high-speed digital circuit design, and increase the success rate of product design, having a great reference value for the personnel engaged in related work. And there are important

in the replacement and upgrade of smart devices and promotion of networking building.

high speed PCB; signal integrity; embedded; RTU

2016-04-06;

2016-05-04。

国家发改委下一代互联网技术在智慧油田的应用示范项目(CNGI-12-03-043)。

李俊杰(1989-),男,山东潍坊人,硕士研究生,主要从事油田电子信息与通信技术方向的研究。

1671-4598(2016)06-0268-03

10.16526/j.cnki.11-4762/tp.2016.06.073

TN402

A