一种Ku波段、K波段频综模块的设计与实现★

2016-11-16韩俊辉郝邵杰彭文辉

韩俊辉,郝邵杰,彭文辉

(1. 中国电子科技集团公司第41研究所,青岛 266555;2. 海军潜艇学院,青岛 266044)

一种Ku波段、K波段频综模块的设计与实现★

韩俊辉1,郝邵杰1,彭文辉2

(1. 中国电子科技集团公司第41研究所,青岛 266555;2. 海军潜艇学院,青岛 266044)

为满足某Ka波段变频模块对小型化快速跳频本振信号的需求,设计了一种频综模块,该模块采用了锁相环频率合成方案,为满足跳频时间的要求,增加了预置电路,同时对锁相环环路参数进行优化设计,最终在160mm*90mm的面积内实现了两个跳频本振信号的发生,其跳频时间为≤160μs;单边带相位噪声为≤-80dBc/ Hz@1kHz;≤-95dBc/Hz@100kHz;上述指标均符合设计要求,现场测试结果表明,该模块性能良好,稳定可靠,满足使用要求。

锁相环;频综模块;单边带相位噪声;环路滤波器

0 引言

频综模块是现代电子系统的重要组成部分,在通信、雷达、导航、航空航天以及遥测等领域有着广泛应用。频综模块通常作为本振信号或者参考信号,可以称作电子系统的“心脏”,其性能指标直接决定了系统的性能指标[1-2]。

频综模块通常采用的频率合成技术包括:直接频率合成技术(DS)、锁相环频率合成技术(PLL)和直接数字频率合成技术(DDS)三种。直接频率合成具有快速频率切换、低相位噪声和高输出频率等优点,其缺点是输出端的寄生分量多和集成度差,而直接频率合成的这些缺点在锁相频率合成中可大大减少。DDS具有快速频率切换和低相位噪声等优点,缺点是输出频率较低且杂散信号较多[3-5]。

本文介绍了某天线系统用频综模块的详细设计。文中第1部分介绍了频综模块的指标要求、总体设计方案以及器件的选择;第2部分介绍了频综模块系统分析和详细设计;最后对该频综模块相关指标进行测试并得出结论。

1 频综模块设计方案

1.1 设计要求

本文设计的频综模块主要包括两段本振信号的技术指标:

频率范围:Ku波段,带宽1600MHz;K波段,带宽1600MHz;

单边相位噪声:≤-65dBc/Hz@100Hz;≤-75dBc/Hz@1kHz;≤-85dBc/Hz@10kHz;≤-95dBc/Hz@100kHz;≤-111dBc/Hz@1MHz;

频率分辨率:100Hz;跳频时间:≤200μs;功耗:≤8W;体积:160×90×30(mm3)。

1.2 设计方案

由于需求频率高,而当前主流的DDS频率合成芯片均比较低,且会带来很多难以处理的杂散信号,增加了电路的复杂性。综合考虑系统的指标、体积和功耗的要求,本文采用锁相环频率合成技术实现频综模块设计。

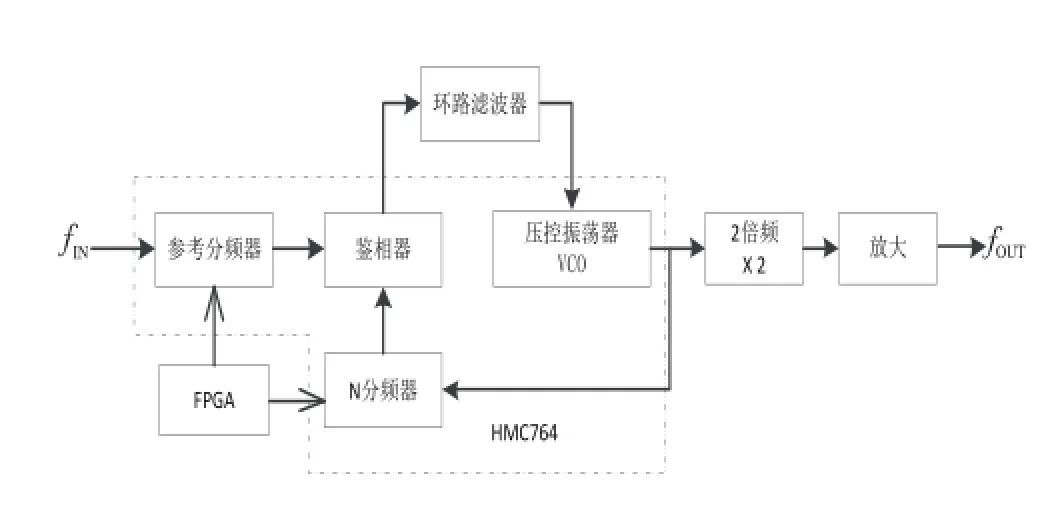

图1为频综模块Ku波段本振原理框图。该方案采用内置VCO的集成频率合成芯片HMC764组成锁相环路,产生较低的C波段扫频信号,然后经过2倍频和放大得到想要的Ku波段信号。考虑到倍频对单边相位噪声的恶化,该环路C波段信号相位噪声需要达到:≤-71dBc/Hz@100H;≤-81dBc/ Hz@1kHz;≤-91dBc/Hz@10kHz;≤-101dBc/Hz@100kHz;≤-117dBc/Hz@1MHz。

图1 Ku波段本振原理框图Fig. 1 Ku-band LO principle block diagram

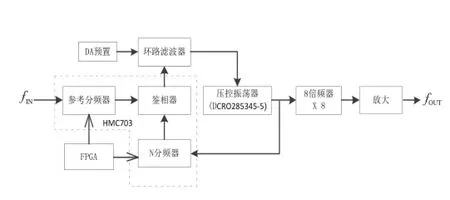

图2 K波段本振原理框图Fig. 2 Ku-band LO principle block diagram

Ku波段本振选择的频率合成芯片HMC764是Hittite公司的高性能频率合成芯片。其特点是:内置VCO,集成度高;可实现100KHz至220MHz鉴相频率;小数分频,具有较好相位噪声性能。由其数据手册可知,当选用100kHz的环路带宽时,能达到的单边带相位噪声为:≤-75.0dBc/Hz@100Hz;≤-95.0dBc/Hz@1kHz;≤-101.0dBc/Hz@10kHz;≤-102.0dBc/Hz@100kHz;≤-120.0dBc/Hz@1MHz。能够满足设计要求。

频综模块K波段本振的原理框图如图2所示。频率合成芯片HMC703和压控振荡器DCRO285345-5组成锁相环,输出S波段扫频信号。该信号经过倍频、滤波和放大得到所需的K波段信号。其中在VCO之前加入了DA预置电路,它的作用是在跳频时加入一个预置电压到VCO,减少了跳频时间。同样考虑到倍频对相位噪声的恶化,S波段扫频信号的指标要求为≤-83dBc/Hz@100Hz;≤-93dBc/ Hz@1kHz;≤-103dBc/Hz@10kHz;≤-113dBc/Hz@100kHz;≤-129dBc/Hz@1MHz。

频综模块K波段本振的主要器件为频率合成芯片HMC703和压控振荡器DCRO285345-5。频率合成芯片HMC703是Hittite公司的高性能频率合成芯片,它的主要特点:较宽的射频输入频率范围;具有较好的相位噪声;最高知100MHz的鉴相频率;较低的杂散;以及超低的噪声基底。此外HMC703内部还集成了一个24位的小数调制器,能够实现高分辨率的小数频率输出。压控振荡器(VCO)同样对锁相环的性能具有很大影响。综合考虑相位噪声、调谐灵敏度、控制特性和功耗等方面的因数,本文选择Synergy公司的DCRO285345-5作为锁相环路的VCO。根据该VCO的相位噪声曲线图选择合适的环路带宽即可满足指标要求。此外,加入DA预置电路,减少了本振的跳频时间。

2 频综模块设计方案

由于频综模块的两个本振采用类似的设计方案,设计过程中比较相似,下面就主要介绍K波段本振的设计,Ku波段本振就不再赘述。

2.1 系统分析

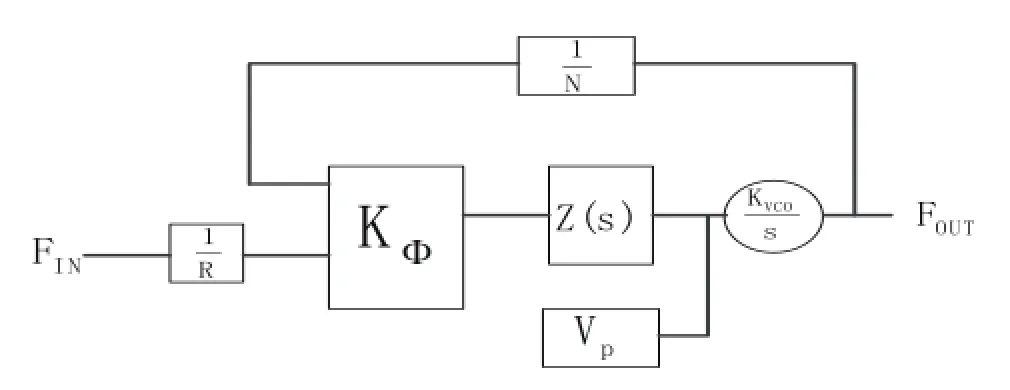

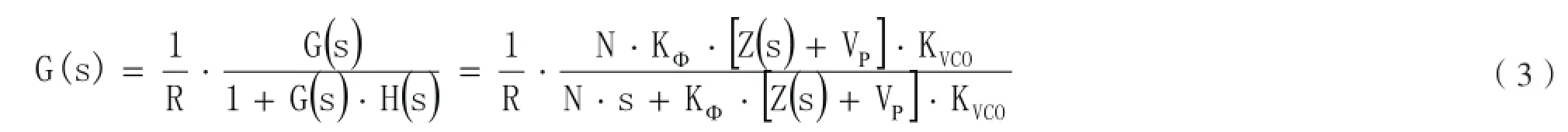

本文所选择的PLL频率合成方案,作为经典控制理论的闭环控制系统,可利用控制理论对其进行分析。此处,不考虑后端的倍频部分,前面所组成的闭环系统的控制系统框图如图3所示。图中KΦ为电荷泵鉴相器的鉴相增益,Z(s)为环路滤波器传递函数,Vp为预置电压,KVCO为VCO的调谐灵敏度,N为反馈回路分频器分频比,R为前置分频器分频比[6-7]。

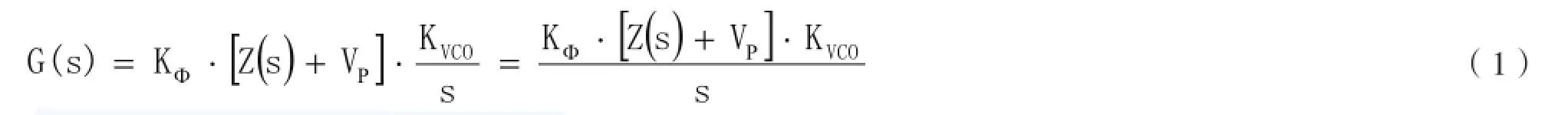

由图3可推出系统的前向传递函数为G(s)

图3 控制系统框图Fig. 3 The control system block diagram

系统的反馈回路传递函数为H(s)

由图3和公式(1)、公式(2)可得系统的闭环传递函数

对于锁相环控制系统,主要关心其稳定性和快速性。系统的相对稳定性由相位裕度和幅值裕度来度量,而快速性对于锁相环来说就是跳频时间的长短。

设Fc为锁相环的环路带宽,ωc=2πFc

可得相位裕度为

2.2 鉴相灵敏度与鉴相频率的选取

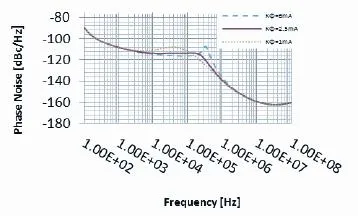

对于内置电荷泵鉴相器的PLL频率合成芯片,电荷泵噪声是锁相环带内的主要噪声源之一。选择合适的鉴相增益可以获得良好的环路性能。本文利用Hittite公司的PLL Design & Analysis Tool软件对环路进行仿真来获得较优的鉴相增益。在其他参数不变的情况下,改变电荷泵的鉴相增益KΦ,得出结果如图4所示。

由图4知,提高鉴相增益可以改善锁相环路的相位噪声,但随着鉴相增益的提高,电荷泵输出电流增大,环路内器件的热噪声和散弹噪声也逐渐变大而不容忽视,使得环路带宽附近和远端的相位噪声变差[8]。经过以上的分析和多次仿真后,本文选择KΦ为2.5mA。

图4 不同鉴相增益下的系统相位噪声Fig. 4 The system phase nosie in different phase detection gains

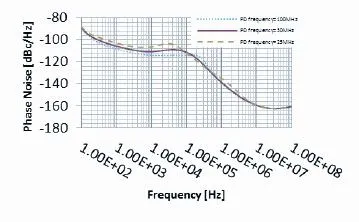

图5 不同鉴相频率下的系统相位噪声Fig. 5 The system phase nosie in different phase detection frequencies

鉴相频率的选择对锁相环路的性能具有非常大的影响,一般来说,在参考频率固定,VCO输出频率不变的前提下,增加鉴相频率可以同时减小R分频器和N分频器的值,较为明显的降低了锁相环路带内的相位噪声[7]。不同鉴相频率下的PLL相位噪声如图5所示。此外,高的鉴相频率增大了PLL环路带宽,有利于环路快速锁定,减小跳频时间。HMC703在小数模式下最大的鉴相频率为100MHz,本文选择的鉴相频率为最大频率100MHz,R分频器的值为1。

2.3 环路滤波器的设计

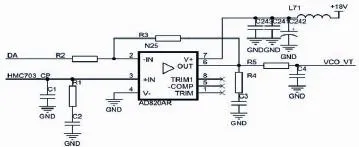

环路滤波器作为锁相环路中设计最为灵活的部分,在鉴相频率、鉴相灵敏度、VCO输出确定后,对系统的稳定性和跳频时间具有很大的影响。环路滤波器主要分为无源滤波器和有源滤波器两大类。无源滤波器良好的相位噪声,而有源滤波器由于引入有源器件而带来更多的噪声,但有源滤波器增加了环路增益,一般用在鉴相器的电荷泵输出不足以驱动VCO情况下。

同时为减小锁相环的跳频时间,加入电压预置电路。电压预置电路将DAC输出的电压值与环路滤波器输出的电压值比例相加,经低通滤波后加到VCO的调谐端,使锁相环工作在快锁带内,从而快速锁定。但电压预置电路的加入也带来负面的影响,加入的DA和运算放大器给环路带来新的噪声,使环路相噪恶化。所以在设计时选择低噪声的运放来减少噪声的产生。

确定选用有源滤波器后,下面对环路滤波器的环路带宽和相位裕度进行选择。环路带宽选择主要是在杂散和锁相时间之间进行权衡[9]。小的环路带宽能够改善杂散却会牺牲锁相时间,而宽的环路带宽正好反之。相位裕度的选择同样重要,它是反映系统相对稳定性的重要指标。对于锁相环,相位裕度一般选择在40°~55°之间,仿真显示在相位裕度48°时系统具有最优的锁相时间,而在50°时具有较好的相位误差。综上,我们选择有源环路滤波器,环路带宽为200KHz,相位裕度为50°[6,10]。具体电路结构如图6所示。

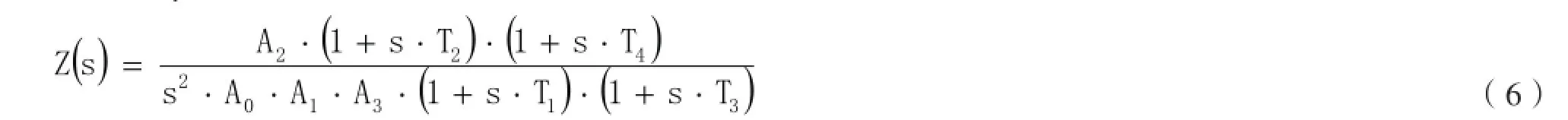

由图6环路滤波器的电路结构,设DA的输出为0,即Vp可得出环路滤波器传递函数为:

图6 环路滤波器电路图Fig. 6 The loop filter's circuit diagram

式中

对于电压预置部分,DA输出的电压经过比例积分和后端的滤波电路添加到VCO。在频率变化时DA输出电压到VCO的时间包括DA元器件内部消耗时间和外部电容充电时间。由于DA元器件内部消耗时间和外部电容充电时间均在几百纳秒到几微妙远远小于系统的跳频时间。所以在本文中忽略电压预置部分电路达到稳定时间。设预置电路部分DA输出为VDA,则

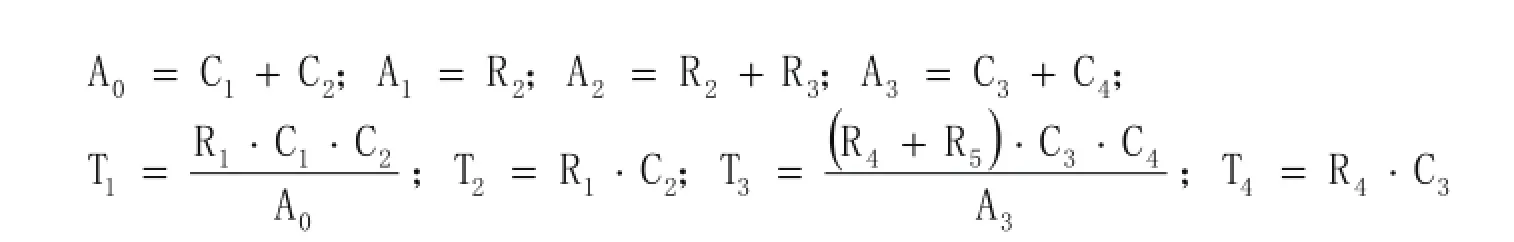

由环路带宽Fc为200KHz,相位裕度γ为50°,VDA= -1V。合理选择零点和极点的比值,即T1~T4的比例关系,加上公式(4)~公式(7)可以选出各元器件较优的值。经仿真和实际的调试选出的各元器件值如表1所示。

此外,其他的一些注意事项包括:锁相环路中各器件分别供电,减少其他器件电源噪声的影响;在器件的供电管脚添加磁珠和电容对电源进行滤波和去耦,减少电源噪声的影响;模拟地与数字地有效分割,减少数字电路对锁相环的干扰;增加屏蔽措施、合理的布局和良好板材的选取等均能提高锁相环的性能。

表1 环路滤波器各元器件值Tab. 1 The value of components in the loop filter

表2 环路滤波器各元器件值Tab. 2 The value of components in the loop filter

3 频综模块设计方案

利用频谱仪对频综模块的单边相位噪声和频率分辨率进行测试。分别对两个本振信号带宽内高频点、低频点两个的单边相位噪声进行了测试,结果如表2所示,满足设计指标。频率分辨率可达100Hz,满足设计需求。

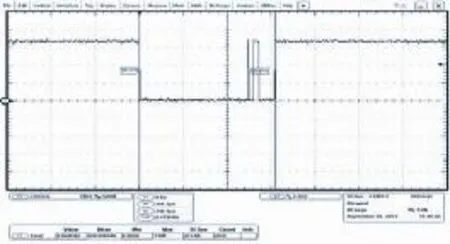

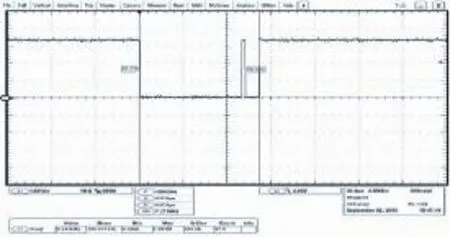

HMC703管脚LD_SDO可以输出锁相芯片的锁定信息,环路锁定时,该管脚输出为高电平,失锁状态时,为低电平。利用示波器监测管脚LD_SDO即可测试K波段本振的跳频时间。图7为锁相环的从最低频点跳至最高频点的所用时间测试曲线,为154.5μs;图8为锁相环最大的反跳时间测试为137.5μs,均满足设计要求。同样HMC764 的LD_SDO管脚可以测出Ku波段本振的跳频时间,测得最大反跳时间测试为152.5μs,最小反跳时间测试为160μs,均满足设计要求。

图7 最大正跳跳频时间测试曲线Fig. 7 The MAX positively hop time test curve

图8 最大反跳跳频时间测试曲线Fig. 8 The MAX positively hop time test curve

4 结论

根据上述的测试结果,本文设计的频综模块满足系统的指标要求。该频综模块具有输出频率高,相位噪声低,输出杂散等特点。现场测试结果表明,该模块性能良好,稳定可靠,可满足具体使用要求,具有较好的工程应用价值。

[1] Schlecker Benedikt,Dukic Maja,Erickson Blake,et al. Single-cycle-PLL detection for real-time FM-AFM applications [J]. IEEE Transactions on Biomedical Circuits and Systems,2014,8(2),206-215.

[2] 赵伟波,管凤仁,祁佑光.S频段小数分频锁相环频率合成器实现与应用[J]. 飞行器测控学报,2011 (30) :31-34. ZHAO Weibo,GUAN Fengren,QI Youguang. Implementation and Application of S Band Frequency Synthesizer[J]. Journal of Spacecraft TT&C Technology,2011 (30) :31-34.

[3] 钱俊. 功率超声波电源频率跟踪系统设计[J].新型工业化,2014,4(8):59-65. Qian Jun. Design of a Frequency Tracking System for Power Ultrasonic Generator[J]. The Journal of New Industrialization,2014,4(8):59-65.

[4] 万天才.频率合成器技术发展动态[J].微电子学,2004(34):366-370.

WAN Tian-cai. The Latest Development of Frequency Synthesizer Technology[J]. Microelectronics,2004(34):366-370.

[5] Feng Xiaodong,Cheng Guohui,Mu Kaiming. Fast frequency hopping technology and SAW direct frequency synthesizer in radar and communication [J]. Qinghua Daxue Xuebao/Journal of Tsinghua University,1997,37(5),289-292.

[6] Xu Xiaoliang,Liu Huihua,Tan Weifeng. Parameters design of 1.25GHz low jitter charge pump PLL [J]. ICEICE 2011 -Proceedings,2011,3418-3421.

[7] 宋强,宋建国,孙梦娟.基于MCU和FPGA双处理器的超音频感应加热电源设计[J].新型工业化,2015,5(4):48-54.

SONG Qiang,SONG Jianguo,SUN Mengjuan. The Design of Audio-frequency Induction Heating Power Supply System of Dual Microprocessor Based on MCU and FPGA[J]. The Journal of New Industrialization,2015,5(4):48-54.

[8] 丁志钊.基于 PLL 频率合成器锁相环的降噪技术[J]. 电子测量技术,2009 (32) :44-46.

Ding Zhizhao. Study of improving phase noise in thePLL based on PLL frequency synthesizer[J]. Electronic Measurement Technology,2009 (32):44-46.

[9] 郝绍杰.基于集成频率合成器的锁相环设计[J]. 国外电子测量技术,2008 (27) :12-15.

Hao Shaojie. PLL design based on integrate frequency synthesizer[J]. Foreign Electronic Measurement Technology,2008 (27) :12-15. [10] Dean Banerjee. PLL Performance,Simulation,and Design[M]. Fourth Edition,2006,167-276.

A Kind of Ku-band and K-band Frequency Synthesizer’s Design and Realization

HAN Jun-hui1, HAO Shao-jie1, PENG Wen-hui2

(1. The 41th Academy of CETC, Qingdao 266555, China; 2. Navy Submarine Academy, Qingdao 266044, China)

In order to meet the demand of the small and fast frequency hopping mode of a Ka-band frequency conversion module, a frequency synthesizer module was designed. The module uses a phase-locked loop frequency synthesis scheme, and increased the preset circuit to meet the requirements of frequency hopping time.At the same time the phase-locked loop parameters was optimal designed, and eventually achieved a two frequency hopping signals generation within the area of 160mm*90mm. And its hopping time is ≤160μs, SSB phase noise is≤-80dBc/Hz@1kHz;≤-95dBc/Hz@100kHz.All the above indexes conform the design requirements. Field test results show that the module has perfect performance, stable and reliable, and meet the requirements of use.

PLL;Frequency synthesizer;SSB phase noise;Loop filter

10.3969/j.issn.2095-6649.2016.02.002

HAN Jun-hui, HAO Shao-jie, PENG Wen-hui. A Kind of Ku-band and K-band Frequency Synthesizer’s Design and Realization[J]. The Journal of New Industrialization, 2016, 6(2): 7-12.

国家自然基金项目(61473306)

韩俊辉(1987- ),男,工程师,主要研究方向:电子测量仪器

本文引用格式:韩俊辉,郝邵杰,彭文辉. 一种Ku 波段、K 波段频综模块的设计与实现[J]. 新型工业化,2016,6(2):7-12.