基于光链路和被覆线链路双冗余的采集数据传输系统设计

2016-11-10臧习飞黄天发李瑞勤商昌文

臧习飞 黄天发 李瑞勤 商昌文

(中国电子科技集团公司第三十四研究所,广西 桂林 541004)

基于光链路和被覆线链路双冗余的采集数据传输系统设计

臧习飞黄天发李瑞勤商昌文

(中国电子科技集团公司第三十四研究所,广西 桂林 541004)

为了提高采集数据传输的可靠性,提出了一种基于光链路和被覆线链路互为热备份的采集数据传输系统。系统采用光链路和被覆线链路双冗余传输路径,通过对两种路径传输品质的监测,利用仲裁器自动倒换传输路径。并通过同步缓冲设计,实现了两种传输路径采集数据的同步输出。同时进行了合理的软、硬件设计,实现了数据双冗余链路传输。

光链路;被覆线链路;双冗余;保护倒换

1 引言

在现代数据采集系统中,后端处理机可通过对多个节点采集数据分析、处理和研究即可获得大量的目标特征信息,具有广泛的应用。而数据采集的前端往往放置于比较恶劣的环境中,因此采集数据的可靠传输成为急待发展的关键技术。

本文提出了一种基于光链路和被覆线链路双冗余的采集数据传输系统,将双冗余保护结构引入采集数据的传输系统,依靠对传输路径硬件冗余,通过对路径传输品质的监测,利用仲裁器自动倒换传输路径,具有可靠性高、自倒换时间短等特点。同时可自动同步两种传输路径采集数据,非常具有实用价值。

2 系统设计

2.1系统总体目标

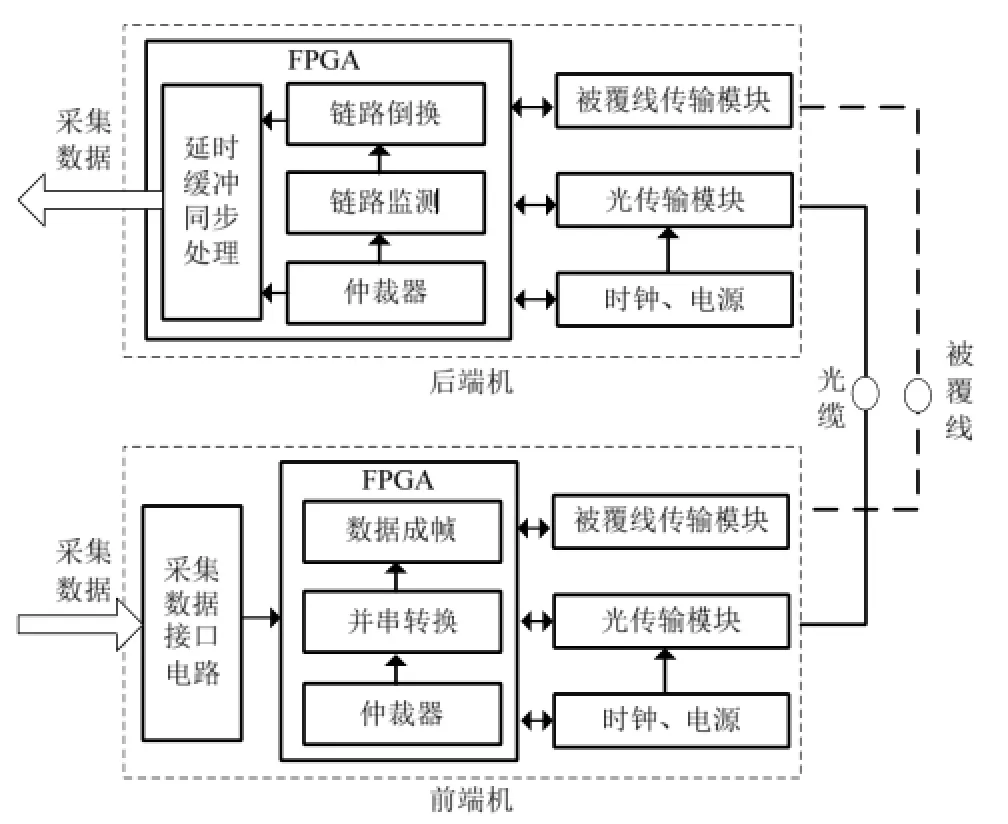

系统采用光链路和被覆线链路双冗余传输方案,对采集数据传输路径冗余备份。FPGA处理模块实时监测传输链路的工作状态;当某段链路发生故障,无需人工干自动完成传输路径保护倒换,确保该采集点数据传输正常,保证了采集系统工作的可靠性。系统原理框图如图1所示。

由于采集数据经光链路和被覆线链路传输延时不同,为了同一时刻采集数据经不同传输链路后同时输出,在后端设备应设置恰当的延时缓冲时间。该延时缓冲时间可通过测量两种传输链路的传输延值计算后得出,采集数据同步后即可送入上位机进行处理。

图1 系统原理框图

2.2延时同步原理

延时同步由链路延时测定和同步缓冲控制两部分组成。当传输路径确定后,由后端设备产生一长周期延时测量伪随机序列,切换到传输链路上。前端设备将接收到该码回环,经相同传输路径传输回后端设备。后端设备锁定接收序列,同时复制发送序列延时缓冲后同步于锁定的接收序列,然后由码相位比较器对比即可求出当前链路延时时间。依次测的光链路、被覆线链路传输延时时间。

同步缓冲控制通过链路延时时间即可计算出延时缓冲FIFO的读出位;控制FIFO的读出指针,即可同步两种链路数据。

2.3双冗余保护原理

冗余保护是指对系统的重要部分依靠增加软、硬件实现多重备份,当该部分发生故障,能够快速定位故障,并自动完成对故障部分的替换。

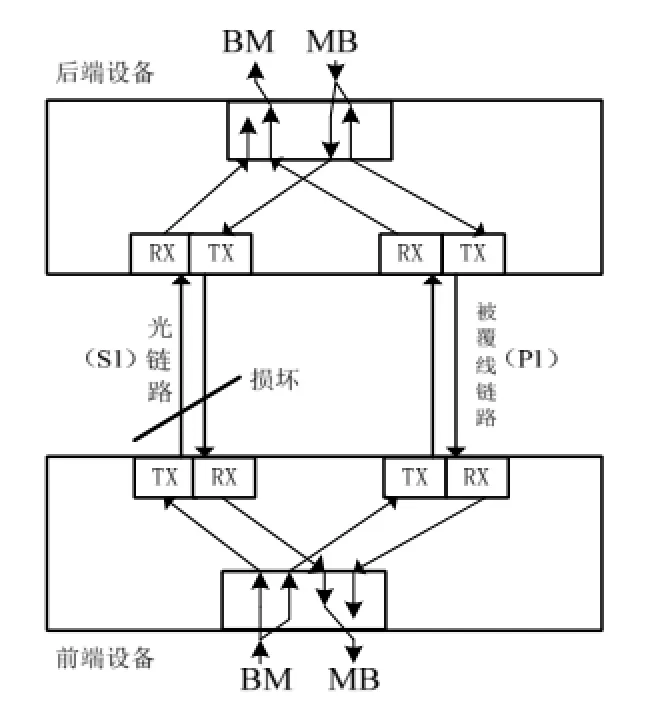

本系统中,传输链路即为系统的重要部分,光链路和被覆线链路互为冗余保护。系统基于“并发优收”的原则,后端设备通过监测传输链路品质,通过仲裁控制器,自动完成传输链路的切换。冗余保护示意图如图2所示。

图2 保护倒换环示意图

系统正常工作时信号同时馈入工作通路S1和保护通路P1;接收侧同时收到工作通路S1和保护通路P1两个通道信号,按其信号的优劣来选择一路作为接收信号。当S1链路损坏后,接收侧按并发优收原则自动倒换到接收链路P1,从而实现了数据传输链路的保护。

3 硬件设计

3.1硬件总体设计

根据系统的整体要求,系统由后端机和前端机构成,数据可实现双向传输。系统硬件结构主要包括光传输模块、被覆线传输模块、链路监测、链路仲裁、链路倒换、延时缓冲等,其中链路监测、仲裁倒换由FPGA内部状态机控制,具有结构简单、切换时间短等诸多优点;延时同步缓冲通过FPGA内部FIFO实现,简化了硬件结构。

3.2光传输模块设计

光传输模块采用TI公司的TLKl501作为并串转换器,串行使用SFF光模块完成光电互转换。其电路图如图3所示。

图3 光传输模块电路图

TLKl50l主要完成数据并串转换、串并转换及时钟处理功能。TLKl50l支持16位的并行接口,并行数据时钟30~75 MHz。并行数据通过8B/10B编码为20位编码数据,再通过并串转换发送出去。串行数据的速率为600M~1.5 Gbps,本系统中并行时钟选用50MHz。

TLKl50l芯片是光传输模块的核心,因此良好的设计、控制是该模块的关键。TLKl50l芯片是高速的千兆串行收发器件,对时钟的要求比较高,发送和接收时钟需要严格的同频,频差需要控制在O.01%内,时钟的抖动小于40ps。接收同步时TLKl50l都是通过检测1DLE7状态下的K28.5码来进行同步的。可通过控制TLKl50l LCKREFN脚控制接收侧进入同步捕获模式,从而实现接收侧快速进入同步状态。

3.3被覆线传输模块设计

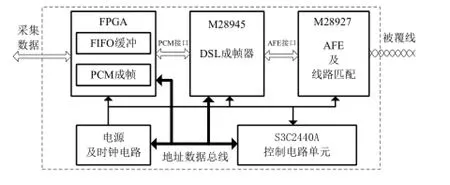

被覆线传输模块采用国际电信联盟(ITU)规范G.SHDSL技术。利用TC-PAM编码方式,单线对净负荷传输速率可在192Kbps 至2312Kbps范围内变化,传输距离更远。本系统中采用净负荷传输速率为192Kbps,传输距离可达8公里。其基本传输结构图如图4所示。

该模块基于敏迅公司开发的M28945、M28927芯片组基础上,使用SAMAUNG公司S3C2440A处理器作为主控制器,使用FPGA完成采样数据到PCM数据成帧。其中,M28945为DSL成帧芯片,M28927为AFE(模拟前端)芯片。

图4 被覆线模块结构框图

采集数据接首先在FPGA使用FIFO完成同步缓冲,在经过数据成帧为192Kbps串行PCM数据。S3C2440A处理器完成M28945的API底层操作码加载、接口配置及状态信息读取。M28945芯片完成PCM数到DSL成帧及TC-PAM16编码的DSP模块。M28927为系统模拟前端芯片,主要完成数字信号与SHDSL信号的转换,即D/A和A/D变换、信号滤波、增益控制和线路驱动输出。

4 FPGA逻辑模块设计

系统中FPGA采用XILINX公司SPARTAN-6系列,逻辑模块设计采用VHDL语言为硬件描述语言,采用模块化设计原则。整个工程分为前端机工程和后端机工程,

前端机工程:主要实现采样数据并串转换的转换,然后将串行数据和状态信息成帧一路PCM数据;接收控制指令和监测倒换信号完成传输链路切换及回环控制。

后端机工程:主要完成PCM数据的帧同步提取、采样数据提取、远端状态信息提取;同时完成链路监测仲裁及倒换控制、链路延时测定、延时同步缓冲等功能。

5 系统调试

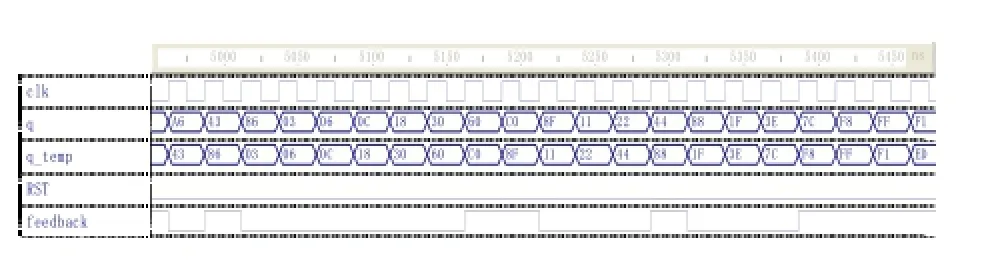

在系统调试过程中,将前端机和后端机使用30公里光纤和8公路被覆线进行连接。采集数据输入端接入模拟数据源,使用示波器观察和Xilinx在线逻辑分析仪捕获分析相结合的方式进行调试。使用线逻辑分析仪捕获结果如图5所示。

图5 光链路和被覆线链路传输对比图

通过试验,某一传输链路切断后,系统自动切换到另一链路,采集数据传输正常。通过测定链路延时时间可实现采集数据同步输出。

6 结束语

该采集传输系统目前已应用于某高可靠探测信号传输中,在实际应用中,可自动或手动切换传输路径,采集数据传输正常,保证了传输链路可靠性。同时,利用链路延时测量、同步缓冲等技术,实现同一时刻采集数据经不同传输链路后的同步输出,为后续数据处理带来极大的方便。

[1] 孙秀娟.基于双模冗余容错技术的数据采集系统设计[J].电测与仪表,2008,45(8):49-52.

[2] 于明,范书瑞,曾祥烨.ARM9 嵌入式系统设计与开发教程[M].北京:电子工业出版社,2006.

[3] 于爽.SDH自愈网原理[J].计算机光盘软件与应用,2011(18): 89-91.

Design of dual redundant data collective transmission system based on optical link and phone link

In order to improve the reliability of data transmission, this paper presents a hot backup transmission based on optical link and phone link. The system has multiple functions such as: dual redundancy protection link, real-time check and control the channel,switching channel by arbitrating the collection result of two link transmission quality. The collective data of tow transmission channel is output delayed by FIFO. The paper introduces delay synchronous theory, present the hardware and software design in detail.

Optical link; phone line; dual redundancy; protection switching

TP393.03

A

1008-1151(2016)04-0006-03

2016-03-11

臧习飞(1979-),男,中国电子科技集团公司第三十四研究所工程师,从事光通信、光器件、传输系统集成等研究工作。