压缩感知硬件结构的能耗评估

2016-10-20裴志军王雅欣

裴志军,王雅欣

(天津职业技术师范大学电子工程学院,天津300222)

压缩感知硬件结构的能耗评估

裴志军,王雅欣

(天津职业技术师范大学电子工程学院,天津300222)

针对在医学监护等低功耗低速率应用中,传感器节点有苛刻的能耗限值和传输带宽限制等问题,通过构建基于压缩感知数据压缩的传感器节点全信号捕获链系统的能耗模型框架,对不同压缩感知硬件结构的能量效率进行分析评估。研究表明:在数据传输能耗占主导的情况下,模拟压缩感知方法比数字压缩感知方法具有更好的能量效率,但硬件复杂性更高;在信号捕获处理占主导的情况下,与模拟压缩感知方法相比,数字压缩感知方法基于能量有效的数字逻辑,系统能量效率更高,适合于传感器节点应用的数据压缩。

压缩感知;硬件结构;能耗评估;传感器节点;低功耗

近年来,压缩感知(compressed sensing,CS)技术及其应用已引起人们广泛的研究兴趣[1-2]。与基于香浓采样定理的传统信号采样处理相比,压缩感知技术存在诸多优点。一方面,压缩感知能够以信号的亚奈奎斯特率采样,在宽带信号处理的高速率应用领域中,有效降低了对模数转换器件高采样率的苛刻要求。另一方面,压缩感知将稀疏的高维数据矢量投影到一个低维空间,减少了信号处理的数据量,在传感器节点数据压缩的低速率应用领域中,降低了数据存储或传输的能耗。虽然,大量研究工作已对高速率应用领域的压缩感知技术进行了深入有益的探讨[3],但在低速率、低功耗的应用领域,如医学监护、环境监测等,能量有效的压缩感知技术近年来才开始受到关注[4]。这些应用领域所面临的技术挑战与传感器节点的严格能耗限制密切相关,往往期望传感器节点具有10年或更长的寿命,而减少传输数据量是获得较长系统寿命的关键[5]。因而,能量有效的压缩感知技术对低速率、低功耗应用系统的数据压缩尤为重要。压缩感知的相关研究中提出了各种硬件实现结构[6],但不同硬件结构能耗不同。因此,本文对低速率应用领域的压缩感知硬件结构的能耗评估技术进行分析探讨。

1 基于压缩感知的数据压缩

传统的信号数据捕获处理要求采样率大于信号最高频率的2倍,即奈奎斯特率采样,而压缩感知理论充分利用信号结构来捕获采样数据,能以正比于信息率而不是信号频率的速率采样[7]。当信号具有相对于带宽而言较低的信息率时,意味着基于压缩感知可以获得比传统奈奎斯特率采样更少的采样数据。在有着苛刻功耗限值的医学监护应用领域,可穿戴或植入式传感器节点需要捕获和传输大量的数据,而许多生物医学信号所要求的奈奎斯特采样率远大于信息率,即事件发生的频率,因此压缩感知方法可以应用于生物信号的数据压缩[8]。压缩感知降低了对模数转换器(analog digital converter,ADC)和随后数字处理的要求,有效减少了存储或传输的数据量,因而非常适合于移动可穿戴低功耗系统的数据压缩。传统典型的医学监护传感器节点电路结构包括基于ADC的信号捕获采样、数据压缩处理及无线发射3个主要的能耗源模块[5]。压缩感知将压缩和采样有机结合,免除了独立的数据压缩模块,且亚奈奎斯特率采样减少了存储或无线发射的数据量,从而降低了系统的整体功耗。

压缩感知CS与传统数据捕获与压缩方法的比较如图1所示,其中包括无数据压缩处理的ADC方式、信源编码压缩方式、滤波或分类的信号处理方式。与传统的数据捕获和压缩方法相比,基于压缩感知的传感器节点系统将数据捕获和压缩相结合,能够实现正比于信息内容的数据压缩,且性能可与信源编码方法相比较,同时具有灵活通用的类似ADC界面,使同一硬件界面能够适合不同应用,降低了存储或数据传输的能耗成本。另外,尽管信号的压缩感知重构的计算要求高于其他数据压缩技术,但在诸如动态医学监护应用系统中,信号重构可以采用对能耗成本限制较少的离线方式执行。

图1 CS与不同数据捕获和压缩方法的比较

2 压缩感知硬件结构

压缩感知的数学框可表示为:

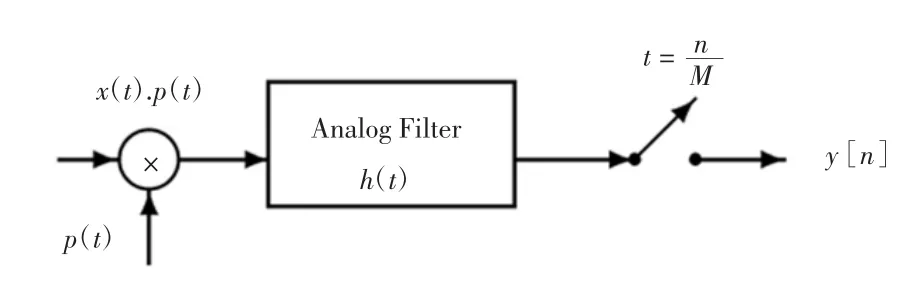

式中:Φ∈RM×N为满足有限等距性质(restricted isometry property,RIP)条件的随机投影感知矩阵;x∈RN为高维稀疏输入信号;y∈RM为随机投影获得的压缩感知采样,M<N。随着压缩感知技术相关研究的不断深入,压缩感知硬件的开发越来越受到关注。文献[4]中提出压缩感知CS硬件结构可分为模拟CS和数字CS两种主要方法。在数字CS方法中,压缩采样测量在奈奎斯特率采样后的数字域获得。而在模拟CS方法中,压缩采样测量在数字化前的模拟域获得。模拟CS方法的硬件捕获系统通常是随机解调器(random demodulator,RD)结构的变化。RD结构主要由混频器(或解调器)、积分器和ADC三部分组成,RD结构的模拟压缩感知CS如图2所示。混频器将一个伪随机序列与输入信号相乘,对应于输入信号与感知矩阵元素的相乘,必须以奈奎斯特率速率执行。低通滤波器(或积分器)将混频器的输出累加,从而获得压缩采样测量样值。之后,ADC器件以亚奈奎斯特率采样。

图2 RD结构的模拟压缩感知CS

然而,在RD结构中,感知矩阵的所有行采用同一随机序列,难以保证最小的相关性。一个通常采用的实际压缩感知硬件执行由并行的RD模块组成,称随机调制预积分(random modulation pre-integrator,RMPI),如图3所示。RMPI结构中,输入信号能够被不同的随机序列相乘,并行的每一个RD模块产生各自独立的压缩采样测量,因而增加了不相关性。RMPI结构进一步减少对ADC器件的要求,但要求使用更多的以奈斯特率工作的累加器和混频器。模拟CS方法中,设计的主要问题是并行的通道设计,通常通道数目等于期望的压缩采样测量数目,而随着并行通道数目的增加,系统整体功耗持续增加。

在低功耗、低速率的应用领域,压缩感知硬件执行面临许多挑战,硬件结构的选择依赖于数据压缩的低功耗能量效率,压缩感知电路本身的能耗不应大于数据压缩所节省的能耗。文献[5]基于无线传感器节点应用,深入分析了压缩感知硬件结构的模拟方法执行和数字方法执行。模拟CS方法执行中采用了RMPI结构;数字CS方法中,硬件系统结构由放大器和ADC及随后执行矩阵乘运算的累加器和门电路组成。通过基于硬件电路系统的功耗比较表明,对于要求高增益和中高分辨率的无线传感器应用,数字压缩感知方法比模拟压缩感知方法更能量有效。由于文献[5]并没有考虑数据传输的能耗,但在诸如医学监测的应用系统中数据传输能耗往往占主导,因而应当通过包括数据传输或存储的全信号处理链系统来评估压缩感知硬件结构的能量效率。

图3 RMPI结构的压缩感知CS

3 压缩感知硬件结构能耗模型

在基于压缩感知的数据压缩中,为分析评估压缩感知硬件结构的能耗,考虑传感器节点信号捕获的全信号链系统,建立不同结构的能耗模型框架进行分析比较。为便于分析,将系统分为捕获前端(front-end,FE)和存储或发射后端(back-end,BE),如图4所示。

图4 基于CS的传感器节点信号捕获系统

前端FE包括与信号的捕获、调整和数字化以及随机调制相关的所有电路,主要电路单元包括低噪声放大器(low noise amplifiers,LNA)、混频器(mixers,MI)和积分器(integrators,INT)、模数转换器(analog-todigital converter,ADC)、数字信号处理电路(digital signal processing circuits,DSP)、存储矩阵及任何中间或最终结果的数字存储器(memory,MEM)。后端BE仅包括存储或数据发射硬件,考虑2个BE选择,即直接的无线数据发射W或非挥发性存储器(non-volatile memory,NVM)暂时存储。一个完整的信号捕获系统可通过将不同的FE与BE组合获得。分析中将奈奎斯特系统结构作为基于CS的FE选择比较参考。图4中(a)为奈奎斯特率信号捕获、(b)为模拟CS编码器、(c)为数字CS编码器。首先分析系统单元功耗估计模型,然后将这些模型组合成不同的系统结构框架,以进行功耗的评估和比较。

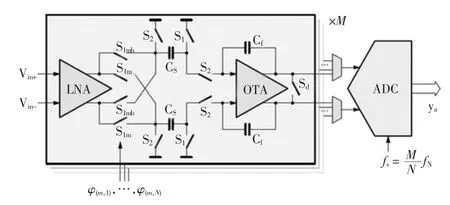

模拟CS编码的差分开关电容级电路图如图5所示。模拟编码器由M个并行的随机调制器通道构成,每个通道包括一个LNA、一个混频器和采样器的组合以及基于运算夸导放大器(operational transconductance amplifier,OTA)的积分器电路。测量矩阵元素采用系数±1,使乘法能够通过简单开关输入信号的极性实现。混频器和采样器组合由开关S1m、S1mb、S2m、S2mb与开关S1、S2及电容组成。

图5 模拟CS编码器电路

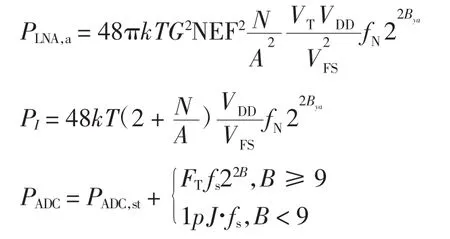

经分析可获得LNA、积分器和ADC的功耗估计分别为:

式中:NEF(noise efficiency factor)为LNA的噪声效率因子;G为LNA电压增益;A=Cf/Cs;VDD为电源电压;FN为信号奈奎斯特频率;FT为ADC热品质因数(figure-of-merit,FOM)。

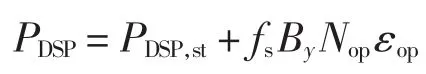

数字CS编码的开关电容级电路如图6所示。获得压缩采样测量的数字信号处理DSP包括乘-累加操作(multiply-add-accumulate,MAC)。DSP部分的功耗估计为:

式中:Nop为运算数目;PDSP,st为电路空闲时DSP的静态功耗;εop为每位MAC运算操作的能量。DSP可采用能量有效的CMOS技术数字集成电路执行。测量矩阵由±1元素构成,使得能够采用简单改变符号实现乘法运算。

图6 数字CS编码器电路

一个压缩感知信号捕获系统必须提供压缩采样测量和测量矩阵Φ的存储。向一个特定存储器件写的位能量成本为εw,则CMOS技术的存储器估计功耗为:

式中:假设εr≈εw;fr为BΦ位字长系统读的速率;Pm,st为存储器宏的待命功耗。

与特定应用相关,前端FE捕获的数据可通过无线发射或存储读出,则后端BE的估计功耗为:

式中:ε{w,tx}为基于存储或发射的位能量成本;f{W,tx}为写操作或无线发射的速率。

应用上述各功能单元的能耗功估计模型,可构成不同结构捕获系统的系统估计功耗模型框架。奈奎斯特结构(Nyquist architecture,NYQ)、模拟CS结构(analog CS architecture,ACS)和数字CS结构(digital CS architecture,DCS)的系统估计功耗可分别表示为:

应用获得的不同结构的系统估计功耗框架,基于综合的工艺电路设计参数,对不同结构系统的能量效率进行评估比较,可选择最适合于应用的压缩感知CS硬件结构。

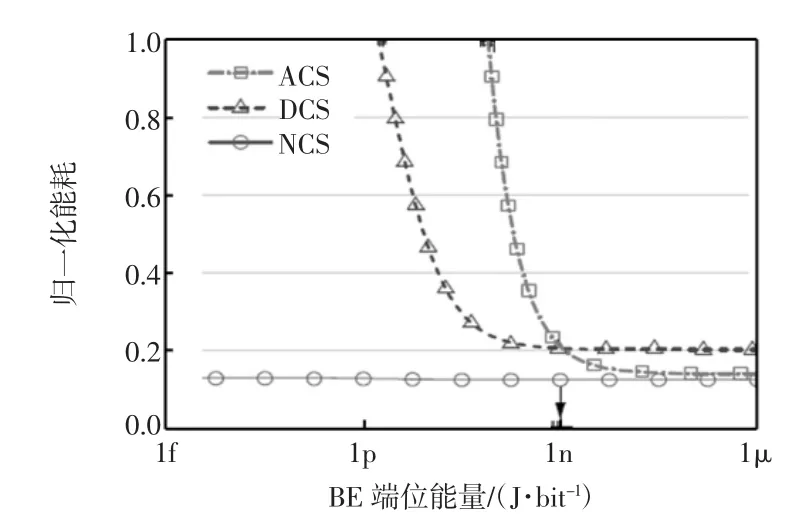

压缩感知硬件结构理论上可采用模拟CS和数字CS两种方式,相关文献做了许多有意义的工作。在低功耗、低速率应用中,通过压缩感知技术进行数据压缩所节省的能耗应不超过电路本身所消耗的能耗。通过上述构建系统功耗模型框架,可对不同压缩感知硬件结构的能量效率进行评估和比较。文献[6]在给定的工艺和电路综合参数下,分析比较了不同压缩感知结构的能耗,如图7所示。在图7右侧,在后端BE功耗较大且占主导的情况下,模拟CS编码器比数字CS编码器可获得更好的压缩性能,从而具有更好的能量效率,但ADC前的模拟电路更复杂,也即产生更高的功耗。在图7左侧,后端BE功耗较小,在中高分辨率及前端FE能耗占主导的情况下,数字CS具有更明显优势,数据压缩宜采用数字CS方法。

图7 不同CS结构能耗评估

4 结束语

压缩感知硬件结构从理论上可采用模拟采样和数字压缩采样2种方法,本文通过构建基于2种不同方法的全信号链信号捕获功耗估计框架模型,基于综合的工艺和电路参数集合,对系统的能量效率进行评估比较,选取适合于特定应用的能量有效的压缩感知硬件结构。全信号捕获链可分为前端FE和后端BE两部分,在后端功耗占主导情况下,模拟压缩感知方法比数字压缩感知方法具有更好的能量效率,但要求更高分辨率的量化器,会使ADC前的模拟电路产生更高的功耗;而在中高分辨率及前端能耗占主导情况,数字压缩采样方法具有更明显优势,更适合于信号的数据压缩。压缩感知硬件结构的能耗评估技术可应用于体域网中移动可穿戴低功耗传感器节点数据压缩系统的设计开发,以及其他相关的无线传感器节点数据压缩应用领域。

[1]焦李成,杨淑媛,刘芳,等.压缩感知回顾与展望[J].电子学报,2011,39(7):1651-1662.

[2]DUARTE M F,ELDAR Y C.Structured compressed sensing:From theory to applications[J].IEEE Transactions on Signal Processing,2011,59(9):4053-4085.

[3]GISHKORI S,LEUS G.Compressive sampling based energy detection of ultra-wide band pulse position modulation[J]. IEEE Transactions on Signal Processing,2013,61(15):3866-3879.

[4]CRAVEN D,MCGINLEY B,KILMARTIN L,et al.Com-pressed sensing for bioelectric signals:A review[J].IEEE Journal of Biomedical and Health Informatics,2015,19(2):529-540.

[5]CHEN F,CHANDRAKASAN A P,STOJANOVIC V M.Design and analysis of a hardware-efficient compressed sensing architecture for data compression in wireless sensors[J]. IEEE Journal of Solid State Circuits,2012,47(3):744-756.

[6]BELLASI D E,BENINI L.Energy efficiency analysis of analog and digital compressive sensing in wireless sensors[J]. IEEE Transactions on Circuits and Systems-I:Regular Papers,2015,62(11):2718-2729.

[7]DONOHO D L.Compressed sensing[J].IEEE Transactions on Information Theory,2006,52(4):1289-1306.

[8]ZHANG J,MITRA S,SUO Y,et al.A closed loop compressive sensing based neural recording system[J].Journal of Neural Engineering,2015,12(3):1741-2552.

Energy consumption evaluation of hardware architecture of compressed sensing

PEI Zhi-jun,WANG Ya-xin

(School of Electronic Engineering,Tianjin University of Technology and Education,Tianjin 300222,China)

In the applications of low power consumption and low speed,such as medical monitoring,sensor nodes have strict limits on energy consumption and transmission bandwidth.By constructing the energy consumption model framework of the sensor nodes of full signal acquisition chain system based on compressed sensing data compression,the energy efficiency of different compressed sensing hardware structure is analyzed and evaluated in this paper.In the case of data transmission energy consumption,the analog method has better energy efficiency than the digital compression method,but the hardware is more complex.In signal acquisition processing dominated applications,compared with analog compressed sensing method is compared,digital compressed sensing method based on energy efficient digital logic has higher system energy efficiency,which is suitable for data compression of sensor node application.

compressed sensing;hardware architecture;energy consumption evaluation;sensor node;low power consumption

TP332

A

2095-0926(2016)02-0015-04

2016-03-21

天津市自然科学基金资助项目(15JCYBJC52200).

裴志军(1967—),男,教授,研究方向为信息获取与处理、专用集成电路设计.