基于AXI4-Stream总线的数字视频接口IP核设计

2016-10-17郑建立漆荣辉

郑建立,漆荣辉,张 璐

(上海理工大学 医疗器械与食品学院,上海 200093)

基于AXI4-Stream总线的数字视频接口IP核设计

郑建立,漆荣辉,张璐

(上海理工大学 医疗器械与食品学院,上海 200093)

针对数字视频IP核间高速流数据传输,设计并实现了一种基于AXI4-Stream总线的数字视频接口IP核,对外部输入ITU601格式的数字视频信号,将其格式转化为符合AXI4-Stream总线协议的信号,并通过IP核的主端口输出到下一级IP核的从端口。采用XilinxISEDesignSuite14.6软件综合设计实现,结合ISE自带ISim软件完成功能仿真,通过实际硬件电路验证了设计的正确性及可行性。

AXI4-Stream;数字视频信号;IP核

在SOC系统设计中,高级微控制器总线结构(AdvancedMicrocontrollerBusArchitecture,AMBA)被广泛采用,已经迅速成为SOC结构和IP核开发的标准[1]。AXI4、AXI4-Lite、AXI4-Stream这3种总线标准是AMBA第4版的重要组成部分。AXI4总线有助于最大化性能和能效;AXI4-Lite总线和AXI4-Stream总线是FPGA实现的理想选择。AMBA4.0总线是标准接口规范,由多家企业共同为行业而设定,包括业界领先的OEM厂商、半导体及EDA供应商等[2],可确保不同IP核的兼容,加快SOC设计效率。

本文在深入分析和研究AXI4-Stream总线协议的基础上,通过VHDL硬件描述语言实现了对ITU601格式的数字视频输入信号转化为符合AXI4-Stream协议的视频输出信号,并通过ISim软件仿真及在基于XilinxZynq7000芯片设计的内窥镜视频处理系统电路上得到验证。

1 AX I4-Stream总线协议

AXI4-Stream总线是以突发传输为机制并没有突发长度限制的总线[3]。总线采用握手机制实现数据的收发,没有地址通道,没有读写使能,一般情况均是写数据从主设备到从设备的传输。AXI4-Stream总线接口协议主要面向高速流数据传输,可用于连接一个产生数据的主机和一个接受数据的从机,当然也可用于连接多个主机和从机。该协议支持多种数据流使用相同共享总线集合,允许建立能执行扩展、压缩和路由的互联结构[4]。

1.1AXI4-Stream 总线接口信号说明

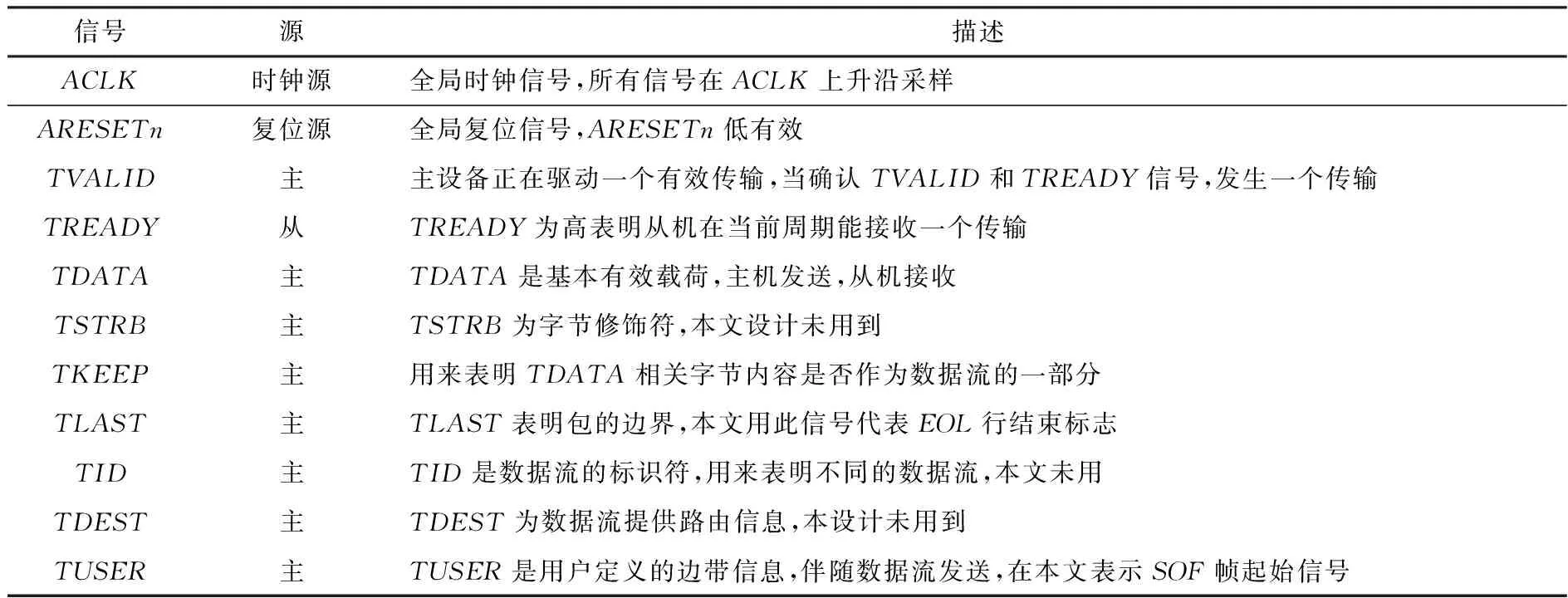

AXI4-Stream接口支持诸多不同的流类型。流协议在传输和包之间定义了联系。表1 介绍了AXI4-Stream接口的信号定义。

表1 AXI4-Stream总线信号说明

1.2AXl4-Stream总线协议信号与时序的关系

TVALID和TREADY握手信号用来确定跨越接口数据的时间。双向流控制机制使得主设备和从设备能控制跨越接口所发送的数据和控制信息的速度。对于一个发生的传输,必须确认TVALID和TREADY信号。一个主设备不允许在确认TVALID前等待确认TREADY。一旦确认TVALID,必须一直保持这个状态,直到产生握手信号。在确认相应的TREADY信号前,一个从设备允许等待确认TVALID。如果从设备确认了TREADY,在TVALID信号确认前,允许不确认TREADY[5]。

AXI4-Stream协议中的TLAST和TUSER信号在本文设计的IP核中分别以EOL和SOF表示,当一行像素传输到最后一个像素时EOL信号置高电平有效,表示一行像素的结束,EOL脉冲宽度为一个时钟周期;SOF帧起始标志表示一帧视频的第一个像素开始传输,一般当作帧同步信号,在TVALID信号没有置位且第一个像素没到来之前SOF的脉宽可是任意个时钟周期[6]。

图1为AXl4-Stream总线协议的TREADY和TVALID握手信号及EOL、SOF标志信号的时序关系图,从图中可看出,从设备在数据和控制信号有效前驱动TREADY信号为高。表明目的设备能在一个ACLK周期内接收数据和控制信息。在此种情况下,一旦主机确认TVALID信号为高,则在时钟周期ACLK的上升沿数据就开始传输。当一行最后一个像素数据传输时EOL信号置高一个时钟周期,表明一行传输完毕。当一帧视频的第一个像素开始传输时SOF帧起始标志位置高电平。

图1 主从设备握手信号及传输波形时序图

2 视频接口IP核设计与实现

在充分研究了外部输入的数字视频格式和AXI4-Stream总线协议的基础上,本文采用VHDL硬件描述语言实现了对外部输入ITU601格式的数字视频转化为符合AXI4-Stream总线协议的视频输出IP核。

2.1ITU601格式数字视频输入

ITU60l是长宽比为16:9和4:3的数字电视信号标准,其对数字电视的各项参数进行了详细的规范和描述[7]。我国通常采用4:2:2采样格式、PAL制式、长宽比为4:3的数字电视信号[8]。本文所用到的外部输入视频信号正是这一格式的信号。其主要特征包括:(1)有3个正交分量:亮度分量Y、色度分量U和V;(2)25帧/s的帧率,每帧两场,每帧扫描625行;(3)对于亮度分量Y,每行抽样864,对于色度分量每行抽样432次;(4)有3个信号用于同步数据分别是:行同步hsync(15 625Hz)、场同步vsync(50Hz)、像素数据同步时钟clk(13.5MHz)。包括消隐期在内,每帧数据扫描625行,每行抽样864个像素点,因此总分辨率为864×625。一帧数据又包含奇偶两场,从上一帧的624行到本帧的310行是奇场,其中上一帧的624行到本帧的22行是奇场消隐期,从23行到310行是奇场有效行;从本帧311行到623行是偶场,其中311~335行是偶场消隐期,从336~623行为偶场有效行数据。对于帧内的每一行,共有864个像素,其中从第0个到第719个为有效像素。共计720个点,从720~863个为消隐期像素。每个象素都抽取Y分量,每两个像素则抽取一个U分量和一个V分量。

2.2ITU601 to AXI4-stream IP核设计实现

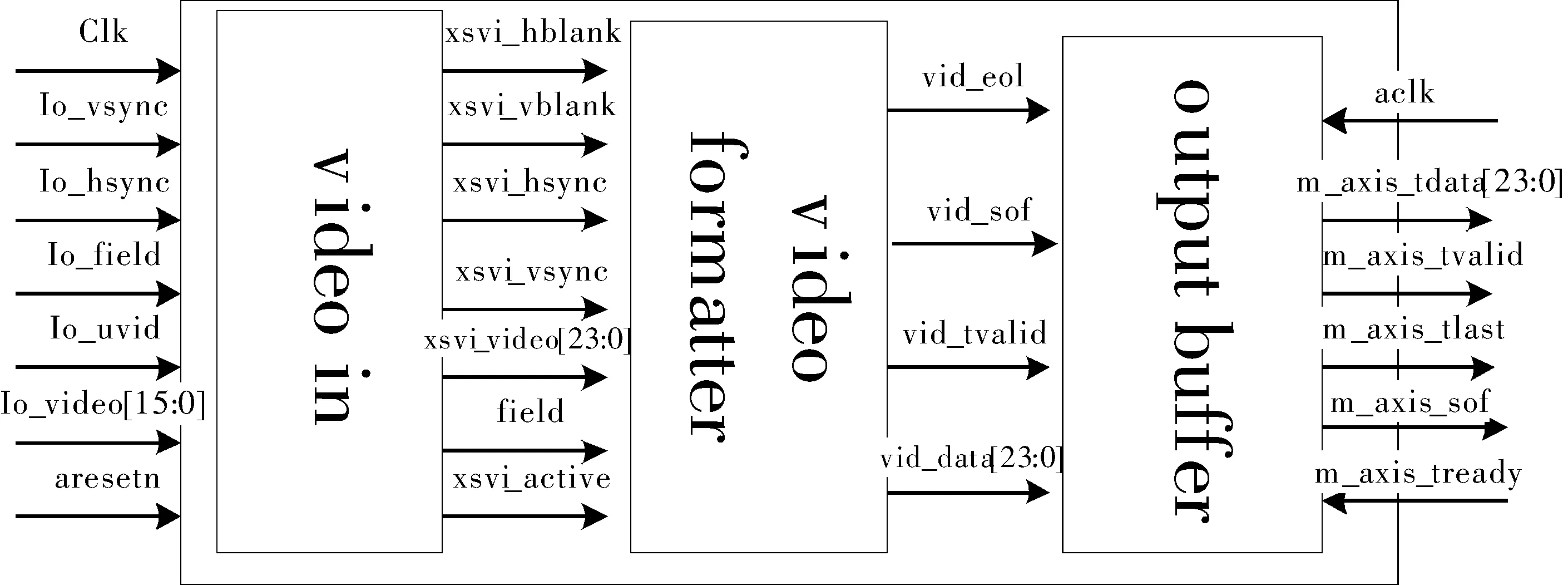

ITU601toAXI4-streamIPCore接口及内部各模块间主要信号传递如图2所示,其中clk为外部输入视频的像素时钟信号13.5,MHz、io_vsync为外部视频场同步信号,io_hsync为外部输入视频行同步信号,io_field为外部视频奇偶场标志信号,io_uvid为外部输入视频UV信号的标志,io_video[15:0]为输入16位数字视频信号,视频数据格式为YUV422。IP核视频输出主接口为符合AXI4-Stream协议的总线接口M_AXIS_VIDEO,其中包括系统数据读写时钟信号aclk,在本文的验证实验中此系统时钟为150MHz,m_axis_tdata[23:0] 24位宽的视频数据总线,m_axis_tvalid为主机数据同步信号,为高电平表示主机准备好发送数据,m_axis_tlast为主机最后一个字指示,在该IP中表示视频数据一行的结束即eol信号,m_axis_sof表示一帧视频数据的开始,m_axis_tready为从机数据同步信号,其值为高表示从机准备好接收数据。TVALID、TREADY这两根信号线完成了主机与从机的握手信号,一旦二者都置高有效,则数据流开始传输。

图2 ITU601 to AXI4-stream IP接口及内部模块结构

IP核内部3个主要的模块都采用VHDL语言设计而成。videoin模块是一个视频输入接口,根据输入视频信号时序将YUV422 16位宽的信号转化为YUV444 24位宽的视频信号。videoformatter模块是视频协议转换的核心模块,完成视频格式转化,通过对输入视频时序分析产生一行结束标志(eol)即vid_eol,帧起始标志(sof)即vid_sof,以及主机握手信号vid_tvalid。通过该模块后输出的视频数据格式就符合AXI4-stream总线协议规范。主要实现代码如下

io_iregs_1:process(Clk)

begin

ifrising_Edge(Clk)then

vsync_1 <=xsvi_vsync;

vsync_2 <=vsync_1;

de_1 <=xsvi_active;

de_2 <=de_1;

de_3 <=de_2;

data_1 <=xsvi_video;

data_2 <=data_1;

data_3 <=data_2;

eol<=de_falling;

sof<=de_risingandvert_blanking_intvl;

sof_1 <=sof;

endif;

endprocess;

io_iregs_2 :process(Clk)

begin

iffalling_Edge(Clk)then

if(vsync_rising= '1')then//risingedgeofvsync

vert_blanking_intvl<=notfield; //field=1:odd0:even

elsif(de_falling= '1')then//fallingedgeofdataenable

vert_blanking_intvl<= '0';

else

vert_blanking_intvl<=vert_blanking_intvl;

endif;

endif;

endprocess;

de_rising<=notde_2andde_1; //de_rising保持一个时钟周期高电平

de_falling<=de_2andnotde_1; //de_falling保持一个时钟周期高电平

vsync_rising<=notvsync_2andvsync_1;

vid_data<=data_3;

vid_tvalid<=de_3;

vid_eol<=eol;

vid_sof<=sof_1;

以上VHDL代码的两个进程功能是实现sof、eol及主机握手信号tvalid。如何正确地产生sof是整个设计的难点,帧起始信号sof在每帧视频的第一个有效像素出现时置一个时钟周期高电平且一帧视频数据中sof只产生一次。sof由xsvi_active信号的上升沿和场同步信号xsvi_vsync共同决定。进程io_iregs_2的功能是确保sof在奇场同步信号上升沿到第一个像素时产生,一帧视频分为奇偶两场,sof相当于帧同步,因而只在奇数场的第一个有效像素时产生。eol主要是根据xsvi_active视频数据有效信号的跳变来产生,当xsvi_active为高电平时表示像素数据有效,为低电平表示处于消隐区,所以一行最后一个像素点传输结束时xsvi_active会发生从高电平到低电平的跳变,在进程io_iregs_1中de_falling正是表示xsvi_active从高到低的跳变,故将其赋值给eol。

Outputbuffer模块是输出接口缓存模块,由于视频数据输入的时钟是13.5MHz、输出是150MHz,读写是跨时钟域的,所以在Outputbuffer模块中引入了一组异步FIFO控制模块,使用异步FIFO可在两个不同时钟系统之间快速而方便地传输实时数据。

3 测试与验证

为验证所实现的AXI4-stream接口总线时序的正确性,本文主要采用功能仿真和实际电路测试。

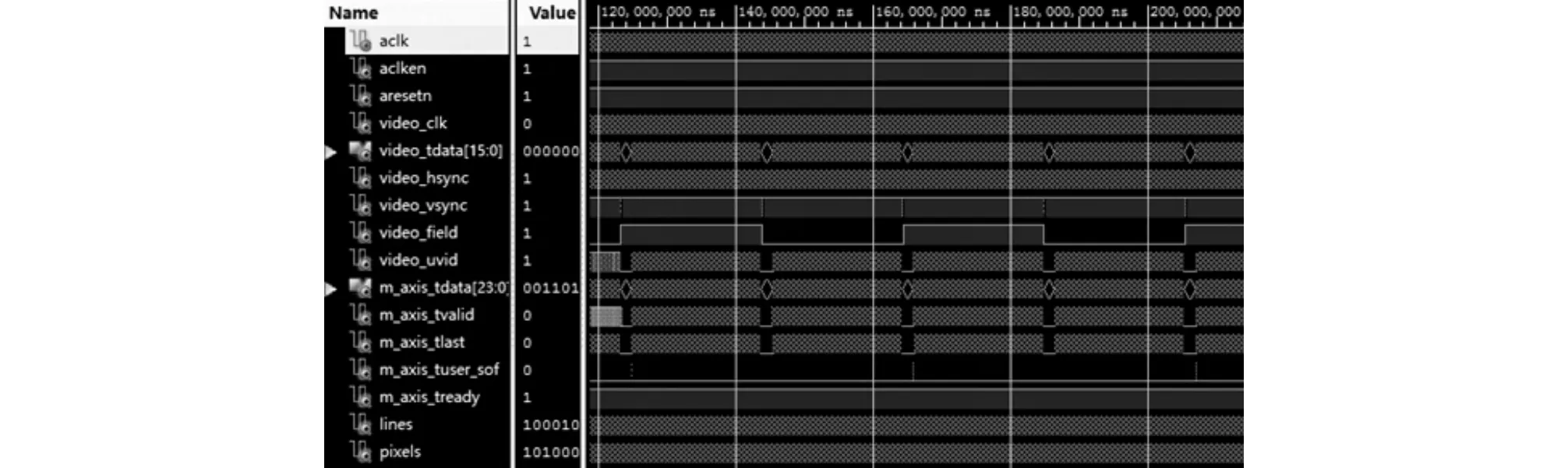

首先进行功能仿真测试,功能仿真采用XilinxISEDesignTools自带的仿真器ISimSimulator,通过VHDL语言编写仿真测试用例,主要是用来验证当外部输入ITU601格式的视频信号后通过视频接口IP核,在该IP核的输出端M_AXIS_VIDEO总线接口时序是否满足AXI4-stream总线时序要求。图3为ITU601toAXI4-streamIP核接口功能仿真时序图,从图中可看出从设备的TREADY(m_axis_tready)信号一直为高电平,等待主机端口传送有效握手信号和数据,每当要传送一个像素点,主端口m_axis_tvalid(Tvalid)就置高电平,完成主从设备握手,在时钟ACLK的上升沿到来时就发生数据传输,当一行720个像素均传送完毕时m_axis_tlast(Tlast)即eol置高电平,表示一行数据传送完毕;由图4可看到IP核输入端视频数据的行同步video_hsync信号,场同步信号video_vsync,在输出端口m_axis_tuser_sof为帧起始标志,奇数场和偶数场合并成一帧,输入端出现了两次场同步信号即奇数场和偶数场video_vsync后,输出端出现一次帧起始标志信号,表明奇数场和偶数场合成一帧。通过功能仿真可验证,所实现的IP核主接口符合AXI4-stream总线时序要求。

图3 ITU601 to AXI4-stream 接口时序1

图4 ITU601 to AXI4-stream 接口时序2

硬件测试平台是一款基于XilinxZynq7000设计的医疗内窥镜,XilinxZynq7000 全可编程SoC(APSoC) 器件集成ARMCortex-A9MPCore处理器的软件可编程性与FPGA的硬件可编程性,不仅可实现重要分析与硬件加速,同时还在单个器件上高度集成CPU、DSP、ASSP以及混合信号功能,Zynq-7000APSoC的这些特性使其在医疗内窥镜、机器视觉、高级驾驶员辅助系统、专业照相机等各种场合都得到了广泛应用[9]。本试验的医疗内窥镜视频处理系统正是基于Zynq-7000APSOC的以上特性设计而成的。该内窥镜CCDcolorCamera拍摄的视频信号经过前期处理板后,输出视频数据格式为ITU601 格式的数字视频信号,此视频信号正是通过ITU601toAXI4-streamIP核视频接口送入基于XilinxZynq7000SOC设计的内窥镜视频处理系统。

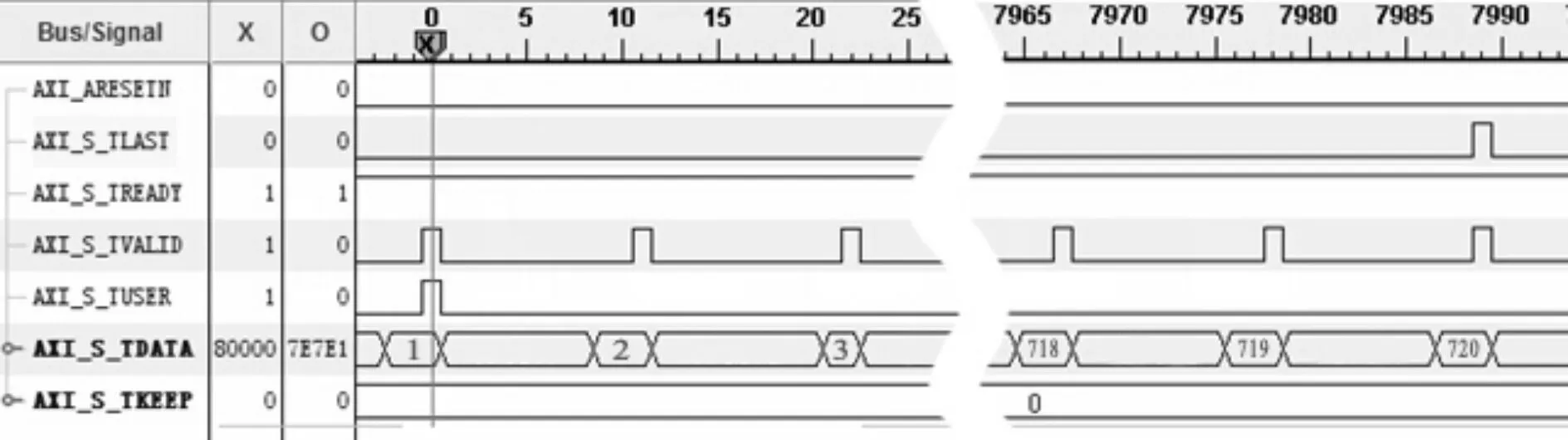

XilinxChipScope工具能够捕获和显示系统设计中实时信号的状态[10],在完成功能验证后,将配置文件下载到内窥镜视频处理系统电路中,利用ChipScope工具可实时捕捉主端口信号并进行时序分析,从而验证所设计的IP核主接口输出信号时序关系是否满足AXI4-stream协议的规定。图 5为利用ChipScope抓取到的IP核主接口信号波形图,从图中可以看出从端口Tready一直为高,等待主端口传送有效数据,当有效像素数据要从主端口传送至从端口时,主端口Tvalid信号就置高电平。axi_s_tuser即sof信号在每帧视频的第一个像素位置出现一次,当一行第720个像素传送时,axi_s_tlast即eol置高电平表示一行的结束。

图5 ITU601 to AXI4-stream IP 核主端口时序

4 结束语

AXI4-Stream总线协议作为嵌入式系统内部高速流数据传输常用的总线协议,得到第三方EDA厂商和IP开发厂商普遍采用[11]。为满足AXI4-Stream总线主从设备间的数据传输,本文通过研究AXI4-Stream总线时序,采用VHDL语言设计并实现了一个视频协议转换IP核,该IP核可将外部输入的ITU601格式视频信号转化为符合AXI4-Stream总线协议的视频输出信号,方便与其他具有AXI4-Stream流接口的IP核进行互联。通过软件仿真及实际硬件电路测试表明本文设计的IP核主接口符合AXI4-Stream总线时序要求,主从设备之间能正确地传输数据,实验视频显示清晰、实时性良好。

[1]蔡晓光.基于AMBA总线SoC的IP核设计与应用[D].西安:西安电子科技大学,2010.

[2]杨舜琪.AMBAAXI4总线的研究与实现[D].哈尔滨:哈尔滨工业大学,2011.

[3]贺理,赵鹤鸣,邵雷.AXI4Stream总线的FPGA视频系统的开发研究[J].单片机与嵌入式系统应用,2015,15(12):42-45.

[4]TanidaH,YoshidaH,FujitaM.EvaluationofFPGAimplementationtechniquesforhigh-performancesoprototypes[J].IeiceTechnicalReportDependableComputing,2010, 110(2):79-84.

[5]何宾.XilinxFPGA设计权威指南[M].北京:清华大学出版社,2014.

[6]钟雪燕,夏前亮,赵德生,等.基于AXI总线的视频数据传输处理的FPGA实现[J].计算机测量与控制,2015,23(11):3825-3827.

[7]严卫健.模拟电视信号数字解码及视频处理研究与设计[D].成都:电子科技大学,2006.

[8]虞卫峰,唐慧明.一种用CPLD实现视频信号运动检测的方法[J].电子技术应用,2004,29(11):64-67.

[9]王莹.Xilinx可扩展处理平台:ZYNQ嵌入式处理器与FPGA集成的独特创举[J].电子产品世界,2012,19(2):27-32.

[10] 曾波.在系统逻辑分析仪的电路设计与实现[D].成都:电子科技大学,2012.

[11] 马飞,刘琦,包斌.基于FPGA的AXI4总线时序设计与实现[J].电子技术应用,2015,41(6):13-15.

Design and Implementation of Video Interface IP Core Based on AXI4-Stream Bus

ZHENGJianli,QIRonghui,ZHANGLu

(SchoolofMedicalInstrumentandFoodEngineering,UniversityofShanghaiforScienceandTechnology,Shanghai200093,China)

ForthehighspeedstreamdatatransmissionbetweentheIPcoreofthedigitalvideo,wedesignandimplementaninterfaceIPcoreofthedigitalvideobasedontheAXI4-Streambus.ThedigitalvideosignalfromtheexternalinputintheITU601formatistranslatedintothesignalconformingwiththebusprotocolofAXI4-Stream,andthenexportedtotheportofthenextlevelIPcorethroughthemainportoftheIPcore.TheaccuracyandfeasibilityoftheproposeddesignhavebeenvalidatedbytheactualhardwarecircuitusingXilinxISEDesignSuite14.6.

AXI4-Stream;digitalvideosignal;IPcore

2015- 12- 21

上海市科委重点科技攻关基金资助项目(11441902302)

郑建立(1965-),男,博士,副教授。研究方向:医学信息集成技术和嵌入式应用。漆荣辉(1988-),男,硕士研究生。研究方向:嵌入式系统及数字化医疗仪器。

10.16180/j.cnki.issn1007-7820.2016.09.045

TN943;TP336

A

1007-7820(2016)09-161-05