DFT与ATPG的低功耗设计原理与分析

2016-10-14丁伟

丁伟

(爱特梅尔半导体科技(上海)有限公司上海200233)

DFT与ATPG的低功耗设计原理与分析

丁伟

(爱特梅尔半导体科技(上海)有限公司上海200233)

文中介绍了在DFT与ATPG阶段均可通过各自的方法来达到降低测试功耗的目的。以实际项目为例,阐述了在DFT过程中分步法的原理,通过此方法可显著降低在Transition测试时的捕获功耗。同时也介绍了SYNOPSYS公司推荐的降低功耗的命令,评估其在ATPG过程中对功耗的影响。在实际项目中,可综合使用这两种方法,从而达到最佳的降低功耗的目的。

分步法;覆盖率;测试向量;设计

随着芯片规模的增大,低功耗不仅是在功能与性能方面对设计者的挑战越来越大,同时对于测试而言,随着SCAN CELL的增多,在SCAN测试时,芯片的功耗也会增大。功耗越大,则芯片的温度升高,导致芯片内部的电性参数发生偏移,扫描链测试失败[1]。这对DFT(Design for Test)以及ATPG(Automatic Test Pattern Generation)提出了更高的挑战。

1 项目中遇到的问题

公司的某个项目在测试扫描链测试向量时遇到了一个问题,既测试结果与期望值不符。通过TetraMax(生成ATPG的工具)对测试向量进行分析,发现测试向量并无问题。后通过测试基台分析,发现芯片在测试的过程中,温度急剧升高,在芯片的部分地方温度超过了85℃,导致了扫描链测试的失败。

基于上述问题,文中引入了2种方法来降低扫描链测试时的功耗。

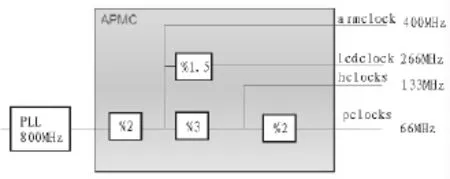

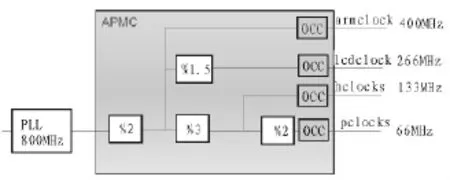

2 分步法

如图1所示,芯片内部分为4个时钟域,分别为ARM(400 Mhz)、LCD(266 MHz)、AHB(133 MHz)以及APB(66 MHz)。对于多时钟域SCAN的测试,按照一般的做法,在SCAN的模式下,直接配置PLL为800 MHz,APMC模块中的分频数值保持不变(与功能模式相同),每个时钟域各自插入异步的OCC,然后生成测试向量,如图2所示[2]。这样的做法优点是操作简单,缺点是时钟域之间的交互连接无法测出,Transition测试覆盖率低(64.277%,低于目标值75%),同时由于测试时各个时钟域的时钟均在工作,根据公式P=CV2f,功耗跟频率成正比,且与电压的平方成正比,在SCAN Transition测试的过程中,捕获时时钟频率高,导致功耗急剧升高,引起MOS管电性参数漂移,使得SCAN测试失败[3]。为解决这一问题,故引入分步法。

图1 芯片时钟域划分

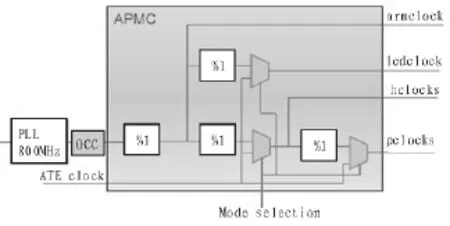

如图3所示,将OCC插入到PLL之后,因有分频器(clock divider)将OCC的时钟分为4个clock域,若用上述提到的传统方法,则4个clock域之间的测试点覆盖不全,同时功耗过高。为此,在电路中将clock divider在scan的模式下,均变为bypass模式,同时在clock divider后面加入时钟选择器(clock mux),如图4所示。时钟选择器将会为lcdclock、hclocks以及pclocks时钟域选择对应的ATE时钟或OCC时钟。

图2 传统控制方法

图3 分步法中OCC结构图

图4 带时钟选择器的结构图

由图5所示,在Mode0的模式下,PLL被配置成400 MHz,此时只有ARM模块部分获得了400 MHz的时钟,因时钟选择器的存在,其余的电路部分得到了ATE(项目中定义为10 MHz)的时钟,由此便可得到在400 MHz的时钟下ARM模块的测试(fault)点,产生Mode0的测试向量。

图5 分步法中Mode0示意图

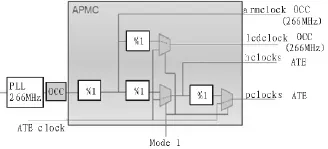

由图6可看出,在Mode1的模式下,PLL被配置为266MHz,此时只有ARM模块跟LCD模块获得了266 MHz的时钟,其余的电路得到ATE的时钟,可得到在266 MHz的时钟下,ARM部分与LCD部分以及ARM与LCD交互部分的测试点。这时,需扣除Mode0中测试到的fault点,然后生成Mode1的测试向量。

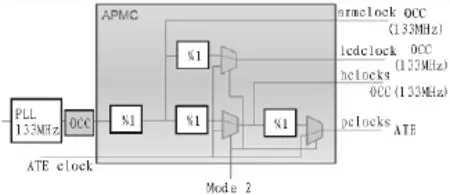

从图7可看出,在Mode2的模式下,PLL被配置为133MHz, ARM模块、LCD模块以及AHB模块获得了133 MHz的时钟,APB模块得到ATE时钟,由此可获得在133 MHz下的测试点(包含了ARM、LCD以及AHB这3大模块之间的连接测试点),在生成Mode2的测试向量时要减去Mode0以及Mode1中已测试到的测试点。

图6 分步法中Mode1示意图

图7 分步法中Mode2示意图

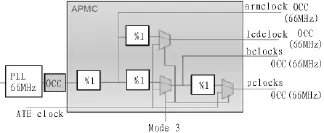

从图8得出,在Mode3的模式下,PLL被配置为66 MHz,所有的模块均获得了66 MHz的时钟,从而可得到所有模块在这一频率下的测试点,再减掉Mode0、Mode1以及Mode2中已测试到的测试点,生成Mode3的测试向量。

图8 分步法中Mode3示意图

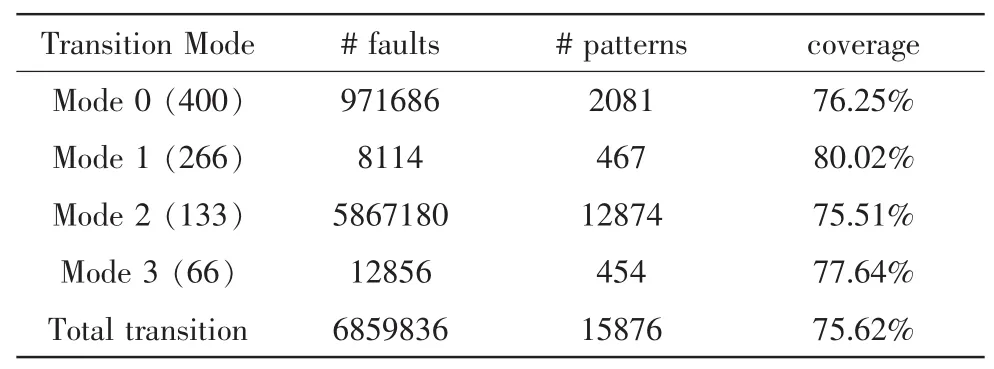

表1 多步法数据统计表

Power Current<300mA

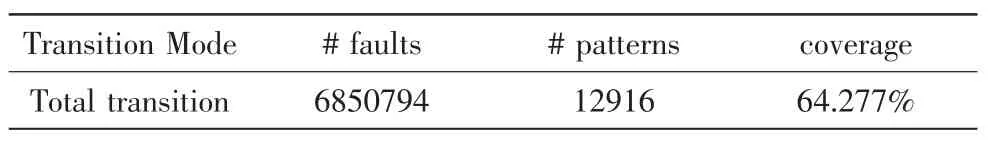

表2 传统方法数据统计表

Power Current>1000mA

从上表1中可看出,使用了多步法后Transition的测试覆盖率为75.62%,高于设定目标值75%,远高于表2中常用方法的64.277%;同时可看出,使用了多步法产生的测试向量数目为15 876,多于传统方法的12 916,说明使用多步法会增加基台在Transition模式下的测试时间。此外,从表1中还可看出,使用多步法后测试电流低于300 mA,低于芯片正常工作的最大电流500 mA,而表2中测试电流大于1000 mA,远大于芯片正常工作的电流值。故使用多步法可降低测试功耗,提高测试覆盖率。但缺点是测试向量增多,导致测试成本增加。

3 SYNOPSYS公司发布的标准降低功耗方法

SYNOPSYS公司对测试向量生成的过程中有方法对shift过程加以干涉。在TetraMax中使用命令“set_atpg╞fill_adjacent╞shift_power_effort_high”,可减少SCAN寄存器翻转的次数,优化测试向量在shift过程中的功耗[4]。

同时还可在扫描链测试向量生成的过程中对捕获(capture)过程加以干涉[4]。在TetraMax的命令行中输入“report_clocks-gating”,以Mode0为例,在Mode0中使用此命令会得到值10.02%。这个值要取整,公式为“power budget= floor(10.02%)+1”。在用于power_budget选项时,数值应为11。使用命令“set_atpg-power_budget 11-power_effort high”,便可获得在捕获时减少功耗的测试向量。

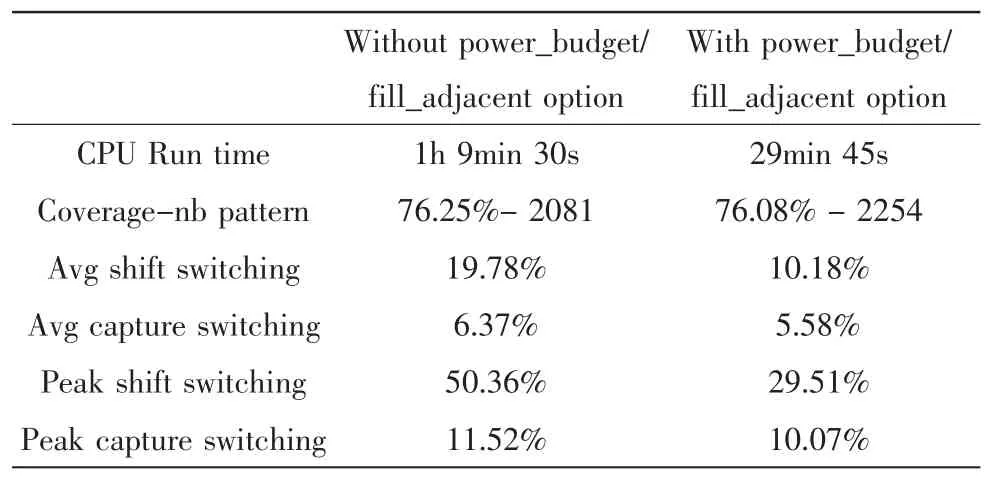

表3 使用SYNOPSYS命令与不使用SYNOPSYS命令的功耗对比

使用上述方法后,从表3中可看出,使用了SYNOPSYS推荐的降低功耗命令选项后,生成扫描链测试向量消耗的CPU Run time显著减少,由1h9min30s减少到29min45s。减少了工作站的负荷,并节省了CPU资源。

同时还可看出,在覆盖率(coverage)为76%左右时,未使用SYNOPSYS推荐命令选项的测试向量数量(pattern数目)少于使用SYNOPSYS推荐命令选项的。测试向量的多少决定了测试基台的测试时间,测试向量数目的增加,必然增加了测试时间及成本。这就需要在功耗、成本之间做出决策,选取最佳平衡点。

表3中还可看出,对于平均shift(Avg shift switching)的功耗,带SYNOPSYS推荐命令选项的相比不带SYNOPSYS推荐命令选项的少,由19.78%降低到10.18%,由此可见SYNOPSYS推荐的命令选项对于降低shift开关的功耗作用明显。

对于平均捕获(Avg capture switching)的功耗,带SYNOPSYS推荐命令的选项为5.58%,比不带SYNOPSYS推荐命令选项的功耗降低了0.79%,功耗降低并不明显。

关于峰值shift(peak shift switching)的功耗,带SYNOPSYS推荐命令选项的比不带SYNOPSYS推荐命令选项的功耗降低了20.85%,效果明显。

对于峰值捕获(peak capture switching)的功耗,带SYNOPSYS推荐命令选项为10.07%,而不带SYNOPSYS推荐命令选项的功耗为11.52%,功耗降低的效果不明显。

由上述可知,SYNOPSYS推荐的降低功耗命令选项对于shift的功耗降低明显,但对捕获的功耗降低则并不明显,同时其缺点还有为了达到相同的覆盖率,测试向量的数量变多,测试成本增加。

4 结束语

多步法可有效的降低芯片在SCAN Transition模式下的功耗(主要是降低了捕获时的功耗),提高测试覆盖率,缺点是测试向量的数量会增多。SYNOPSYS推荐的方法优点在于可直接在TetraMax工具中加入命令,过程简单方便,对shift功耗降低明显,但捕获功耗降低的作用相对较小。可在多步法中结合使用SYNOPSYS推荐的方法,以达到更好降低功耗的目的。

[1]Michael L.Bushnell Vishwani D Agrawal.超大规模集成电路测试[M].蒋安平,冯建华,王新安,译.北京:电子工业出版社,2006.

[2]On-Chip-Clockcontroller(OCC):AnAlternative Approach,SNUG Israel 2012.

[3]Using Custom OCC with TetraMax for At-speed Transition Fault testing and Small Delay Defect,SNUG France,2011.

[4]Synopsys Tetramax 2012.06-SP5 User Guidehttps://solvnet. synopsys.com/dow_retrieve/latest/tmax/tmax_olh/Default_CSH. htm.

[5]王巍.多时钟域ASIC的可测性设计[J].集成电路应用,2001(6):26-29.

[6]赵晓海.跨时钟域信号的几种同步方法研究[J].电子设计工程,2012(7):139-143,147.

DFT and ATPG low power design algorithm and analysis

DING Wei

(Atmel Semiconductor Technology(Shanghai)Co.,Ltd.,Shanghai 200233,China)

This paper introduces separate methods to reduce power consumption during DFT and ATPG.This paper indicates algorithm of multi-step method during DFT by taking real project as example.This method can obviously reduce capture power consumption during Transition test.Meanwhile,this paper also introduces and evaluates the command recommended by SYNOPSYS Company to reduce the power during ATPG.It's suggested to combine these two methods together in order to reach better power optimization.

multi-step method;coverage pattern;test vector;design

TN99

A

1674-6236(2016)12-0149-03

2015-07-25稿件编号:201507167

丁伟(1982—),男,江苏镇江人,硕士,工程师。研究方向:集成电路设计。