基于FPGA的电磁阀控制设计与研究*

2016-10-13刘兴俊杨玉华贾兴中

刘兴俊,杨玉华,贾兴中

(1.中北大学电子测试技术国家重点实验室,太原030051;2.中北大学仪器科学与动态测试教育部重点实验室,太原030051)

基于FPGA的电磁阀控制设计与研究*

刘兴俊1,杨玉华2*,贾兴中1

(1.中北大学电子测试技术国家重点实验室,太原030051;2.中北大学仪器科学与动态测试教育部重点实验室,太原030051)

针对航空飞行器在飞行试验中需要精确控制滚控发动机电磁阀的难题,从电磁阀自身特点入手,设计了控制硬件电路并建立电磁阀门硬件电路灭弧电路响应时间模型,成功卸载60.5 V反向大电压,详细分析影响电磁阀的时间因素,同时也提出了基于FPGA的电磁阀可配置脉冲的实现方式。目前,该电磁阀控制设计已成功应用于地面发动机测试设备,具有较好的实时性、安全性和时间响应性能。

FPGA;电磁阀控制;灭弧电路;反向大电压

在航空飞行器姿态调整及控制中,主要通过滚控发动机来配置并调节飞行器的转动姿态。航空飞行器在飞行试验中测试设备需要不断地控制滚控发动机切换电磁阀,而电磁阀是一种感性负载设备,当切断电磁阀驱动电路时不能立刻释放电磁阀,因此对其实施精确控制是地面发动机测试设备的关键难题,同时,在电磁活门释放瞬间驱动电路中产生的反向大电压如何卸载而不造成影响也是面临的难题。本文在硬件上采用继电器、续流二极管和压敏电阻组合实现了电磁阀驱动和高达60.5 V反向大电压的卸载,建立了灭弧电路的RL零输入模型,在控制逻辑上提出了基于FPGA的可调制脉冲波形的控逻辑。

1 方案设计

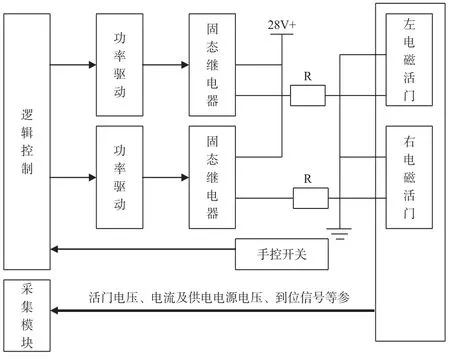

电磁阀控制包括手动控制及自动控制两种模式。电磁阀驱动电路主要由两路功率驱动模块、固态继电器、限流电阻及手动控制开关等模块组成,电磁阀控制硬件驱动电路原理如图1。

图1 电磁阀控制硬件驱动电路原理图

左右电磁阀的驱动电源采用外接15 V~45 V可调恒压源,可以自动调节外接输入直流电源以满足电磁阀动作所需的电压拉偏要求。电磁阀在上位机控制驱动过程中产生的各种信号参数(活门电压、电流及供电电源电压)以及活门到位等开关量信号通过采集模块采样后上传至上位机实时显示。

2 硬件电路设计

2.1电磁阀实时精确控制

基于对双极电磁阀机理的分析,本设计采用以下3种措施最大限度地减小电磁阀的响应时间。

(1)采用继电器模块

高速响应特性是电磁阀驱动设计应考虑的重要指标,因此在本设计中采用固态继电器模块来控制大电流。固态继电器是一种无触点开关,具有较高的响应速度,导通关断时间为2 μs~500 μs,驱动电流高达40 A,且具有导通电阻小(0.1 Ω左右)等优点[1]。因此,在电磁阀驱动电路中采用继电器来控制活门高速动作能有效缩短电磁阀到位信号的响应时间。本设计中,同时对两个电磁活门执行交替动作,两个控制端需要相同的特性参数(导通时间、关断时间及导通电压相近)以保证相应上位机可调制脉冲一致。因此,通过对同一批次固态继电器做高低温筛选实验,选出特性参数相同的继电器。

(2)采用高频大电流二极管作为续流二极管

高频大电流二极管作为续流二极管,能够迅速释放存储在电感线圈中的能量,从而使电磁阀的吸力迅速减小,降低电磁阀响应时间[2]。

(3)采用提前控制机制由于电磁阀是感性负载,切断活门驱动电流瞬间并不能立刻释放电磁阀,有一定滞后时间。因此,可以按照设定的电磁阀控制周期,合理地减小电磁阀的吸和时间,使得减少的时间能够补偿电磁活门的滞后时间。因此,采用提前控制的方法能够有效地提高电磁阀的响应时间,又不影响地面发动机测控设备的整体正常工作。

2.2硬件电路采样电阻参数设置

为实现对电磁活门的实时精确控制,首先要最大程度地减少电磁阀在复杂电磁环境中因干扰信号而引起的抖动现象,然后需减小电磁阀的响应时间,从而精确控制左右活门的高速切换。电磁阀控制驱动过程中产生的各种信号参数(活门电压、电流及供电电源电压、电磁活门到位信号)都需要实时通过采样电阻进行转换采样后实时显示并存储在FLASH中。

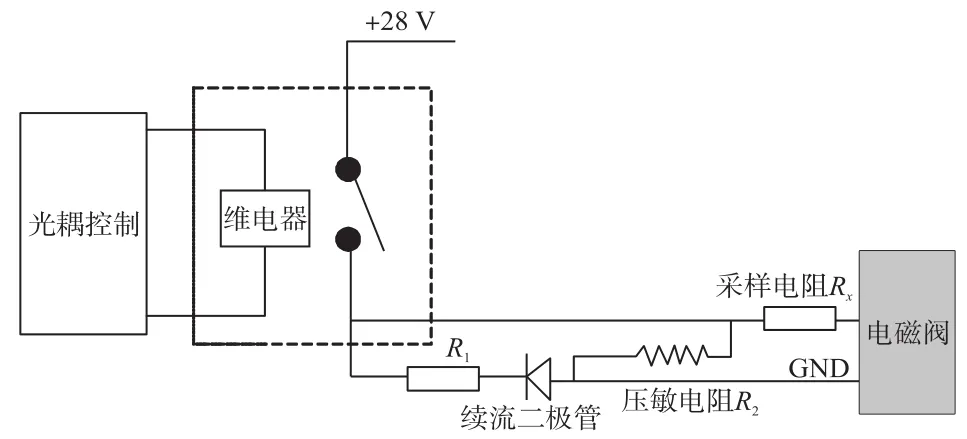

在图2中,电磁阀正常工作电压为+28 V,测试时要求拉偏电压为±3 V,工作电流不大于20 A,电磁阀线圈电阻为3.5 Ω~5.5 Ω。RX是采样电阻,同时也具有限流作用。连接电磁阀电缆直径为0.5 mm2(AFR-200,阻抗为42 Ω/km)[3]。在图2中,通过配置RX的大小来调整驱动电流,取值算法如表1所示。

图2 电磁阀驱动电路示意图

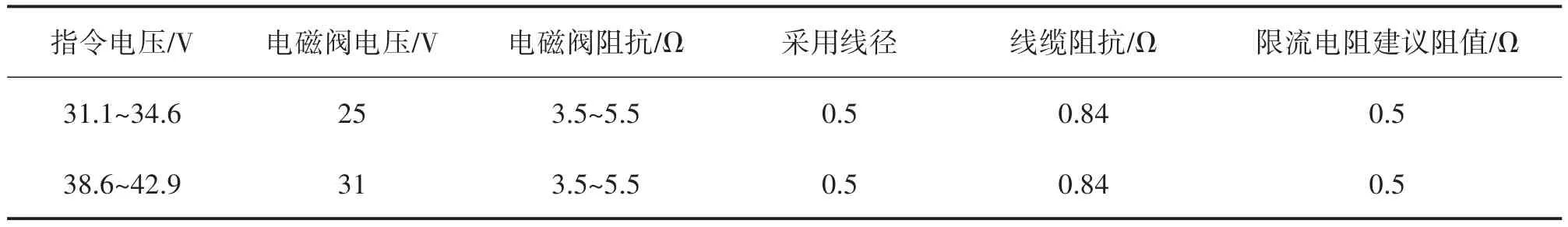

单向20 m电缆为双点双线电缆,阻抗为0.42Ω双向阻抗为0.84 Ω。当电磁阀两端电压为25 V时,电磁阀阻抗为3.5 Ω~5.5 Ω,则指令电压最小为31.1 V,最大电压为34.6 V;当电磁阀两端电压为31 V时,电磁阀阻抗为3.5 Ω~5.5 Ω,则指令电压最小电压为38.6 V,最大电压为42.9 V。因此为保证流经电磁阀电流不至于过大,综合考虑以上各种情况选定限流电阻为0.5 Ω。

表1 电磁阀控制回路限流电阻及指令电压设计列表

由表1可知,为了确保电磁阀两端电压满足(28± 3)V,并适应不同阻抗的电磁阀门,直流电源可上调上限设置为43 V,即能确保电磁阀拉偏试验正常进行。

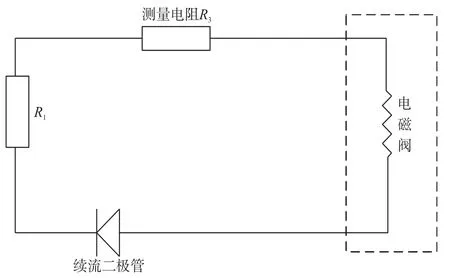

2.3电磁阀灭弧电路等效模型

经测量,该地面发动机测试设备所控制的电磁阀阻抗大小为5.2 Ω,感抗大小为1.7 H。当固态继电器闭合时,电磁阀直接由外接35 V驱动。当电磁阀断开瞬间,电磁阀因具有感性特点,仍保持原有负载电流,与原驱动电路形成RL零输入相应电路,等效回路如图3[4-5]。

图3 电磁阀灭弧电路等效原理图

在固态继电器由闭合到断开过程中,具有初始电磁阀电流I0和等效电阻R(电阻R1,R3及电磁阀内阻)相连,并构成一个串联闭合回路。根据KVL(基尔霍夫电压定律)得:

由UR=Ri,UL=Ldi/dt,代入等式(1)得出电路的微分方程为:

根据等式(2),可以得出一阶齐次微分方程的通解为

则电磁阀两端电压为:

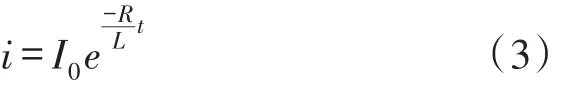

因此根据(4)得出电磁阀两端卸载电压随时间变化的曲线图如图4所示。

图4 电磁阀灭弧电路零输入响应曲线和实测反向电压卸载曲线

由上图电磁阀断开瞬间可知,等效电路的响应时间t与电磁阀电感L和等效内阻R有关,其中响应时间t为

根据上述分析,将已知等效电阻R=105.7 Ω(R1= 100 Ω,R3=0.5 Ω,电磁阀内阻为5.2 Ω)感抗为1.7 H,代入式(5)得到电磁阀左右两端响应时间t约为16.083 ms。初始电磁阀电流但根据等式(4)闭合瞬间固态继电器反向端电压最小值高达60.5 V,如此高的反向电压对负载及继电器都会产生不可避免的影响。

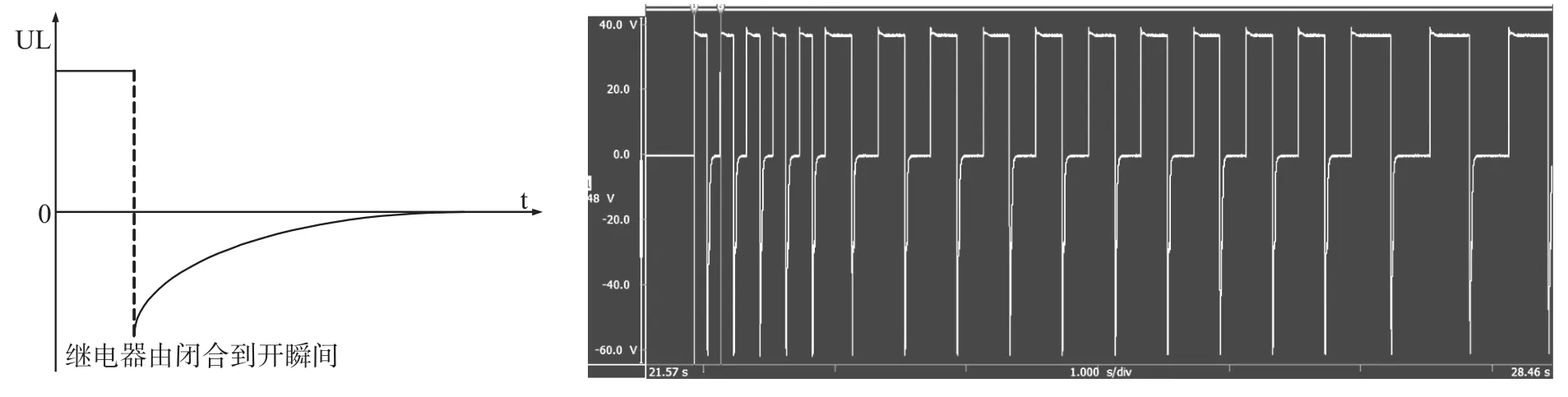

由上述分析可知,为尽量缩短电磁阀响应时间,必须增大等效电阻R,但是电阻R值并非能无限增大。在增大电阻后,继电器后级反向电压会增大从而会反向击穿继电器。在本设计中,根据继电器反向耐压值,选定电磁阀泄流R1的阻值为100 Ω。同时为避免继电器反向电压过大,采用两种方法为电磁阀过载电流提供卸载回路。如图5所示,电磁阀控制硬件电路原理图。第一种在电磁阀驱动电路中通过选用电解电容E5,E8来吸收瞬间浪涌电压;选用压敏电阻YM1、YM2,以卸载反向过载电压。

图5 电磁阀控制硬件电路

3 电磁阀可调制脉冲逻辑设计

电磁阀可调制脉冲逻辑要具备以下几个特点:发送控制指令和数据;为实现电磁阀实时可控,需要发送实时控制指令和波形数据指令;读取电磁阀传感器数据;上位机需要实时监测并显示电磁阀在动作过程中的到位信息;实现数据链路校验机制。由于整个系统的功能复杂,波形参数、控制参数、时间参数及关键指令参数均需要通过USB接口实现数据传输,因此上位机还需要监测返回的状态码,校验数据或者指令是否发送成功。

实现如此复杂的协议,不仅需要保证数据既定的传输速度,并且在传输过程中不能出现指令丢失和数据丢包的情况。因此,本测量控制装置采用USB master主控方式,把USB协议芯片Cy7C68013做主机FPGA做从机,整个动作均由USB协议芯片发起,FPGA只负责解析USB下发的指令[6]。在FP⁃GA内部开辟了一个2 kbyte容量的FIFO,满足波形数据及波形控制指令的完整下发。同时在FPGA端外接大容量外置FIFO,保证USB突发数据高速传输时数据完整性[7-8]。

3.1FPGA逻辑实现

3.1.1FPGA波形及指令识别

上位机通过USB总线下发波形数据数字量及波形控制指令数字量,FPGA对下发的2 byte数据的高字节进行识别,并将识别的波形数据及波形控制指令分别存储。FPGA内部分配两个内置512 byte RAM模块,第1个RAM模块为波形数据RAM,用来存储波形数据数字量。第2个RAM模块为波形控制指令RAM,用来存储波形控制指令数字量。

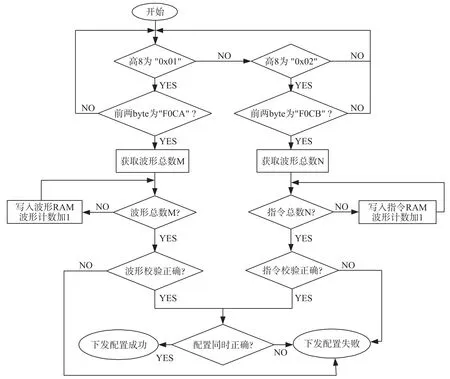

FPGA根据波形数据个数及波形控制指令条数分配RAM地址,最后校验波形数据和波形控制指令是否正确并返回状态,具体配置流程如图6所示。

图6 波形数据及控制指令数据配置流程

对于波形数据数字量,FPGA对USB下发的每两byte数据,首先判断高byte是否为“0x01”,接着判断后面的2 byte有效数据是否为“FOCA”,如果正确的话,获取波形数据容量M。在波形RAM中分配M大小的空间,将USB下发的数据以字(WORD)为单位存储,并按照RAM中存储的地址分配各自波形索引值。待全部波形数据在波形RAM中登记完毕后,通过USB最后下发的两字节数据校验下发波形数据是否正确。

对于波形控制指令数字量,FPGA首先判断高byte是否为“0x02”,接着判断后面的2 byte有效数据是否为“F0CB”,如果正确的话,获取波形控制指令数据容量N。在波形RAM中分配N大小空间,将USB下发的数据以字为单位存储,并按照RAM分配控制指令索引值。带全部控制指令在波形RAM中登记完毕后,通过USB最后下发的两byte数据校验下发控制指令数据是否正确。

3.1.2可调制脉冲的实现

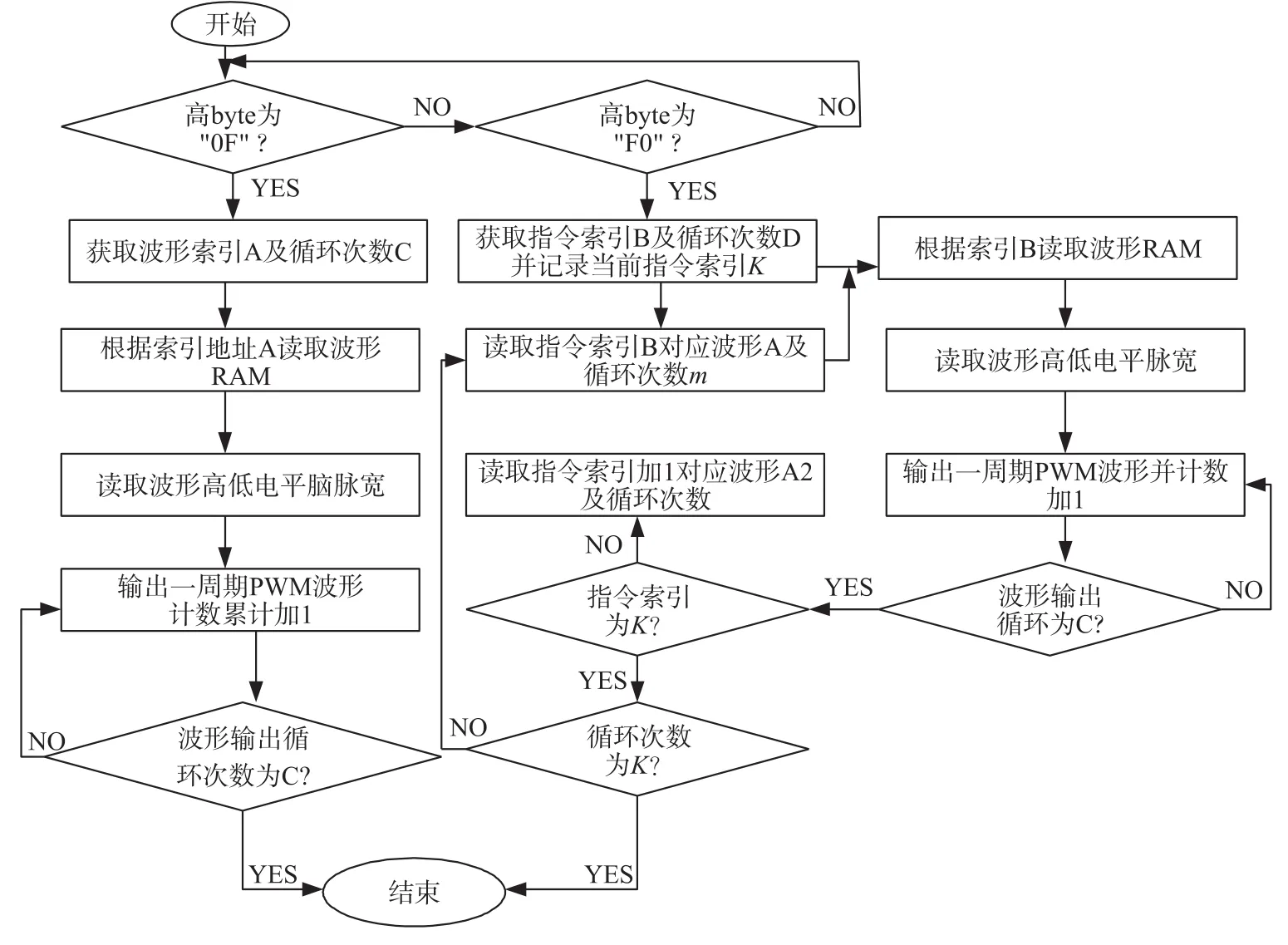

主控制器FPGA等待配置波形数据RAM和波形控制指令RAM完成后,主控制器先从波形控制指令RAM中读取第一个控制命令字,根据先前的协议解析控制指令字高byte以确定单波形循环(“0F”为单循环控制指令)还是多波形循环(“F0”为多循环控制字),接着获取需要循环波形数据相对应的索引值和波形循环总次数。根据获取的波形索引值,从波形数据RAM中依次读取波形高低电平值,并驱动电磁活门,同时记录判断循环次数是都达到设定的波形循环次数。等待完成这次波形后,再次从波形控制指令RAM中读取下一条波形控制指令,并根据波形指令依次从波形数据RAM中获取波形信息,并驱动电磁活门,具体流程如图7所示。

图7 主控制器FPGA识别并执行波形驱动流程图

4 实验结果

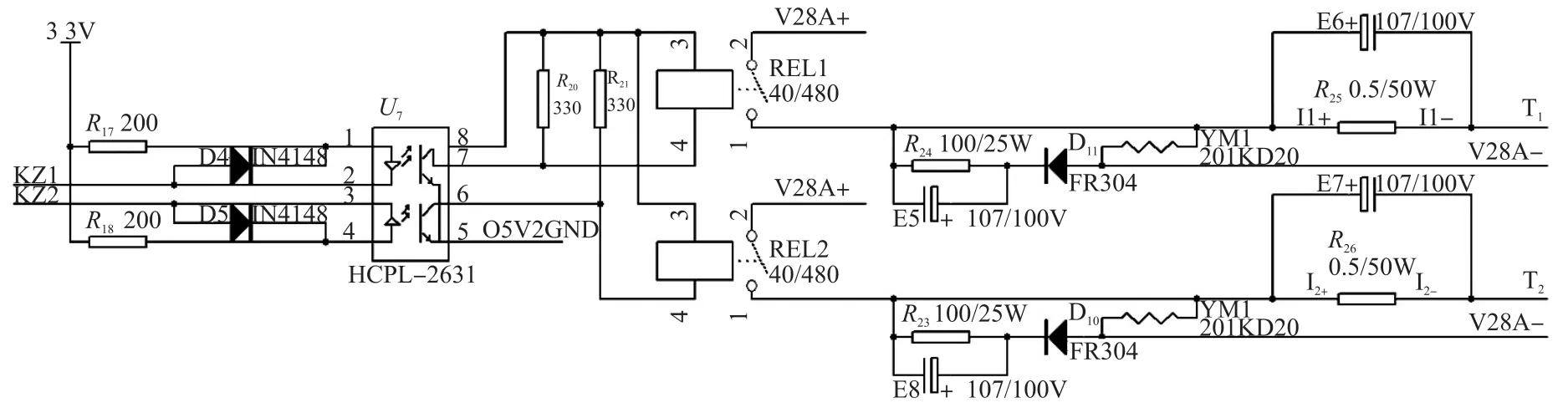

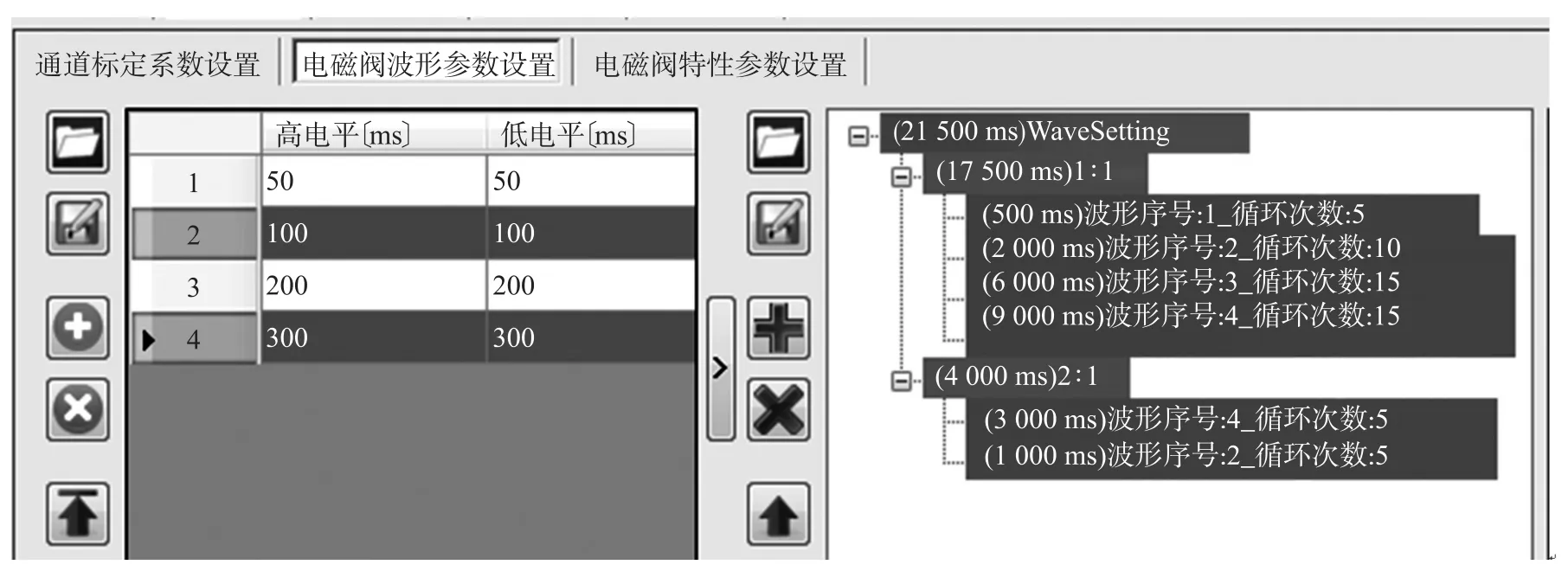

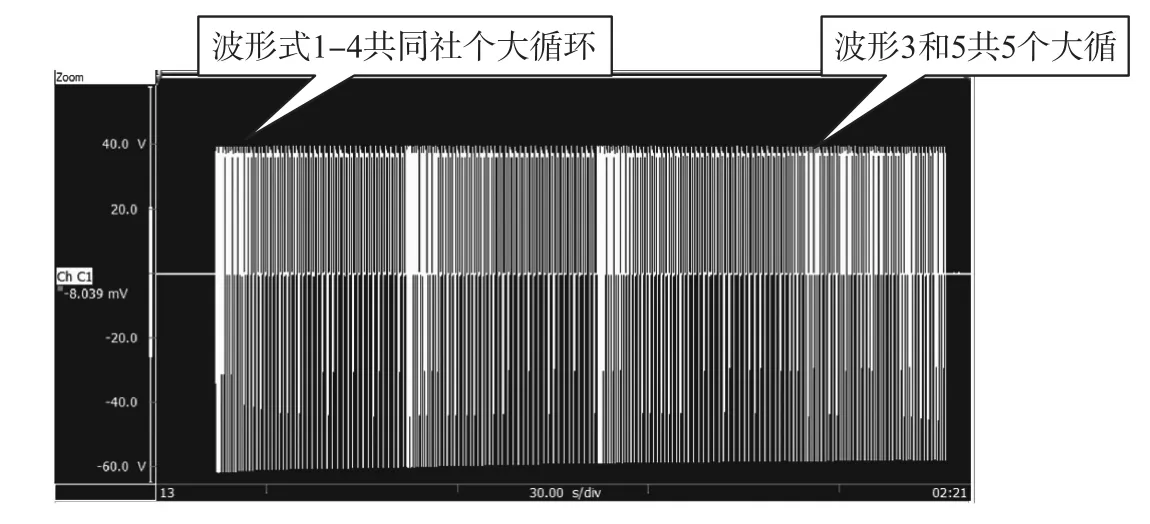

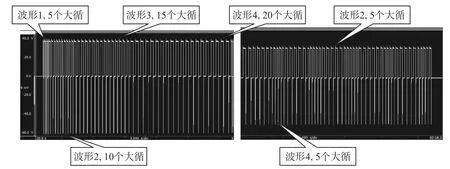

地面发动机测控设备最大可调至脉宽可设置为65 535 ms,最小可调制脉宽可设置为1 ms。上位机配置4种电磁活门波形参数,单周期分别为100 ms、200 ms、400 ms、600 ms、占空比为50%的波形数据。波形控制指令设置为波形1单循环5次、波形2单循环10次、波形3单循环15次、波形4单循环20次,对波形1~波形4全部大循环3次;随后继续将波形3单循环5次,波形5单循环10次,对波形3和5全部大循环5次。详细波形数据设置及波形指令设置如图8所示。

图8 电磁活门波形参数及循环设置

通过备份采集装置测量出电磁活门动作如图9所示(截取3个大循环波形)。通过放大单个大循环波形测量各个波形参数,实现了单波形的多次循环,多个单波形的多次嵌套大循环,可调制脉冲波形循环不受波形设置前后顺序的影响,可以任意设置顺序,完全符合上位机波形参数的设置。

图9 波形大循环示意图

图10 波形1-4共3个循环监测示意图

5 总结

本文深入地分析了电磁阀控制的硬件电路原理和可调制脉冲波形实现的设计思路,对电磁阀精确控制原理框图建立了灭弧电路RL零输入响应模型。电磁阀的控制硬件电路可以保证电磁阀的高速切换,可以卸载高达60.5V反向大电压,通过续流二极管和阻容的组合消除对驱动控制电路造成的影响。在基于FPGA的控制逻辑上实现了可调制脉冲波形的控制,成功解决了电磁阀精确控制的难题。

[1]王昌华.固态继电器及应用[J].西北电力技术,2004(5):49-52.

[2]徐雁,张德会,姚军.高频大电流测量[J].电测与仪表,2007 (2):10-12,53.

[3]唐金元,王翠珍,纪明霞.通信电缆特性阻抗测量方法研究[J].仪表技术,2014(10):10-12,16.

[4]尼尔森,里德尔.电路[M].第9版.北京:电子工业出版社,2012.

[5]邱关源,罗先觉.电路[M].第5版.北京:高等教育出版社,2010.

[6]任勇峰,张凯华,程海亮.基于FPGA的高速数据采集存储系统设计[J].电子器件,2015,38(2):139-142.

[7]Cypress Semiconductor Corporation.EZ-USB Manual Technical Reference,Version4.6[S].2001.

[8]程云飞,胡荣强,李伟.基于EZ-USB FX2固件程序设计[J].电子元器件应用,2007(1):42-44.

刘兴俊(1989-),男,汉族,山西太原人,中北大学硕士研究生,研究方向为电路与系统,1185889308@qq.com;

杨玉华(1977-),女,汉族,山西太原人,副教授,硕士生导师,研究方向为数据采集、数字信号及功能转换材料,yangyuhua@nuc.edu.cn。

Solenoid Valve Control Design and Research Based on FPGA*

LIU Xingjun1,YANG Yuhua2*,JIA Xingzhong1

(1.National Key Laboratory for Electronic Measurement Technology,North University,Taiyuan 030051,China;2.Dynamic Testing Laboratory Instrument Science and the Ministry of Education,North University,Taiyuan 030051,China)

For aviation aircraft in the flight test,the precise control of the engine roller solenoid valve requires.Start⁃ing from its own characteristics solenoid valve control hardware circuit design,an interrupter arc response time mod⁃el of the solenoid valve hardware circuit is established,reverse large voltage 60.5 V successfully uninstalled,and the time factor of the solenoid valve analyzed.Based on FPGA implementations,solenoid valve can be configured by pulse matches method.Currently,the solenoid valve control design scheme has been successfully used in ground engine test equipment.It has a good real-time,security,and time response.

FPGA;solenoid valve control;interrupter circuit;reverse large voltage

TP301.6

A

1005-9490(2016)02-0392-06

EEACC:5180F10.3969/j.issn.1005-9490.2016.02.030

项目来源:国家自然科学基金项目(51275492)

2015-05-27修改日期:2015-06-25