低相噪低杂散650 MHz点频源的设计

2016-10-13赵亚妮

赵亚妮

低相噪低杂散650 MHz点频源的设计

赵亚妮

(中国电子科技集团公司第十研究所,四川 成都 610036)

提出了一种锁相环内倍频的设计方法用于低相噪低杂散650 MHz的点频源。采用晶体滤波器将10 MHz源的倍频信号提取出来,然后再利用锁相环倍频至需要的650 MHz,最后放大滤波输出。测试结果表明,该点频源的相位噪声为–77 dBc@1 Hz, –95.4 dBc@10 Hz, –107.5 dBc@100 Hz, –116.2 dBc@1 kHz, –114.3 dBc@10 kHz, –121.8 dBc@100 kHz,–137.9 dBc @1 MHz;输出功率9.8 dBm;谐波抑制–78 dBc;幅度稳定度±0.5 dB/24 h。该点频源具有低相位噪声、低杂散、高频率稳定度等性能,且结构简单实用。

低杂散;低相噪;锁相环;点频源;频综;倍频

频率源在现代通信中有着举足轻重的地位,常用的有跳频源和点频源。作为系统中的基础信号,它们的性能和纯度直接影响着整个系统的指标[1-4]。

作者提出了一种将锁相环倍频用于低相噪低杂散650 MHz的点频源的设计方法。采用晶体滤波器将10 MHz源的倍频信号提取出来,然后再利用锁相环倍频至需要的650 MHz,最后放大滤波输出。

1 锁相环的基本原理

本文的点频源基于锁相环原理设计,因此首先介绍锁相环的基本原理。锁相环本质上是一种负反馈环路,其基本电路部件如图1所示,工作原理为:鉴相器(内部集成了鉴相模块及分频模块)通过比较晶振输入信号的相位,与压控振荡器输出信号的相位,根据两者之间的相位差大小,产生一个正比于此相位差的误差电流,该误差电流脉冲经过环路滤波器滤除高阶成分后再积分形成一个平滑的脉冲电压,此电压作用于压控振荡器(voltage controller oscillator,简称VCO),控制其调整输出频率,反复作用之后,当相位差为零时,VCO输出频率就不再变化,此时锁相环就进入了锁定状态。锁定时,VCO的频率等于输入信号的频率。

衡量频率源性能的主要指标有:输出电平、杂散抑制度、谐波抑制度、频率稳定度(长期稳定度、短期稳定度)、相位噪声等。其中短期稳定度是相位噪声的频域表示。

2 点频源电路设计及实现

为了达到提出的低相噪低杂散高稳定度的要求,一般锁相环方案都采用参考信号直接激励锁相单环的电路形式,或参考信号直接倍频的方案,然而由于参考信号直接激励锁相单环的电路形式不易调试,不适用于批量化生产;参考信号直接倍频的方案杂散多,对滤波器要求很高,成本较高。经过对比考虑,本文结合了两者的优点,最终提出了图2的设计方案,不仅方案简单,同时具有低相噪、低杂散、易调试的优点,适用于工程中大批量生产。

在本方案中,为了利用参考信号的高品质纯度和低相噪的优点,先将10 MHz输入信号放大倍频,再采用高值的滤波器提取出参考信号的五倍频信号50 MHz,在保证50 MHz信号有足够低的相噪和足够好的纯度时,将其放大,作为参考信号提供给分频锁相环,分频锁相环利用高品质纯度和低相噪的50 MHz参考信号,将信号锁定在650 MHz,从而实现了低相噪低杂散的650 MHz点频源信号的产生,之后再经放大滤波后输出。该方案倍频的数值、锁相环的分频比均经过了多次改版调试。该方案有结构简单、相位噪声低、杂散少、易于调试等特点,因此可大大节省电路调试时间,电路图见图3。

2.1 50 MHz晶体滤波器

10 MHz参考信号经过低噪放和倍频之后,信号频谱中出现了非常多的杂散信号,为了提取出所需的高品质50 MHz信号,需采用高品质因数滤波器,滤波器的性能直接影响了最后输出信号的频谱纯净度。此处为电路设计中难点和重点。对滤波器指标要求很高。考虑到体积成本,本文最终选用了特别定制的晶体滤波器。其主要技术指标如下:

1) 中心频率:50 MHz;

2) 驻波系数≤1.5;

3) 特性匹配阻抗:50 Ω;

4) 插损≤6 dB;

5) 带外抑制:在偏离中心频率±100 kHz处,抑制>50 dB;在偏离中心频率±10 kHz处,抑制>20 dB;

6) 3 dB带宽≥4 kHz;

7) 工作温度–40 ~ +70℃;

8) 结构尺寸:25 mm×15 mm×10 mm。

2.2 650 MHz锁相环

在低相噪低杂散的要求下,方案中的分频锁相环中用到的鉴相器芯片选的是Hittite公司的鉴频鉴相器HMC440,该芯片具有低相噪的优点,其工作电压为+5 V;工作电流为250 mA;在鉴相频率为100 MHz时,相噪指标可以达到–153 dBc/Hz@10 kHz;该低相噪的芯片内部集成了5bit可编程分频器(=2~32);其参考输入频率范围为10~1 300 MHz,参考输入信号电平为–10~+10 dBm;随着分频比的变化,鉴相范围可达到10~2 800 MHz;其鉴相灵敏度为0.286 V/Rad。

为了充分满足低相噪低杂散的要求,分频锁相环中采用的压控振荡器也选用了低相噪锁相环芯片,MINI公司的低相噪VCO芯片ROS-660PV,其工作电压为+5 V;工作电流15 mA;输出信号范围为640 MHz到660 MHz;相噪指标在偏离主信号100 kHz时可达到–127 dBc/Hz;压控灵敏度更可达到10~14 MHz/V;输出信号的电平典型值为0 dBm。另外由于分频锁相环中的分频比是由外围电路来决定的,所以电路结构十分简单,仅需要将芯片引脚中A1至A5按说明置高置低,便可确定相应的分频比[5]。

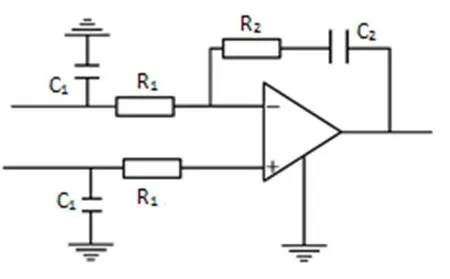

由于该低相噪VCO芯片ROS-660PV是浮地输出的形式,所以其后的环路滤波器也只能采用浮地的差模输入形式。为了避免在此处引入不必要的相噪干扰,本文特意选用了具有超低相噪低失真的ADI公司运放芯片AD797来搭建如图3所示的有源环路滤波器。使用时,根据环路带宽和阻尼系数,便可计算出所需各个电容电阻元件的值,以此达到所需的指标。

图3 分频锁相环的有源环路滤波器

2.3 其他模块

同上所述,为了达到低相噪低杂散的要求,在信号的输入端,为其放大并提供倍频功能的器件选用的是宽带低噪声放大器2SC3357。同时为了在50 MHz晶体滤波器之后对信号进行放大,电路版图中预留了π型衰减器位置,一方面可避免放大器饱和后无法调试的现象出现,也方便随时调整信号电平至所需值。在锁相环后端电路中,放大滤波模块分别采用了MINI公司的放大器ERA-5SM和同公司的低通滤波器LFCN-630,用来实现对锁相环输出信号的放大和滤波处理。放大器ERA-5SM的输出1 dB压缩点为16.5 dBm。低通滤波器LFCN-630的特性为:当输入在DC~630 MHz内时,插损<1 dB;当输入为830 MHz时,插损=3 dB;当输入在1 050~ 3 500 MHz范围内时,插损=40 dB;阻带VSWR为20;通带VSWR为1.2;额定工作电流为0.5 mA;额定工作温度为–55~+100℃。PCB版图中电路的滤波模块后也预留了π型衰减器的位置,它在实现对点频源输出信号电平调节的同时,也巧妙地实现了电路特性的匹配。

3 点频源整体测试

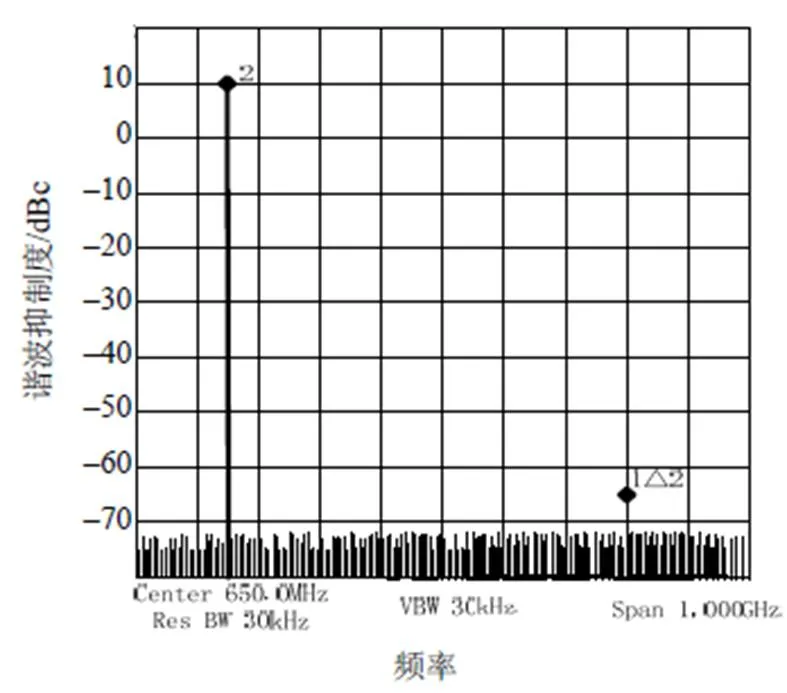

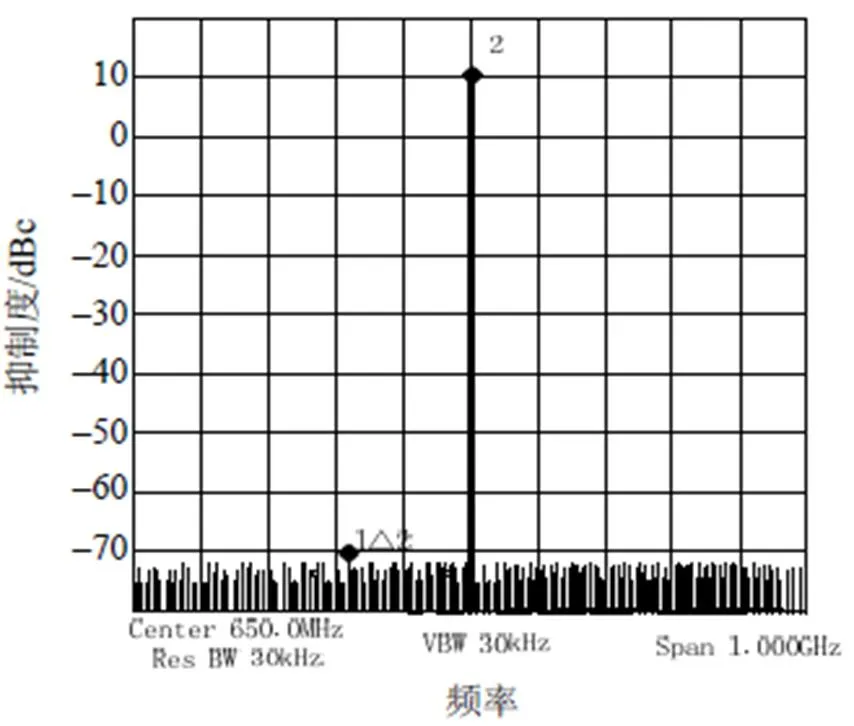

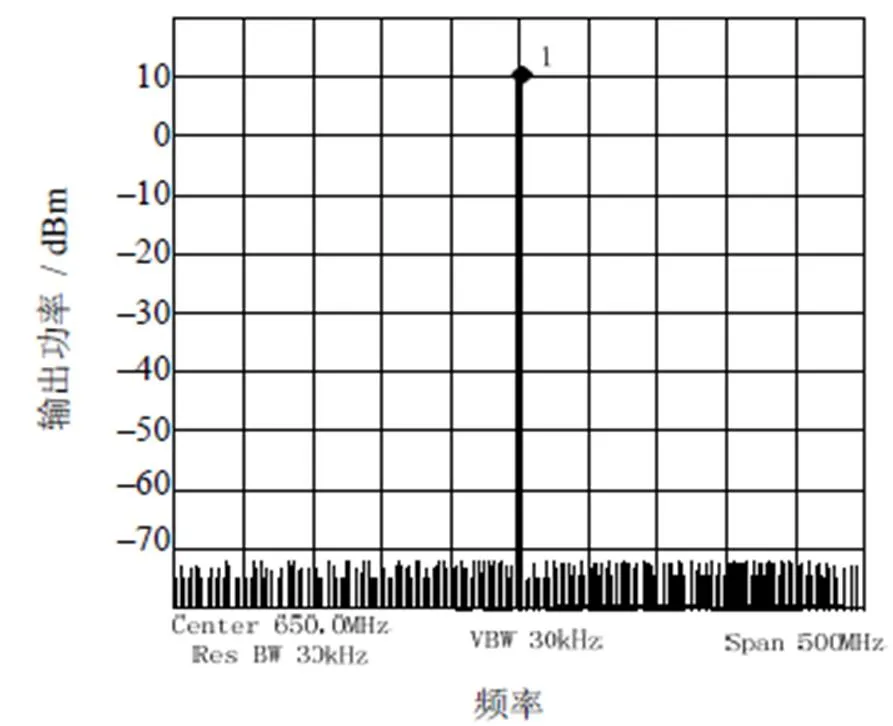

用频谱仪PXA N9030A对所设计的锁相环实物进行测试,其相噪结果具体为:–77 dBc @1 Hz, –95.4 dBc @10 Hz, –107.59 dBc @100 Hz, –116.2 dBc @1 kHz, –114.3 dBc@10 kHz, –121.8 dBc@100 kHz, –137.9 dBc@1 MHz;谐波抑制结果如图4所示,具体为–78 dBc;带宽为1 GHz时杂散抑制情况见图5,具体为杂波抑制度–83 dBc;图6为本文所述点频源的输出功率,可见输出电平值为9.8 dBm。

4 结论

介绍了一种低相噪低杂散650 MHz点频源的设计方法。为了达到低相噪和低杂散的性能,特提出了一种锁相倍频的设计方法,采用性能优良的晶体滤波器将10 MHz源的倍频信号高纯度地提取出来,其可以保持参考信号的高品质相噪和杂散,然后再利用锁相环倍频至需要的650 MHz,最后放大滤波输出。结果表明与传统测控领域信道所用频综相比,该点频源具有低相位噪声、低杂散、高频率稳定度、低成本等性能,且结构简单实用,体积小,具有批量化生产的优点。

图4 点频源的谐波抑制测试结果

图5 点频源的杂散抑制测试结果

图6 点频源的输出功率

[1] 梁孝彬, 石玉, 王轩. 基于DDS技术L波段小步进低相噪频率源设计与实现[J]. 电子元件与材料, 2015, 34(5): 54-57.

[2] 刘嘉兴. 向技术极限挑战——深空测控通信的目标[J]. 电讯技术, 2008, 48(4): 1-7.

[3] 刘嘉兴. 深空测距信号短稳对测距精度的影响 [J]. 空间电子技术, 2012(12): 66-69.

[4] 刘永智, 鲍景富, 高树廷. 一种S频段高性能频率合成器的设计与实现[J]. 电讯技术, 2011, 51(1): 89-92.

[5] 杜丹. 深空测控系统1 Hz低相噪频率合成技术[J]. 电讯技术, 2015, 55(11): 1249-1254.

(编辑:陈渝生)

Design of 650 MHz frequency source with low phase noise and low spurious

ZHAO Yani

(No.10 Institute of China Electronic Technology Co., Chengdu 610036, China)

A low spurious, low phase noise 650 MHz frequency source was proposed by using phase locked loop (PLL) frequency multiplier design method. First, frequency multiplication signal of 10 MHz reference was extracted by using crystal filter, second, PLL locked the frequency to 650 MHz, then the signal was amplified and filtered output. The test results show that the phase noises of the frequency source are –77 dBc@1 Hz, –95.4 dBc@10 Hz, –107.5 dBc@100 Hz, –116.2 dBc@1 kHz, –114.3 dBc@10 kHz, –121.8 dBc@100 kHz, –137.9 dBc@1 MHz; the power of output is 9.8 dBm; the harmonic suppression is –78 dBc; the amplitude stability is ±0.5 dB/24 h . So a low phase noise, low spurious, high frequency stability frequency source is realized whose structure is simple and useful.

low spurious; low phase noise; PLL; frequency source; frequency synthesis; frequency multiplier

10.14106/j.cnki.1001-2028.2016.07.018

TN74

A

1001-2028(2016)07-0077-03

2016-04-25

赵亚妮(1988-)女,山西运城人,工程师,主要从事航天测控的研究,E-mail: 2500129341@qq.com。

2016-07-01 10:50:50

http://www.cnki.net/kcms/detail/51.1241.TN.20160701.1050.017.html