金属氧化物避雷器测试仪校准装置设计

2016-10-12周哲玲邓建清

陈 昕 周哲玲 邓建清

(广东电网有限责任公司汕头供电局1,广东 汕头 515041;长沙天恒测控技术有限公司2,湖南 长沙 410100)

金属氧化物避雷器测试仪校准装置设计

陈昕1周哲玲1邓建清2

(广东电网有限责任公司汕头供电局1,广东 汕头515041;长沙天恒测控技术有限公司2,湖南 长沙410100)

针对RC阻容网络检定氧化锌避雷器测试仪的不足,研究了氧化锌避雷器测试仪谐波电流检测技术,提出了一种金属氧化物避雷器测试仪校准装置。对反馈信号进行离散傅里叶变换(DFT),消除高次谐波。阐述了校准装置的硬件设计方案及各功能模块的工作原理、软件设计方案的工作流程。最后,试验证明了该校准装置的可行性,其与传统的RC阻容网络方法相比更具优势。

避雷器FPGA标准信号发生器DFT高次谐波消除模数转换上位机

0 引言

金属氧化物避雷器(metaloxidearrester,MOA)利用金属氧化物的非线性特性进行开断电流,是电力系统中广泛使用的一次过电压保护设备。作用于MOA的电压不同,将会引起MOA中的金属氧化物阀片性质发生剧烈变化。在雷电电压的作用下,阀片呈现低阻状态,且电压消失后,可恢复为高阻态。正常工作电压下,MOA处于高阻状态,但会有电流流过阀片。由于长期在大电压等级以及户外的环境下运行,避雷器的工作性能会出现变化,并且极易发生损坏[1]。而避雷器故障导致的后果非常严重,不仅会丧失其保护设备及线路的基本功能,甚至还会造成电力系统过压事故。为保证MOA的正常运行,必须对其进行定期检测。对于MOA预防性试验,国内外研制了各种MOA测试仪。而针对这些测试仪,国家并没有制定相应的校准规范。目前,检验MOA测试仪主要采用标准信号发生器法和RC阻容网络法。

传统的RC阻容网络法所需的试验设备包括自偶式调压器、交流电压表、交流电流表、交流电阻箱以及交流电容箱,对试验设备要求不高[2]。其不足之处是回路接线繁琐、操作复杂、工作效率低;标准电压器和电容器并非理想元器件,会引入残余电感和分布电容。在交流电路中,电阻器的时间常数不为0,其引起的误差约为百分之几;电容器也存在一定的损耗因数,引起的误差将近千分之几[3]。电路中无法产生3次谐波电流,测试数据单一、相角设置不灵活等众多因素影响校验结果的一致性。本文提出了一种金属氧化物避雷器测试仪的校准装置。

1 DFT信号处理

电流输出信号经过I/U转换、信号调理后,由模数转换器转换成数字信号并传递给现场可编程门阵列(fieldprogrammablegatearray,FPGA),调整输出信号的幅值和相位,消除高次谐波噪声。输入信号为:

x(t)=IPR1sin2πf0t-IPR3sin6πf0t+IPC1cos2πf0t

令信号频率为f0、采样频率为fs、采样序列长度为N,则采样得到的离散序列为:

(1)

(2)

则序列x[n]的离散傅里叶变换[4-5]为:

(3)

假设信号被5次谐波和7次谐波污染,令所有谐波幅值为0.1A。经过傅里叶变换,得到信号频谱图。

x(t)=0.1sin2πf0t-0.1sin6πf0t+0.1cos2πf0t+

0.1sin10πf0t+0.1sin14πf0t

(4)

通过叠加反向的5次谐波和7次谐波信号,消除由后续硬件引起的高次谐波影响。

2 硬件设计

硬件电路总体结构如图1所示。图1中,ZX为被检MOA测试仪的等效电阻。

图1 硬件电路总体结构框图

2.1主控电路

微处理器使用高性能的ARM®CortexTM-M3 32位的RISC内核,工作频率为72MHz,内置高速存储器(高达512kB的闪存和64kB的SRAM),丰富的增强I/O端口和连接到两条APB总线的外设,多达112个快速I/O端口。微处理器主要与外设进行通信、数据显示、响应按键操作等,并与FPGA进行协议约定,控制FPGA进行数字信号处理。

FPGA[6-7]主要负责以下3项工作。

①接收模数转换器反馈的信号,对标准输出信号进行幅值和相位调节。同时,对反馈信号进行离散傅里叶变换。设定单个周期为256个采样点,则fs=256f0。如果采样点数控制N=256×16=4 096,可以保证q为整数,不发生频谱泄漏。对信号进行频谱分析,信号发生时叠加反向谐波信号,抵消了噪声及高次谐波,降低了波形的失真度。

②根据奈奎斯特采样定律,输出序列长度为N=4 096的离散数字信号,将信号传递给数模转换器,并进行数模转换。在系统允许的失真度情况下,且保证fs≥2fM,fs越大,由数模转换器转换的模拟信号越接近原始信号。

③同微处理器进行约定,接收微处理器发出的命令,进行复杂的运算处理。

FPGA功能框图如图2所示。

图2 FPGA功能框图

2.2采样电路

16位A/D和D/A负责信号的模数和数模转换,A/D转换器将电压、电流信号转换为离散的数字信号,便于FPGA处理。D/A转换器将离散的数字信号转换成稳定度非常高的正弦波电压信号和电流信号。A/D和D/A转换器的分辨率应该与FPGA采样频率fs相匹配,否则会直接影响后续数据的处理效果。

2.3模拟信号输出电路

从D/A输出的模拟信号[8-9]通过OP1、OP3进行信号调理后,经过低通滤波器将基波和3次谐波以外的噪声和高次谐波滤除,再进行功率放大驱动输出变压器进行输出。电流信号通过I/U转换模块、电压信号通过U/U转换模块进行反馈,再经过OP2、OP4信号调理,将输出信号反馈至OP1、OP3的输入端,并通过模数转换器传递至FPGA。FPGA调节输出标准信号幅值和相位,并对信号进行频域分析,叠加反向高次谐波信号,以抵消由硬件电路引入的噪声,降低波形失真度,改善负载特性,最终形成稳定的闭环反馈控制电路。

2.4上位机

微处理器通过RS-232与上位机进行通信。上位机安装监控和通信软件,设有人机对话界面;读取被检金属氧化物避雷器测试仪数据,进行误差计算。

3 软件设计

本设计采用实时嵌入式操作系统[10]作为开发平台。系统上电后,首先进行初始化配置,包括主时钟、I/O口、SPI模块等。初始化成功后,读取上位机界面设定的Up、IPR1、IPR3、IPC1。如果设定值超过输出上限,系统报警,需重新设定。根据设定值判断是否需要切换电压量程,选择最佳量程输出电压;判断IPR1、IPR3、IPC1电流是否需要切换量程,选择最佳量程输出电流,以提高输出精度。同时上位机通过RS-232或RS-485读取被检测试仪数据,计算误差值。程序流程如图3所示。

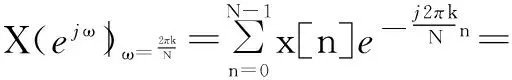

4 数据分析

对校准装置参比电压输出和谐波电流输出的性能进行验证,如表1和表2所示。220V量程的参比电压相对误差不大于0.05%;20mA量程的阻性基波电流和容性基波电流的相对误差均不大于0.07%,3次谐波电流相对误差不大于1%;相角误差不大于0.01°。数据符合标准装置的相关计量要求。

图3 程序流程图

标称值/V实际值/V相对误差/%2221.990.044444.010.026665.970.048888.050.05110110.010.01220220.030.01

表2 20 mA量程电流误差

5 结束语

金属氧化物避雷器测试仪校准装置采用基于FPGA的标准信号发生器法,通过DFT,从频域的角度对信号进行分析。通过叠加反向高次谐波,抵消由硬件电路引入的噪声,降低了波形失真度。相比RC阻容网络方法,该装置具有精度高、相位调节灵活和操作便捷等优点;避免了因电阻、电容受外界因素影响而引入的误差,明显提高了检定装置的精度和稳定度。

[1] 赵玉林,项雯,李继昌.氧化锌避雷器分布式测量装置的研究[J].电测与仪表,2015,52(4):81-84.

[2] DLT 987-2005 氧化锌避雷器阻性电路测试仪通用技术条件[M].北京:中国电力出版社,2006.

[3] 冯建,史小涛,许峰.氧化锌避雷器测试仪阻容网络校准方法[J].上海计量测试,2012(4):20-29.

[4] SANIT K,MITR A.Digital signal processing [M].Beijing:Publishing House of Electronics Industry,2006.

[5] 张强.基于DFT的数字相位计设计[J].自动化与仪器仪表,2015,41(2): 33-35.

[6] 王丹,许虎.LET系统中FFT的研究与DSP实现[J].电子技术应用,2011,37(10):63-66.

[7] 韩广,王斌,王大磊.基于FPGA的相关干涉仪算法的研究与实现[J].电子技术应用,2010,36(7):76-80.

[8] 朱晓华.微机原理与接口技术[M].北京:电子工业出版社,2008.

[9] 远坂俊昭.测量电子电路设计[M].北京:科学出版社,2004.

[10]李志明,檀永,徐石明,等.STM32嵌入式系统开发实战指南[M].北京:机械工业出版社,2013.

DesignoftheCalibrationDeviceforTesterofMetalOxideArrester

ToagainstthedeficienciesincalibratingthetesterofMOAbyusingresistor-capacitornetwork,theharmoniccurrentdetectiontechniqueofthetesterofMOAisresearched,thecalibrationdevicefortesterofmetaloxidearresterisgiven.ThediscreteFouriertransform(DFT)offeedbacksignalisconductedtoeliminatethehigherorderharmonics.Thedesignschemeofthehardwareofcalibrationdevice;theworkingprincipleofvariousfunctionalmodules;andthedesignschemeandworkingprocessofsoftwarearedescribed.Thetestsverifythefeasibilityofthiscalibrationdevice;comparingwithtraditionalmethodofusingRCnetwork,itismoresuperior.

ArresterFieldprogrammablegatearray(FPGA)StandardsignalgeneratorDiscretefouriertransform(DFT)HigherorderharmonicseliminationAnalogdigitalconversionHostcomputer

陈昕(1984—),男,2012年毕业于中山大学电子与通信工程专业,获硕士学位,工程师;主要从事电网电测、电能以及热工技术监督等工作。

TH86;TP27

ADOI:10.16086/j.cnki.issn1000-0380.201609017

修改稿收到日期:2016-01-07。