用于8位80 MS/s模数转换器的增益数模单元电路

2016-09-12董嗣万朱樟明刘敏杰杨银堂

董嗣万,朱樟明,刘敏杰,杨银堂

(西安电子科技大学微电子学院,陕西西安 710071)

用于8位80 MS/s模数转换器的增益数模单元电路

董嗣万,朱樟明,刘敏杰,杨银堂

(西安电子科技大学微电子学院,陕西西安 710071)

提出了一种针对高速中精度模数转换器的增益数模单元电路优化设计,满足8位80 MS/s流水线模数转换器的要求.通过优化设计一种改进传输门开关,提高了增益数模单元电路的线性度;针对高增益两级宽带运算放大器,提出了一种宽带运算放大器优化设计方法,能有效地优化运算放大器的建立时间和功耗;优化设计了一种高速低功耗动态比较器,在提高速度方面具有优势.基于0.18μm 1.8 V CMOS工艺完成了增益数模单元及8位80 MS/s流水线模数转换器的流片验证,测试结果表明,在80 MHz采样频率下,输入信号频率为35 MHz时,模数转换器的信号噪声失调比为48.9 d B,有效位数为7.83位.

增益数模单元;运放优化;传输门;动态比较器;流水线模数转换器

增益数模单元(Multiplying Digital-to-Analog Converter,MDAC)是流水线模数(Analog to Digital,A/ D)转换器电路的核心模块,由于其转换速度和有效位数制约了整个模数转换器所能达到的最大转换速度和最高分辨率,所以高速增益数模单元电路的研究对设计高速流水线模数转换器具有重大的意义[1-4].增益数模单元电路中信号导通开关、运算跨导放大器(Operational Transconductance Amplifier,OTA)、比较器等关键部分的设计尤为重要.针对传统传输门结构,在不引入较复杂电路的情况下,笔者提出一种改进的金属氧化物半导体(Metal Oxide Semiconductor,MOS)开关以减少导通电阻非线性.对于高精度的模数转换器,运算跨导放大器需要提供高增益和大带宽,笔者分析了一种非传统米勒补偿两级运放,对电路进行Matlab建模优化,并用gmId查表方法[5]设计,对运放的单位增益带宽和电路的功耗进行优化.同时,设计了一种改进的动态锁存比较器,以提高转换速率.

1 增益数模单元电路结构及开关优化

笔者采用电容翻转型增益数模单元电路,与电荷再分配型结构相比,所需电容数量少,面积更小,功耗更低,噪声性能更好[6].整体结构及传输函数如图1(a)和图1(b)所示,在采样相位,开关Φ1闭合,实现对输入信号的底极板采样.采样电容底极板与输入信号相连接,顶极板与共模电位相连接,采样结束时差分输入信号保存在两个采样电容上.在保持相位,反馈开关Φ2闭合,反馈电容的底极板与输出端短接,顶极板与输入端短接,信号同时转移到了输出端.

图1 增益数模单元单边简化及所用传输门示意图

由于开关存在非理想效应,导致采样信号失真,这里的采样与反馈开关S1使用自举开关实现.对于反馈开关S2,多数采用普通的互补金属氧化物半导体(Complementary Metal-Oxide-Semiconductor,CMOS)传输门,相比于加自举开关,这种做法节省了面积和功耗,但是会降低电路的性能.笔者采用了改进的传输门[7]来代替,进一步提高了采样保持电路的线性度.

采样开关如图1(c)所示,与传统互补传输门相比,改进结构获得相同的通道电阻而所引入的寄生电容仅为原来的一半.在开关导通时,P沟道金属氧化物半导体(P-channel Metal Oxide Semiconductor,PMOS)管的源极与衬底相连以消除其衬偏效应,从而降低了开关的导通电阻;在开关关闭时,PMOS管的衬底被接到电源电压,保证输入在电源和地的变化范围内,源漏到衬底的寄生二极管处在反偏状态,从而提高了开关电路在高频下的无杂散动态范围(Spurious Free Dynamic Range,SFDR)性能.

2 高速高增益运算跨导放大器

在高速、中精度增益数模单元的工程设计中,常用的运算跨导放大器结构有两级式、套筒式、折叠式运放以及增益自举运放.套筒式结构由于所需电源电压高,所以难有较高的输出摆幅.由于增益自举运放需引入子运放,结构较复杂,并引入较高的功耗,通常只在高精度高位数增益数模单元设计中采用.单级折叠式共源共栅结构又达不到所设计增益要求.故笔者采用一种特殊的两级米勒补偿运算放大器,比传统米勒补偿运放拥有更高的带宽和相位裕度,更高的输出摆幅及对应增益,同时输入管用N沟道金属氧化物半导体(N-channel Metal Oxide Semiconductor,NMOS)管,可以有效地提高电流跨导利用率[8-9].

2.1运算跨导放大器小信号建模及分析

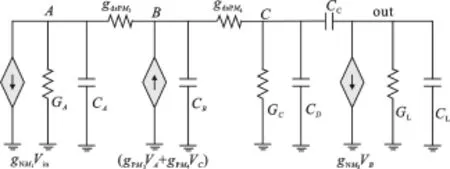

笔者所设计的运算跨导放大器如图2所示.第1级为折叠共源共栅级,第2级为差分共源级,采用动态共模反馈电路稳定两级的输出共模,米勒补偿电容位置在非小信号通路一侧的N M4、N M5管的源端,对运算跨导放大器进行小信号电路等效.小信号等效电路图如图3所示.

图 运算跨导放大器电路图

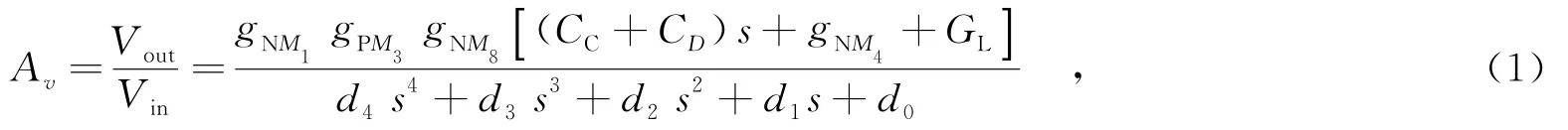

图3中,gm为MOS管跨导,gds为源漏等效跨导.CA、CB、CD为A、B、C点的总寄生电容,GA、GC为A、C点的等效跨导,CC为改善的米勒补偿电容,CL为输出等效负载.传输函数可表示为其中,d4,d3,d2,d1,d0为已知系数,s为传输函数.但由于其繁杂,在本设计中可以假定gm≫gds,且gNM4足够大,同时(CC,CL)>(CA,CB,CD),通过化简得到运放的零点z和极点p的表达式为

图3 运算跨导放大器小信号等效电路图

其中,GBC为B、C间的跨导,零点z为左半平面零点,极点p1、p2为左半平面主极点和次极点,极点p3为左半平面共轭极点,根据式(1)分母系数不同而变化.米勒电容和栅寄生电容CC>CB≫CA,并且由于共栅管N M4、N M5对第2级输入端与米勒电容和负载的隔离作用,与传统米勒补偿相比,次主极点p2的位置更远,所以达到同样的单位增益带宽所需的补偿电容或第2级跨导更小,同时引入左半平面零点,其位置可根据增益带宽调节,改善相位裕度.

2.2MATLAB建模及gm/Id方法优化计算MOS管尺寸

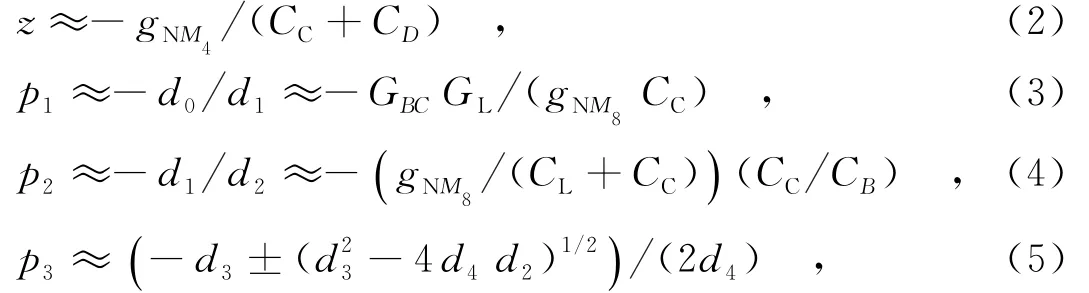

图4 gm1与gm8与CC变化关系图

根据运放有限增益和有限带宽造成的静态及动态误差,可以初步确立运放的增益为78 dB以上,运放的单位增益带宽(WGB)为600 MHz以上.首先确定补偿电容CC的值.系统单级点近似得到的WGB表达式为WGB=gNM1(2πCC).引入的米勒补偿电容应该使次级点远远高于WGB,一般p2极点位置可取3倍的WGB,利用MATLAB计算以CC作为变量下gNM1与g N M 8同CC的关系.当(gNM1+gNM8)最小时,可以在保证相位裕度不变的同时获得运放最小功耗.根据实际经验可估算寄生电容CB≈100 f F,通过MATLAB工具计算不同CC下保持相位裕度的gm变化,如图4所示.当取(gNM1+gNM8)最小值时,CC≈200 f F,从而得出两级输入管跨导gNM1≈0.8 m S,gNM8≈2.1 m S.

折叠共栅支路电流Id2=INM6=RSCC=(0.9V/1ns)×200fF=180μA,RS为信号压摆率.根据gm/Id表,可以取两输入管为最小沟道长度,且分配NM1与NM8同为过驱动电压Vov=0.2V,从而得出折叠输入支路为INM1=gNM 1/(gNM /1Id1)≈103μA;第2级输入支路电流为INM1=gNM 8/(gNM 8 Id1)≈288μA.可得出NM1与NM8宽长比(W/L)NM1=Id1/(Id1/W)≈(3μm/180nm),(W/L)NM8=Id3/(Id3/W)≈(6.5μm180nm).

将计算所得的MOS管尺寸带入仿真环境下,仿真结果表明,运算跨导放大器具有82 dB的增益,单位增益带宽为620 MHz,相位裕度为72°,在差分摆幅为1.5 V时,运算跨导放大器的增益仍有80 dB,满足设计要求.

3 比较器优化设计

传统及所改进比较器如图5所示.传统结构在复位阶段的信号Reset为零,管子M9、M10闭合将输出复位至高电位,而需M5、M6先将源端寄生电容充电,导致输出端复位所需时间增加.笔者所提出的结构在M5、M6的源端引入复位开关,直接拉至高电平,从而省略其寄生电容充电所耗时间,提高了复位速度[10].

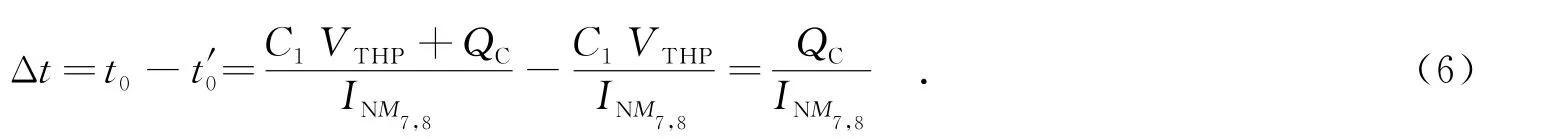

在比较相初期,由于输入及参考电压引入差导致的M5、M6漏电流不同,输出端Vout+和Vout-开始时刻下降速率不同,直到某输出端下降至(VDD-VTHP),此时M10、M11开始导通,正反馈环路形成.但由于PMOS管M9、M12在比较相开始时刻关断,开关电荷注入导致初始时刻Vout电压上升.初期进入正反馈所耗时间t0为,其中C1为比较器输出端负载及寄生电容,QC为开关电荷注入量.笔者所提出的结构用优化的传输门代替PMOS开关,具有更好的导通线性度以及更低的导通电阻,减少了导通时间,同时由于传输门的电荷补偿作用,几乎无电荷注入.与传统结构相比,节省的时间为

在比较相后期,由于锁存器M5、M6、M7、M8的增强作用,最终导致放电速度快的管子同侧输出端电压变为零,另一端差分输出变为1,实现了比较功能.

图5 传统的与所提出的比较器电路图

4 测试结果

基于0.18μm 1.8 V CMOS工艺,对笔者设计的电路作为流水线模数转换器的第1级增益数模单元进行了流片验证,芯片照片如图6(a)所示,增益数模单元有效面积为0.049 mm2.如图6(b)所示,在电源电压)为1.8 V、采样率为80 MHz、输入正弦信号频率为35 MHz时,8位模数转换器的实际有效位数为7.83位,证明笔者所设计的增益数模单元有效位数超过7.83位,满足高速中精度流水线模数转换器设计要求.

表1给出了笔者与文献[4,11]中所设计8位模数转换器整体特性.与文献[4]中提出的时间域子流水线级对比,笔者设计的增益数模单元结构具有更高的模拟余量精度和更高的采样速率,适用于高速信号处理;同时与文献[11]中1.5位增益数模单元相比,笔者设计的电路具有更低的功耗和更大的信号摆幅,适合于在低功耗和高信号摆幅下应用.

表1 所实现8位模数转换器与参考文献中的数模转换器性能对比

图6 第1级增益数模单元的版图照片及模数转换器整体测试快速傅里叶变换频谱图

5 总 结

查表设计方法来优化功耗.同时,提出一种改进的高速动态锁存比较器来节省子模数转换器静态功耗.流片后的8位流水线模数转换器在输入频率为35 MHz时,有效位数为7.83位,证明所设计的增益数模单元具有优越的性能.

[1]OH T,VENKATRAM H,MOON U K.A Time-based Pipelined ADC Using Both Voltage and Time Domain Information[J].IEEE Journal of Solid-state Circuits,2014,49(4):961-971.

[2]杨银堂,李迪,石立春,等.一种用于14位1.28MS/sΣΔADC的数字抽取滤波器设计[J].西安电子科技大学学报,2010,37(2):315-319. YANG Yintang,LI Di,SHI Lichun,et al.Decimation Filter Design for 14-bit 1.28MS/s Sigma-delta ADC[J].Journal of Xidian University,2010,37(2):315-319.

[3]杨银堂,袁俊,张钊锋,等.256 MHz采样71 dB动态范围连续时间ΣΔADC设计[J].西安电子科技大学学报,2015,42(1):10-15. YANG Yintang,YUAN Jun,ZHANG Zhaofeng,et al.Continuous TimeΣΔADC Design with 256 MHz Sampling and 71 dB DR[J].Journal of Xidian University,2015,42(1):10-15.

[4]PASHAEEFAR M,ASHTIANI S J.A Novel 8-bit 20-MS/s Folded Residue Amplification Based Pipelined ADC[J]. Analog Integrated Circuits and Signal Processing,2014,79(1):177-182.

[5]SILVEIRA F,FLANDRE D,JESPERS P G A.A gm/ID Based Methodology for the Design of CMOS Analog Circuits and Its Application to the Synthesis of a Silicon-on-insulator Micropower OTA[J].IEEE Journal of Solid-state Circuits,1996,31(9):1314-1319.

[6]YANG W,KELLY D,MEHR I,et al.A 3-V 340-m W 14-b 75-M Sample/s CMOS ADC with 85-dB SFDR at Nyquist Input[J].IEEE Journal of Solid-state Circuits,2001,36(12):1931-1936.

[7]SHU G H,FAN M J,SHU C,et al.A 12-bit 50-MS/s Pipelined Analog-to-Digital Converter in 65nm CMOS[C]// IEEE International Conference on Solid-state and Integrated Circuit Technology.New York:IEEE,2010:563-565.

[8]YAVARI M,SHOAEI O,SVELTO F.Hybrid Cascode Compensation for Two-stage CMOS Operational Amplifiers [C]//IEEE International Symposium on Circuits and Systems.New York:IEEE,2005:23-26.

[9]ARDAKANI H A,DEHGHANI R,ASGARI V.A Compensation Strategy for Two-stage Operational Transconductance Amplifiers Based on Zero Splitting[C]//22nd Iranian Conference on the Electrical Engineering.Iranian:ICEE,2014:20-22.

[10]LIU S B,ZHU Z M,YANG Y T,et al.A High Speed Low Power Low Offset Dynamic Comparator Used in SHA-less Pipelined ADC[J].Journal of Semiconductors,2014,5:114-121.

[11]LEE H Y,LIU S L.A 8-bit 140MS/s Pipelined ADC Using Folded Sample-and-Hold Stage[C]//2007 IEEE International Conference on Electron Devices and Solid-state Circuits.Piscataway:IEEE,2007:357-360.

(编辑:郭 华)

Optimum design of the MDAC circuit for the 8 bit 80 MS/s pipelined A/D converter

DONG Siwan,ZHU Zhangming,LIU Minjie,YANG Yintang

(School of Microelectronics,Xidian Univ.,Xi’an 710071,China)

A high speed and medium accuracy multiplying digital-to-analog converter(MDAC)circuit optimization design is presented for meeting the requirements of the 8 bit,80 MS/s pipelined analog-todigital(A/D)converter.An optimized transmission gate is adopted to improve the linearity of the MDAC circuit.In view of the high gain two-stage operational amplifier,design method in wideband operational amplifier design optimization is proposed and the settling time and power consumption of operational amplifier can be effectively decreased In addition,an improved high speed dynamic comparator is used in this design Fabricated in a 1.8 V 0.18μm CMOS process,this A/D converter with the proposed MDAC circuit achieves a signal to noise and distortion ratio(SNDR)of 54.6 dB and an effective number of bits (ENOB)of 7.83 bit with a 35 MHz input signal at the 80 MHz sample rate.

multiplying digital-to-analog converter;amplifier optimization;transmission gate;dynamic comparator;pipelined analog-to-digital converter

TN431.2

A

1001-2400(2016)01-0162-05

10.3969/j.issn.1001-2400.2016.01.029

2015-03-17

国家自然科学基金资助项目(61234002,61322405,61306044,61376033)

董嗣万(1988-),男,西安电子科技大学博士研究生,E-mail:dsiwan@163.com.