一种可编程全数字锁相环的设计与实现

2016-09-07李凤华刘丹丹单长虹

李凤华,刘丹丹,单长虹

(南华大学 电气工程学院,湖南 衡阳 421001)

一种可编程全数字锁相环的设计与实现

李凤华,刘丹丹,单长虹

(南华大学 电气工程学院,湖南 衡阳421001)

针对传统的全数字锁相环电路参数不可调、锁相速度慢及锁相范围窄的缺点,提出了一种可编程全数字锁相环。采用电子设计自动化技术完成了该系统设计,并对所设计的电路进行了计算机仿真与分析,最后,采用FPGA予以硬件电路的实现;系统仿真与硬件实验证明,该锁相环中数字滤波器和数控振荡器的参数可以自主设定,改变数字滤波器的参数可加快锁相速度,改变数控振荡器的参数可扩大锁相范围;该锁相环具有锁相速度快、锁相范围宽、电路结构简单、参数设计灵活和易于集成等优点,可适用于许多不同用途的领域。

全数字锁相环;电子设计自动化;计算机仿真;可编程

0 引言

锁相环路已在模拟和数字通信等各个方面得到了较为广泛的应用,比如其同步特性就保证了通信中系统的稳定性[1]。随着集成电路的发展,部分模拟锁相环也渐渐被数字锁相环取代[2]。与模拟锁相环相比,数字锁相环易于集成、可靠性高、设计方便、价格优廉,并且有很强的通用性,克服了模拟锁相环中对温度敏感、直流零点漂移、抗干扰性能差和无法嵌入SOC构成片内锁相环系统等缺点[3-4]。但现有的一些全数字锁相环的锁相范围窄、用途单一、通用性不强。且设计方案复杂,修改电路参数不易。对于用于不同用途的锁相环而言,需要重新进行电路系统的设计,若要满足锁相系统的锁相速度和锁相范围等方面的性能指标要求,整个设计过程就比较复杂[5-6]。

本文提出了一种可编程的全数字锁相环,

介绍了它的系统结构、工作原理及各分模块的设计方案。利用Quartus II软件工具对电路系统进行了仿真验证,并根据仿真结果对电路参数的变化对锁相系统的影响进行了分析。最后,给出了基于FPGA芯片实现的系统硬件测试结果[7]。

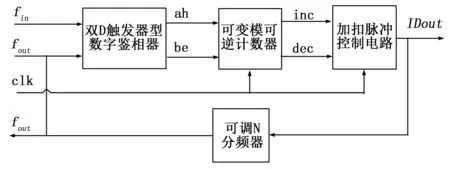

1 可编程全数字锁相环的工作原理

可编程全数字锁相环主要由双D触发器型数字鉴相器、可变模可逆计数器、加扣脉冲控制电路和可调N分频器构成[8-10]。其结构框图如图1所示。

图1 可编程全数字锁相环的结构框图

双D触发器型数字鉴相器通过检测输入信号fin和输出信号fout的上升沿,输出检测到的相位超前信号ah或滞后信号be及相位误差信号。相位超前信号ah为高电平时,可逆计数器进行加计数,当加计数值达到可逆计数器预设的模值m后,环路滤波器输出对应的加脉冲控制信号inc;相位滞后信号be为高电平时,可逆计数器进行减计数,当减计数值达到预设模值m后,环路滤波器输出减脉冲控制信号dec。加扣脉冲控制电路根据环路滤波器输出的脉冲加、减控制信号,通过加上或减去一个系统时钟周期去调整输出信号的相位。可调N分频器对加扣脉冲控制电路调整后的输出信号IDout进行分频,并将其输出信号fout送入数字鉴相器进行下一周期的比较,最终实现环路的锁定。

在该全数字锁相环系统中,数字滤波器和分频器的参数是可编程的。调节变模可逆计数器中的模值m,可使输出加扣脉冲控制信号的频率升高,进而加快相位的调整,提高了锁相速度。改变分频系数N,使得环路中心频率可调,可实现对不同频率的输入信号进行锁定。

2 各模块的设计与仿真

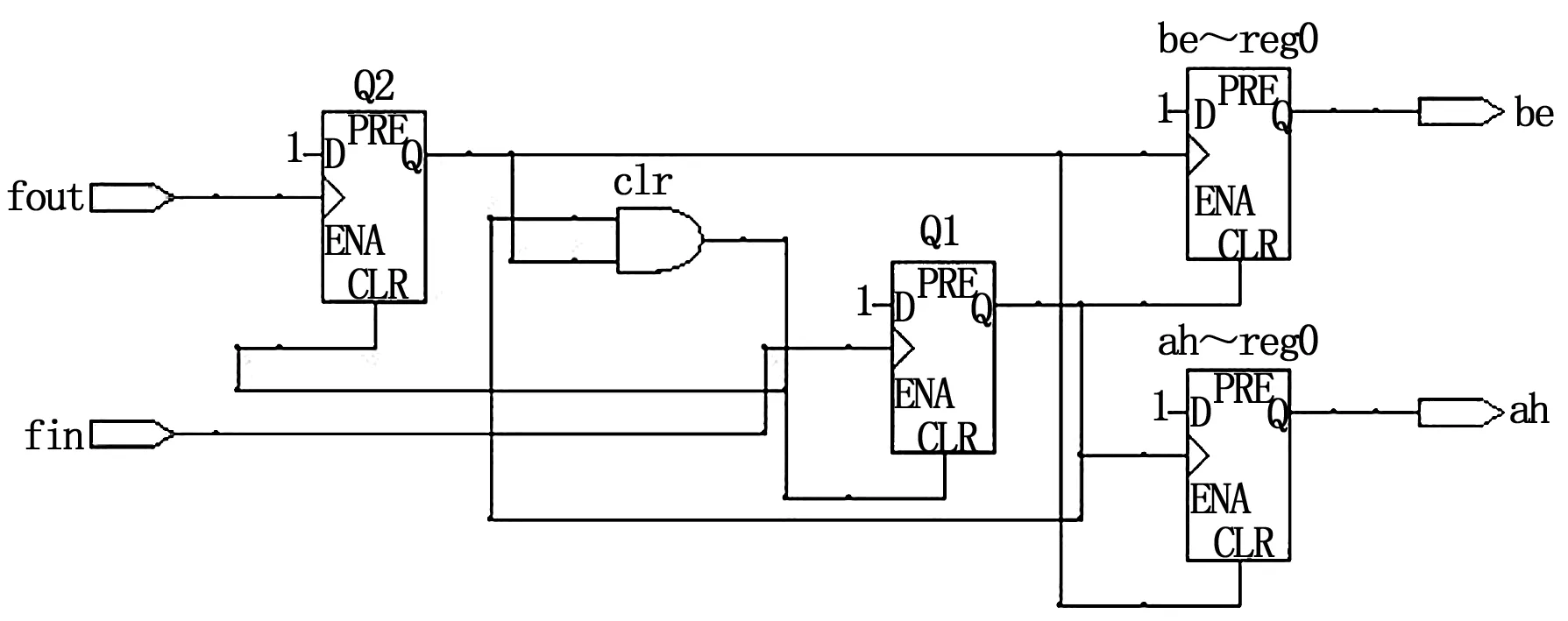

2.1双D触发器型数字鉴相器

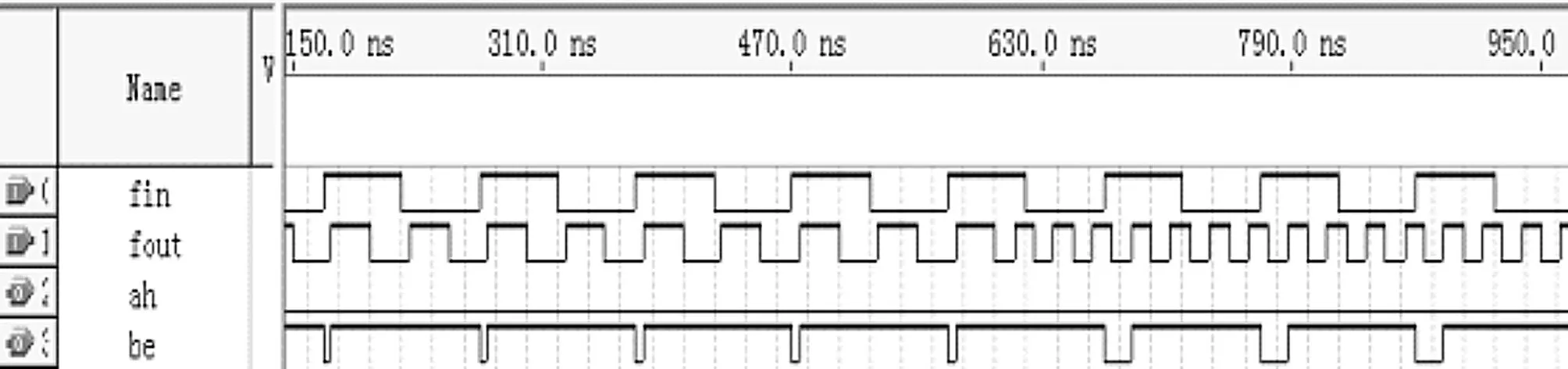

双D触发器型数字鉴相器采用VHDL语言进行编程设计,通过检测输入与输出信号的上升沿,判断出误差相位极性,并生成反映输入与输出信号之间相位超前或滞后的相差信号,其RTL级电路图如图2所示。图3、图4为鉴相器的功能仿真波形。

图2 双D触发器数字鉴相器的RTL级电路图

图3 输入与输出信号频率相同、相位不同时的波形图

图4 输入与输出信号频率不相同时的波形图

由图4可知,双D触发器型数字鉴相器不仅具有鉴相功能,而且也有鉴频功能。这是其它类型的数字鉴相器所没有的优点。

2.2可变模数字滤波器

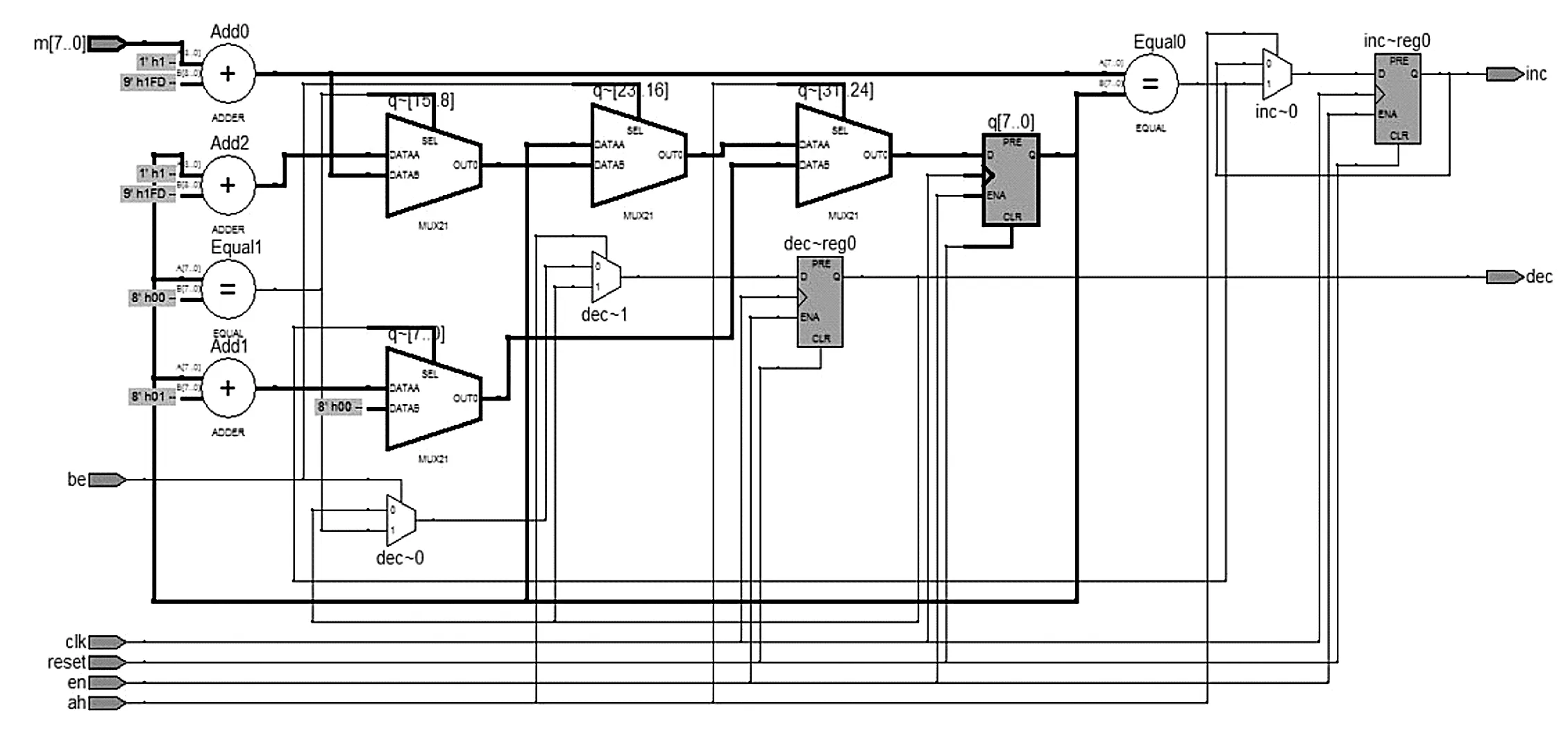

数字滤波器是由一个可变模可逆计数器构成,采用VHDL语言进行编程设计。其计数方向的控制信号来自鉴相器的输出信号。其RTL级电路图如图5所示。

图5 变模数字滤波器的RTL级电路图

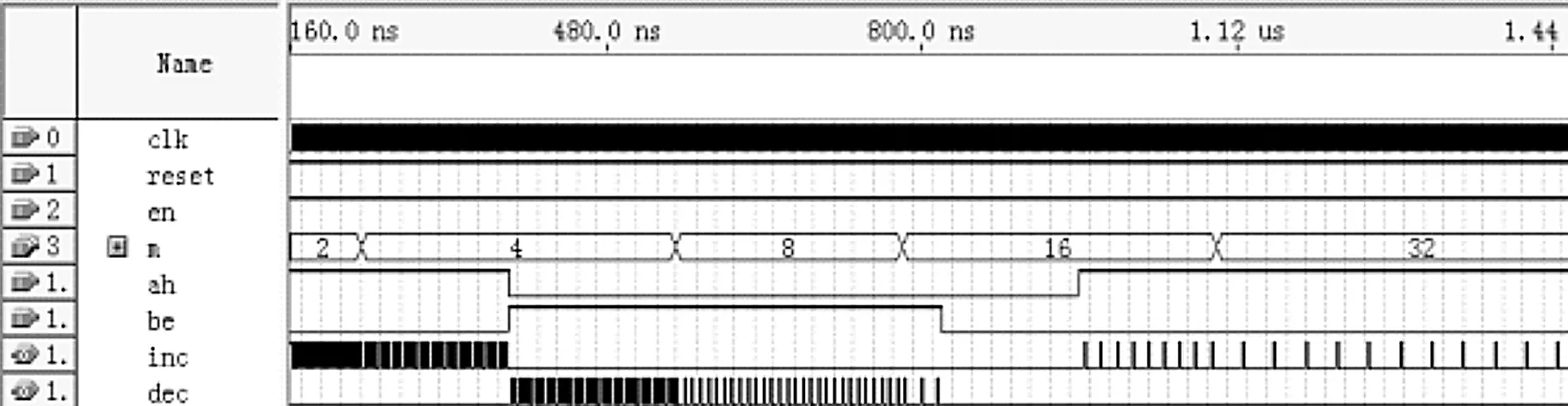

数字滤波器的仿真波形如图6所示。不同的模值m表示数字滤波器中计数器的不同的计数深度,m的取值影响着锁相环路的锁相速度。当输入信号与输出信号的相位误差较大时,如果m取较大值,可逆计数器的计数周期就较长,其输出加减脉冲信号的频率就较低,锁定速度就比较慢;相反,若m取值较小时,可逆计数器的计数周期就较短,输出加减脉冲的频率就会较高,锁相速度就会加快。因此,可逆计数器模值的选择对于改善锁相系统的性能至关重要。由数字滤波器仿真波形图可以看出,当可逆计数器的模值分别为2、4、8、16、32时,输出信号inc或dec的频率逐渐减小。由此可见,本设计方案可实现数字滤波器的参数可调,改变滤波器输出控制信号的频率。

图6 变模数字滤波器的波形仿真图

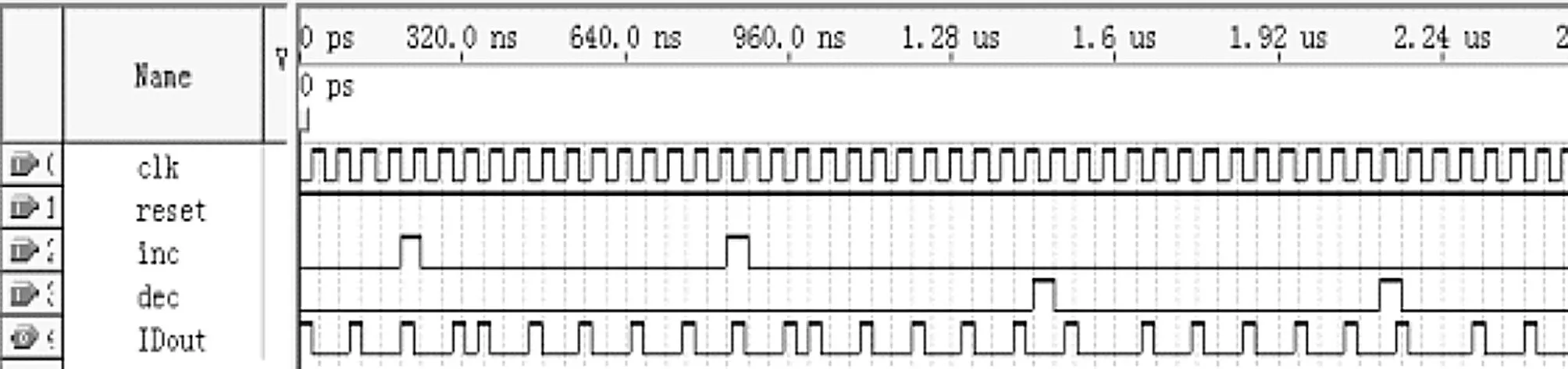

2.3加扣脉冲控制电路

加扣脉冲控制电路也是采用VHDL语言进行编程设计。数字滤波器输出的进位和借位脉冲信号作为加扣脉冲电路的控制信号,IDout为其输出信号。当进位信号inc为高电平时,系统会在加扣脉冲电路输出信号的下一个周期加上一个时钟脉冲,使得输出信号的相位提前;当借位信号dec为高电平时,系统会在加扣脉冲电路输出信号的下一个周期减去一个时钟脉 冲,使得输出信号的相位延后;当inc与dec都为低电平时,该电路只对系统时钟信号进行二分频。其仿真波形如7所示。

图7 加扣脉冲数控振荡器的波形仿真图

2.4可调N分频器

系统时钟的二分频信号经由加扣脉冲控制器调节之后的输出信号IDout,作为可调N分频器的时钟输入信号。根据输入信号的频率变化,选择合适的分频值送入分频器,就可改变环路的中心频率,从而扩展系统的锁频范围。由于分频器的分频值N可调,设计者可以根据被锁信号频率的差异来选择相应的分频值,实现对不同频率信号的锁定。

图8 N分频器的波形仿真图

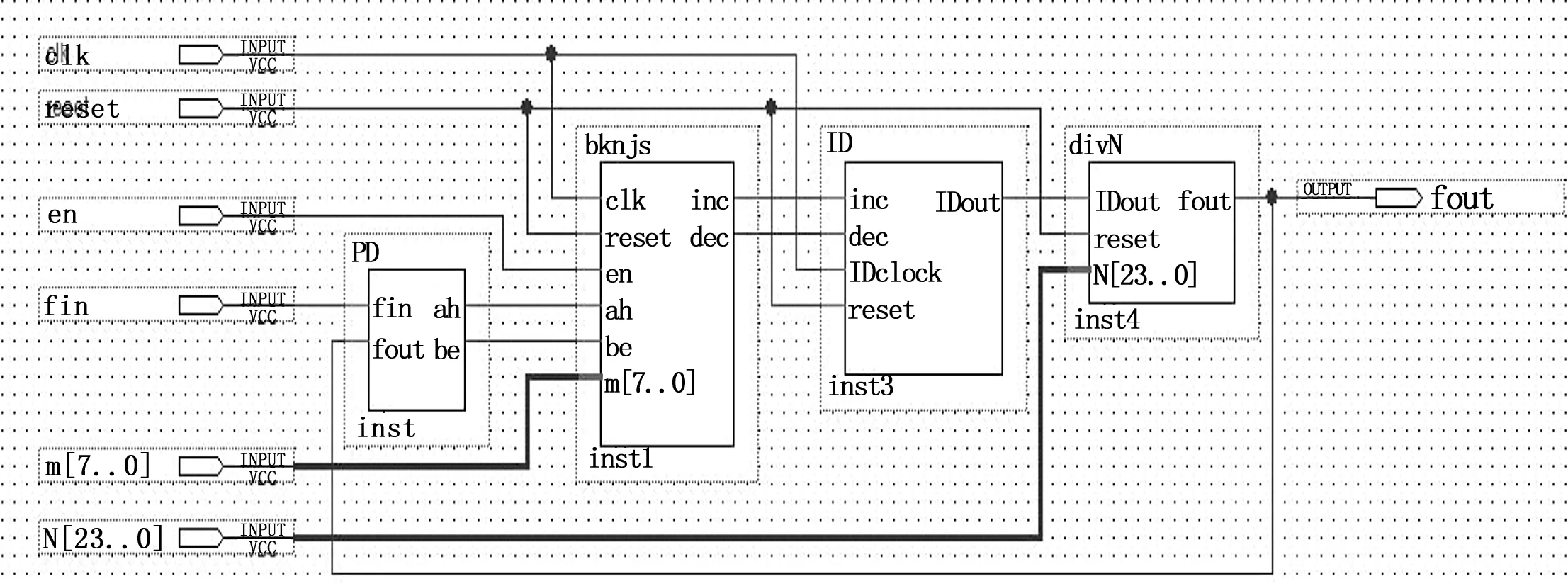

3 整体设计与仿真

系统的整体设计采用自顶而下的设计方法,首先,用VHDL语言对各模块进行编程设计,在完成各模块的设计之后,再将各模块连接起来进行系统设计。该全数字锁相系统的顶层电路结构如图9所示。其中PD模块为数字鉴相器,bknjs 模块为可变模可逆计数器,ID模块为加扣脉冲电路ID,divN模块为可调分频器。

图9 可编程全数字锁相环的顶层电路图

系统时钟的频率取20 MHz,输入信号分别取2.5 MHz和100 kHz时,对该锁相系统进行整体仿真。其中clk为系统时钟信号,reset为复位信号,en为使能信号,fin和fout为分别为系统的输入输出信号,m为环路滤波器中可逆计数器的模值,N为可调分频器的分频系数。

图10 fin=2.5 MHz, m=23,N=4时的波形仿真图

图11 fin=2.5 MHz,m=2,N=4时的波形仿真图

图10和图11中输入信号频率为2.5 MHz,分频值N取4,数字滤波器的模值m分别取23和2。由图10中可见,当输入信号相位发生跳变时,锁相环需要十4个输入信号的周期实现锁定。由图11中可见,当输入信号的相位发生跳变时,锁相环只需3个周期就能锁定。比较图10和图11的仿真结果可知,减小数字滤波器的模值可以加快锁相速度,改善系统的性能。

图12 fin=100 kHz,m=23,N=100时的波形图

图12中输入信号频率为100 kHz,数字滤波器模值m取23,分频值取100。由该系统仿真结果可知,调节分频器的分频系数,能够改变系统的中心频率,从而可扩展系统的锁频范围。

4 硬件测试结果

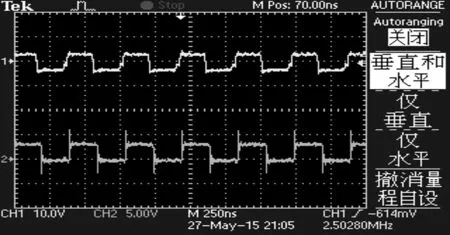

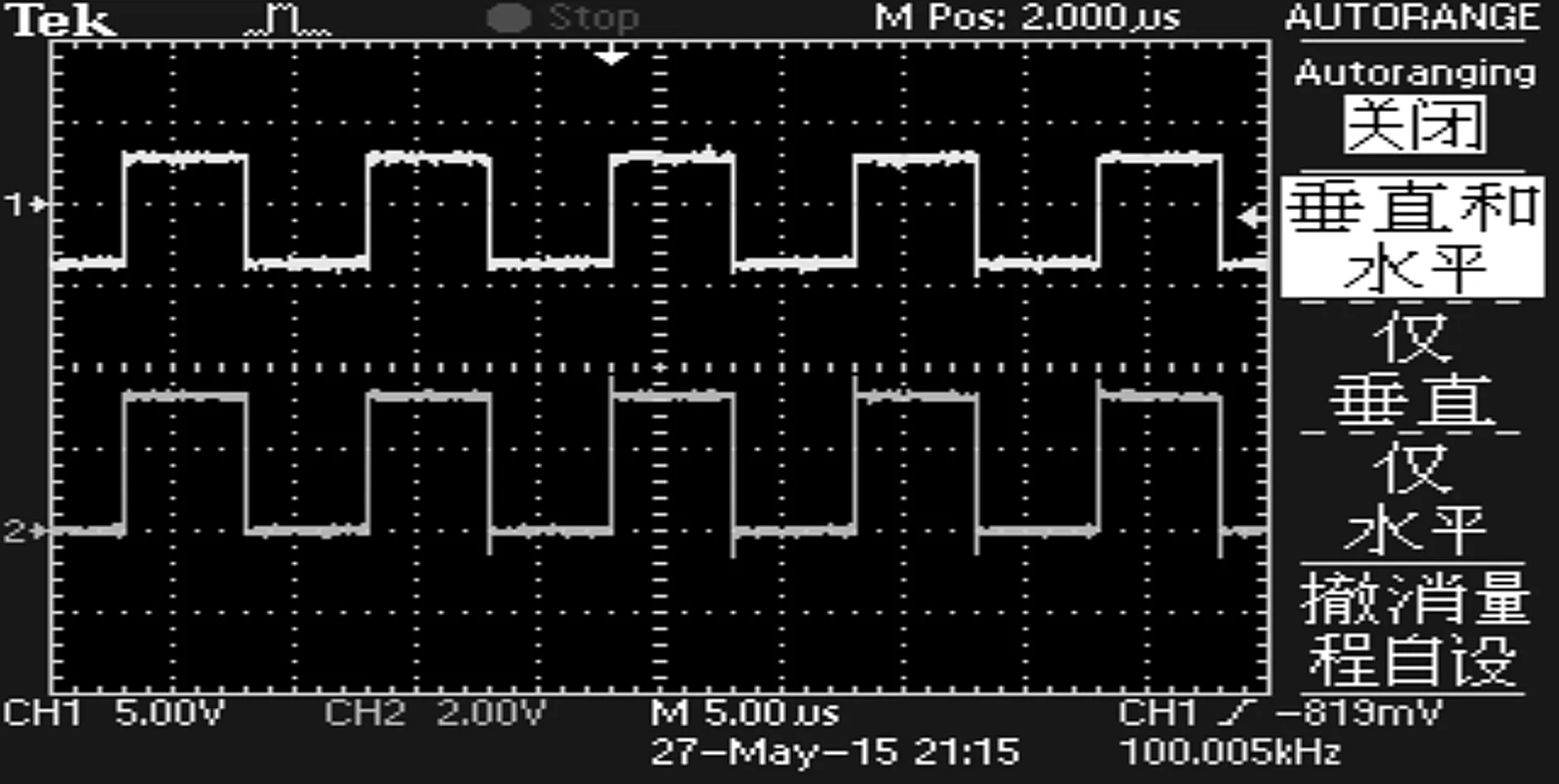

采用EP1C6Q240C8芯片对系统进行硬件电路的验证,其中系统的时钟频率为20 MHz。图13为输入信号频率为2.5 MHz,数字滤波器模值为23,分频值为4时的硬件测试结果。图14为输入信号频率为100 kHz,数字滤波器模值为23,分频值为100时的硬件测试结果。

图13 fin=2.5 MHz时的硬件测试波形图

图14 fin=100 kHz时的硬件测试波形图

以上硬件测试结果表明,当被锁输入信号的频率不同时,可选择不同的分频值N和合适的数字滤波器参数,该环路系统都能实现相位和频率的跟踪锁定。该系统的硬件测试与系统仿真结果是一致的,都证实了该设计方案是正确与可行的。

5 结束语

采用EDA技术完成了可编程全数字锁相环的系统设计。该锁相系统中数字滤波器的参数可调,当输入信号频率为2.5 MHz时,若选择m=23,N=4,锁相环需要14个输入信号的周期实现锁定;而若选择m=2,N=4,锁相环可在输入信号的3个周期内就能锁定。同时,数控振荡器中分频器的系数可调,若分别选择分频系数N为100或4时,锁相环的锁相频率分别为100 kHz和2.5 MHz。该锁相环路具有锁相速度快、锁相范围宽、电路结构简单和易于集成等优点。同时,系统参数设计灵活、方便,可以根据不同的锁相范围和用途,选择相应的设计参数,以实现锁相环在不同的频率范围内快速锁定。

[1]王辉,宋昌统.基于自适应状态聚集Q学习的移动机器人动态规划方法[J]. 计算机测量与控制, 2014(10):3418-3422.

[2]彭咏龙, 路智斌, 李亚斌. 基于 FPGA 的改进型全数字锁相环的设计[J]. 电源技术, 2015, 39(2):410-412.

[3]赵玮, 齐向东. 基于VHDL的数字锁相环设计及Modelsim仿真[J]. 机械工程与自动化, 2013(2):57-59.

[4]王文理, 张霞. 基于FPGA 的全数字锁相环的设计[J]. 电子设计工程,2009,17(1): 39-40.

[5]Chen Y W, Hong H C. A fast-locking all-digital phase locked loop in 90nm CMOS for Gigascale systems[A]. Circuits and Systems (ISCAS)[C]. IEEE, 2014. 1134-1137.

[6]Elkholy A, Anand T, Choi W S, Elshazly A,Hanumolu P K. A 3.7 mW low-noise wide-bandwidth 4.5 GHz digital fractional-N PLL using time amplifier-based TDC[J]. Solid-State Circuits, IEEE, 2015,50(4):867-881.

[7] 高建明.自适应模糊控制的自平衡机器人设计[J].计算机测量与控制,2015(3):773-776.

[8] 黄保瑞, 杨世平. 基于FPGA 的全数字锁相环设计[J]. 电子测试, 2014(8X):33-34 .

[9] Geng H, Xu D, Wu B. A novel hardware-based all-digital phase-locked loop applied to grid-connected power converters[J]. Industrial Electronics, IEEE, 2011,58(5):1737-1745.

[10] Singhal A, Madhu C, Kumar V. Designs of all digital phase locked loop[A]. Engineering and Computational Sciences (RAECS)[C]. IEEE, 2014.1-5.

Design and Implementation of a Programmable ADPLL

Li Fenghua,Liu Dandan,Shan Changhong

(College of Electrical Engineering, University of South China, Hengyang421001,China)

To avoid the shortcomings of traditional all digital phase-locked loop (ADPLL) on circuit parameters adjustment, low lock speed and narrow lock range, a programmable DPLL is proposed. The system design is completed by using electronic design automation(EDA) technology, while simulation and analysis of the DPLL circuit are carried through computer aided technology, and finally, the system is implemented on a FPGA hardware platform. System simulation and hardware test results verify that parameters of the digital filter and controlled oscillator of the system can be adjusted through programming, i.e. changing parameters of the digital filter leads to raising the lock speed, while changing that of the digital oscillator gives rise to broadening the lock range. The phase-locked loop is characteristic of its high lock-speed, wide lock range, simple circuit structure, flexible parameters design, and easy system integration, etc., and also it can be applied to many different areas.

all digital phase-locked loop(ADPLL); electronic design automation(EDA); computer aided simulation; programmable

2015-07-20;

2015-08-25。

湖南省教育厅重点项目资助(14A119)。

李凤华(1990-),女,河南商丘人,硕士研究生,主要从事电路集成与系统设计方向的研究。

单长虹(1957-),男,湖南衡阳人,教授,硕士研究生导师,主要从事电路集成与系统设计方向的研究。

1671-4598(2016)01-0243-03

10.16526/j.cnki.11-4762/tp.2016.01.067

TB114.3

A