厚膜电阻制造技术研究

2016-09-07尤广为邹建安

尤广为,邹建安,肖 雷

(中国兵器工业第214研究所,安徽 蚌埠 233042)

厚膜电阻制造技术研究

尤广为,邹建安,肖雷

(中国兵器工业第214研究所,安徽 蚌埠 233042)

针对传统厚膜混合集成电路在厚膜电阻制造过程中存在厚膜电阻阻值离散性大、印刷效率低及产生大量试阻片浪费等问题,特对厚膜制造技术进行了研究。通过对厚膜电阻设计和制造原理进行分析,发现厚膜电阻印刷膜厚对其阻值至关重要,因此,决定采用厚膜电阻印刷膜厚监测以达到控制厚膜电阻阻值的方式,先对厚膜电阻印刷时膜厚控制范围进行确定,同时根据所使用的厚膜电阻浆料方阻的不同,对厚膜电阻印刷膜厚控制范围进行调整,然后依据调整后的膜厚控制范围直接进行厚膜电阻印刷。经过实际验证,采用这种加工方式使厚膜电阻加工效率和成品率得到了大大提高,同时厚膜电阻阻值一致性也得到了很大改善。

厚膜混合集成电路;厚膜电阻印刷;膜厚测量

厚膜混合集成电路中厚膜电阻的制作方法是通过丝网印刷机的规律往返动作以及丝网掩模,把厚膜电阻浆料均匀地沉积在陶瓷基片上,以获得清晰完整的印刷图形,形成均匀且膜厚可控的各类厚膜浆料湿膜;再通过室温下静置流平和红外干燥炉的干燥,使浆料中有机载体挥发从而使印刷出的湿膜变成干膜;最后通过高温烧结炉进行烧结,使干膜经过一系列物理、化学反应,形成符合设计要求的厚膜电阻烧结膜层。其电阻阻值一般控制在产品标称值的60%~90%[1]。

通过理论分析和实际验证可知,厚膜混合集成电路中厚膜电阻的膜厚与其电阻阻值之间存在关联性:当厚膜电阻膜厚越厚时,其阻值越小;厚膜电阻膜厚越薄时,其阻值越大。根据这一规律,将传统厚膜电阻制作方法进行技术改进,由原来试阻方式改进为通过膜厚控制直接印刷方式,使加工效率和成品率大大提高,同时厚膜电阻阻值控制在70%~80%,使厚膜电阻质量一致性得到很大提高。

1 存在的问题

在对厚膜混合集成电路厚膜电阻加工时,通常采取小样试阻方式印刷电阻,当小样试阻阻值达到标称值的60%~90%时,方可进行正式试量印刷。采用此种厚膜电阻加工技术存在如下问题。

1)试阻过程耗时及浪费试阻片。厚膜电阻在批量印刷过程前应进行试阻,要求阻值控制在60%~90%,如厚膜电阻阻值达不到要求,则需要重新调机再进行试阻,直至达到要求为止。在试阻过程中,产生3~9只试阻片(每次需要3只试阻片,如试阻3次则需要9只试阻片),而这些试阻片只能作为废片处理,同时在此试阻过程中浪费大量时间,每试阻1次至少需要1.5 h(印刷10 min,干燥15 min,烧结1 h,阻值测量5 min)。

2)印刷时膜厚偏差。厚膜电阻在批量印刷时,会受到印刷机状态、厚膜电阻浆料性能等参数影响,且对厚膜电阻膜厚不进行监控;因此,不同基片上厚膜电阻的膜厚存在较大偏差,导致厚膜电阻阻值偏差>5%,造成厚膜电阻阻值难以控制。

3)印刷过程试烧耗时及浪费试阻片。为防止整批印刷中相应参数漂移而导致阻值超差,要求每印刷200片试烧3片来控制阻值。采用这种控制办法是先抽样再干燥及烧结,然后对厚膜电阻阻值进行测量,这也花费了大量时间,并且造成了试烧片的浪费。

4)总烧耗时。厚膜电阻总烧前应先试烧,试烧合格才可总烧。试烧片的选取最少为5片,如果总批量>300片,则按照每200片抽取3片的方法进行选取。这也花费了大量时间,如阻值不合格,则造成试烧片浪费。

采用此种加工技术需要花费大量试阻时间,加工效率低;同时造成试阻样片浪费,导致成品率偏低;因此,有必要对厚膜电阻加工技术进行改进。

2 厚膜电阻加工技术创新

通过对厚膜电阻设计技术和加工原理进行研究,找出厚膜电阻加工技术的改进方法。

2.1厚膜电阻设计原理

厚膜电阻设计是根据产品设计任务书要求进行版图设计。先设计厚膜电阻两端导带,两端导带之间距离即为厚膜电阻长度,与两端导带搭接的电阻多少即为厚膜电阻宽度。为满足厚膜电阻阻值要求,应根据厚膜电阻设计曲线图设计出厚膜电阻的长度和宽度。

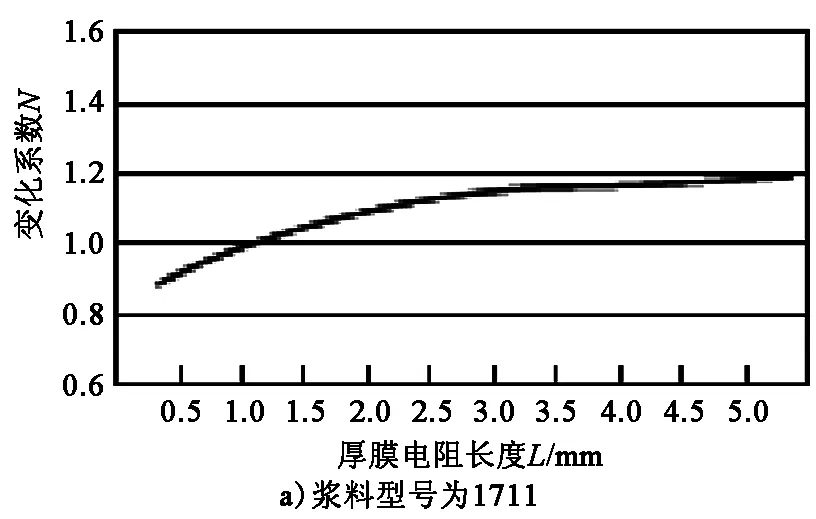

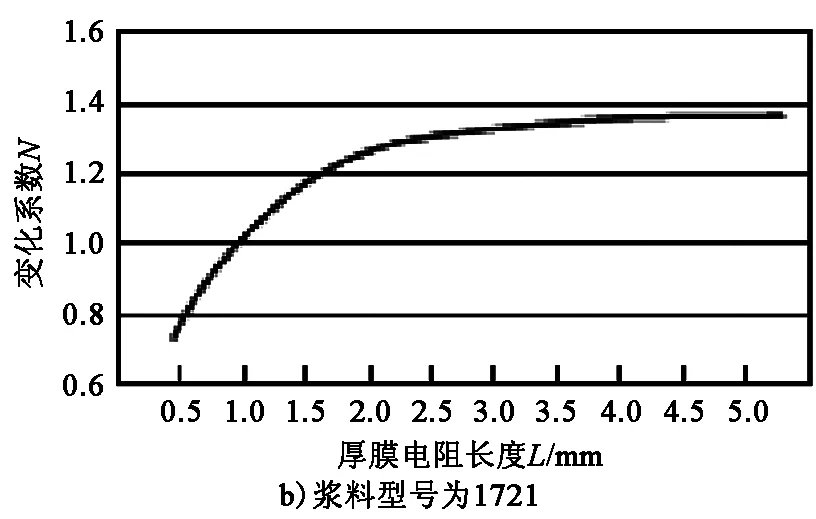

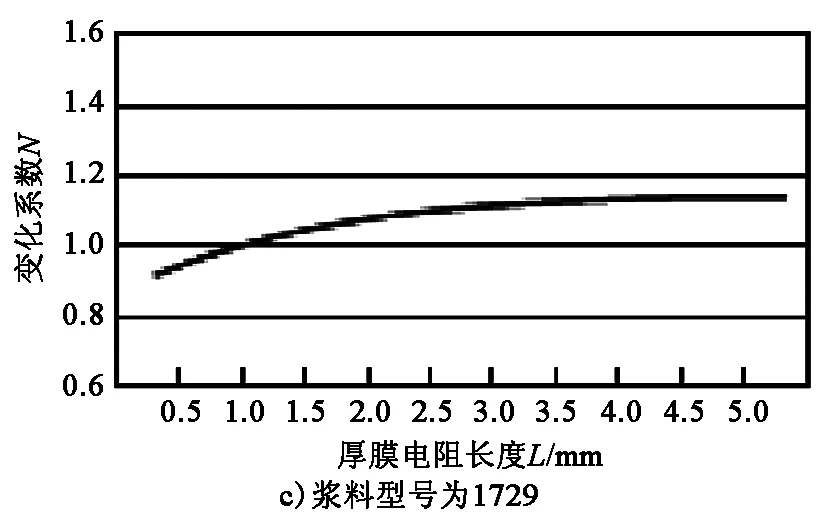

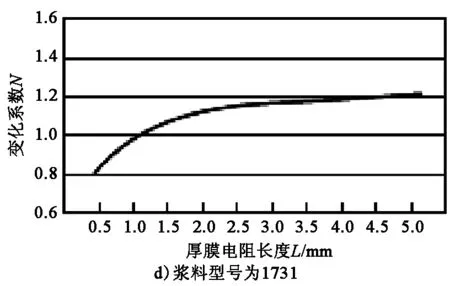

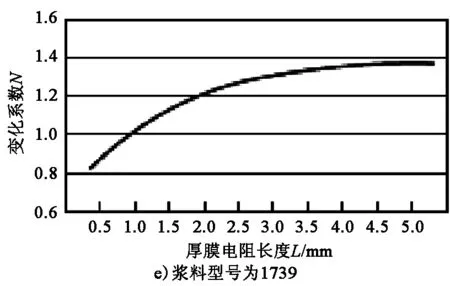

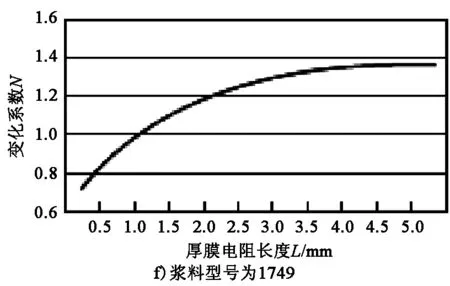

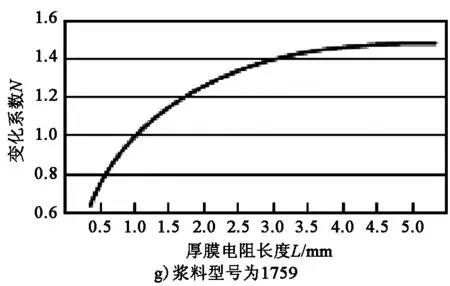

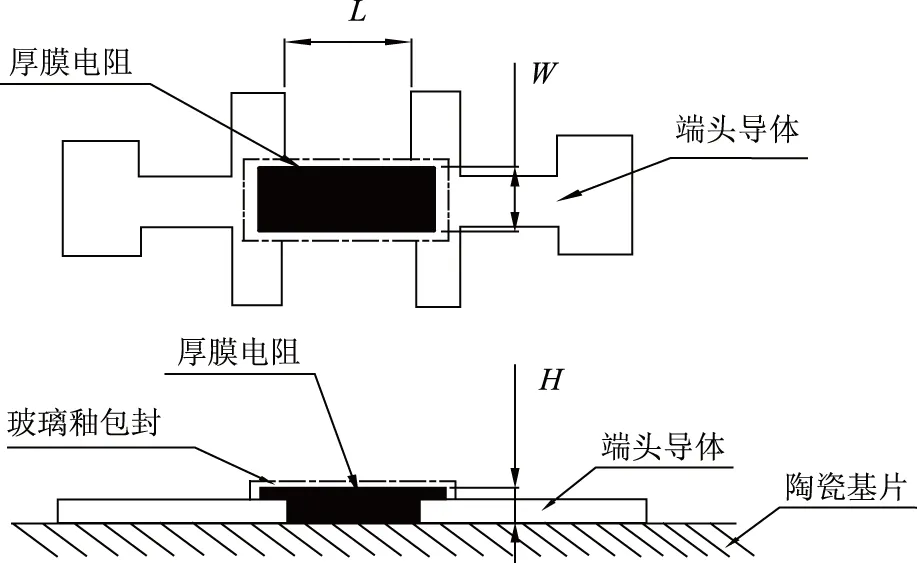

厚膜电阻设计曲线图是在厚膜电阻宽度为1 mm的情况下得出的,不同浆料型号的厚膜电阻设计曲线图如图1所示。

图1 不同浆料型号的厚膜电阻设计曲线图

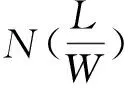

在厚膜电阻设计时,按照厚膜电阻设计计算式,并结合厚膜电阻设计曲线图,计算出产品所需要的厚膜电阻长、宽尺寸。计算式如下。

(1)

式中,R是电阻值;R□是方阻,是所采购厚膜电阻浆料1 mm2的阻值;W是厚膜电阻宽度。

例如,用方阻R□为1 kΩ/□的电阻浆料设计一个电阻值为2 kΩ的厚膜电阻。按标称值的90%(1.8 kΩ)来设计这个电阻,根据上述厚膜电阻设计曲线图,当电阻宽度W为1 mm,电阻长度L为1.5 mm时,N值为1.2。通过式1得到电阻值R=1.8 kΩ,即阻值为2 kΩ的厚膜电阻,其设计长度为1.5 mm,宽度为1.0 mm。

2.2厚膜电阻加工原理

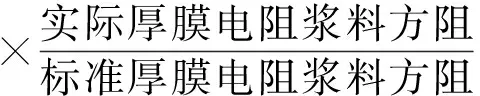

厚膜混合集成电路厚膜电阻加工是按照产品版图设计的厚膜电阻图形,将其制作在陶瓷基片上,先制作厚膜电阻两端导体,然后在2条端头导体之间印刷厚膜电阻浆料,并经过干燥烧结后形成厚膜电阻,最后在厚膜电阻体上进行玻璃釉包封。具体厚膜电阻结构图如图2所示。

图2 厚膜电阻结构图

在厚膜电阻加工时,图形尺寸已由版图设计所确定,其印刷出来的厚膜电阻长度和宽度与版图设计图形相同,此时厚膜电阻阻值大小只与实际使用的厚膜电阻浆料方阻及加工膜层厚度有关,具体如下。

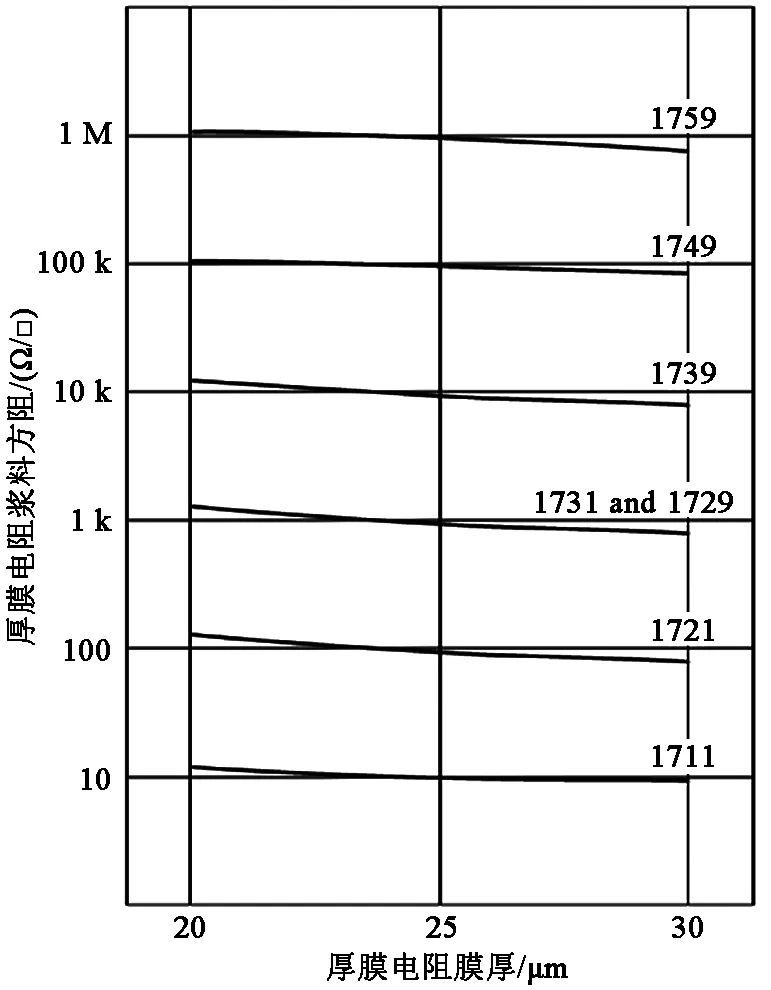

1)膜厚越厚,其阻值越小,反之阻值越大。厚膜电阻膜厚对阻值的影响曲线如图3所示。

2)所用厚膜电阻浆料方阻为90%~110%,方阻越大,其阻值越大,反之阻值越小;因此,应根据不同方阻的厚膜电阻浆料来调整厚膜电阻加工膜厚,以保证厚膜电阻阻值能得到有效控制。具体控制办法如下:

实际厚膜电阻膜厚 =

图3 厚膜电阻膜厚对阻值的影响曲线

2.3厚膜电阻加工技术改进

根据对厚膜电阻设计和加工原理进行分析,通过在厚膜电阻加工时对其膜厚进行测量,即可达到控制厚膜电阻阻值的目的,即将原试阻方式改进为膜厚控制直接印刷厚膜电阻方式。

3 厚膜电阻加工改进技术运用

3.1厚膜电阻加工膜厚确定

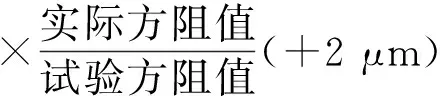

通过对某电路所需3种(10 kΩ/□、100 kΩ/□和1 MΩ/□)厚膜电阻进行加工,得出了其阻值控制在标称值的70%~80%时的膜厚平均值;同时,根据实际所使用的厚膜电阻浆料方阻,对厚膜电阻的膜厚进行调整。具体操作方法是将实际方值输入厚膜电阻膜厚控制要求表中(见表1),然后应用Excel表按照下列公式自动生成膜厚控制范围。

实际膜厚最小值=

实际膜厚最大值=

3.2厚膜电阻加工膜厚控制

按照表1规定的某产品厚膜电阻膜厚控制范围,对厚膜电阻进行成膜加工。在实际厚膜电阻印刷过程中,工艺部门操作人员根据膜厚控制范围要求对厚膜电阻进行直接印刷,同时操作人员采取膜厚测量方法对厚膜电阻进行监控,监控频次为每印刷50只抽测1只,观察其膜厚是否在控制范围内,并作好标识单独摆放。厚膜电阻膜厚实际测量图如图4所示。

表1 HGXXXX厚膜电阻膜厚控制要求表

图4 厚膜电阻膜厚实际测量图

3.3厚膜电阻加工后检测

为确保厚膜电阻阻值质量,在新采购厚膜电阻浆料在首批使用时对厚膜电阻成膜烧结进行加严控制。要求当所有电阻印刷完成后,将测量样品进行试烧,并检测其阻值是否满足文件要求。如完全满足文件要求,则将整批电路进行总烧。当再次使用时,则可以通过厚膜电阻膜厚控制方法进行直接印刷、干燥和烧结,无需再进行试烧。厚膜电阻加工后

阻值检测仪表如图5所示。

图5 厚膜电阻加工后阻值检测仪表

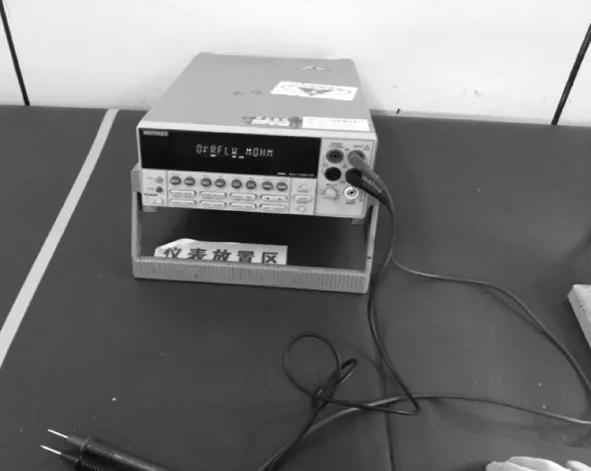

3.4厚膜电阻实际加工情况

现安排投5批XX军品电路成膜基板加工,在厚膜电阻印刷过程中,严格按照表1中所要求的膜厚进行控制,分别对5批完成成膜加工的电路进行厚膜电阻抽样测试,发现其阻值均控制70%~80%,厚膜电阻阻值一致性好(见表2)。

表2 HGXXXX厚膜电阻阻值统计表(批次:C13XX)

注:1 mil=0.025 4 mm。

4 实施效果

通过采用改进的厚膜电阻加工技术,厚膜混合集成电路中厚膜电阻加工效率、成品率以及阻值一致性均得到很大提高。

4.1提高加工效率

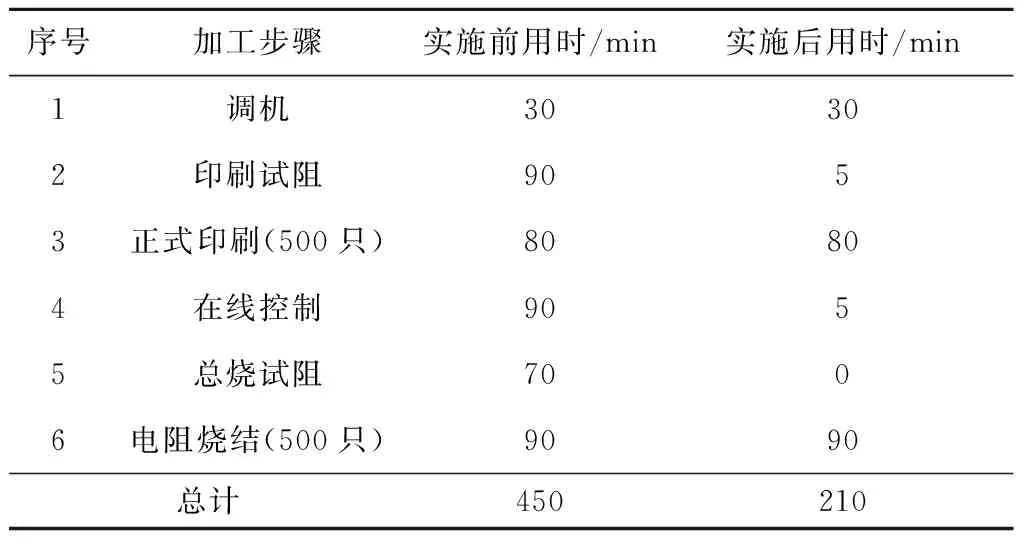

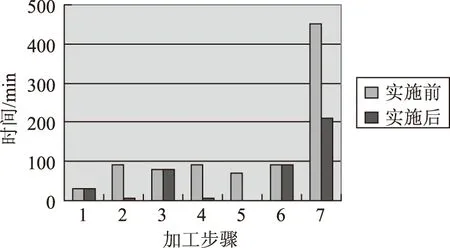

通过采用改进的厚膜电阻加工技术,节约了大量试阻时间,提高了丝网印刷效率。下述列举厚膜电阻丝网印刷用时对照表(表3)和柱状图(图6),通过图6可以看出,印刷效率提高了1倍以上。

表3 实施前、后厚膜电阻丝网印刷用时对照表

图6 实施前、后厚膜电阻丝网印刷用时对比柱状图

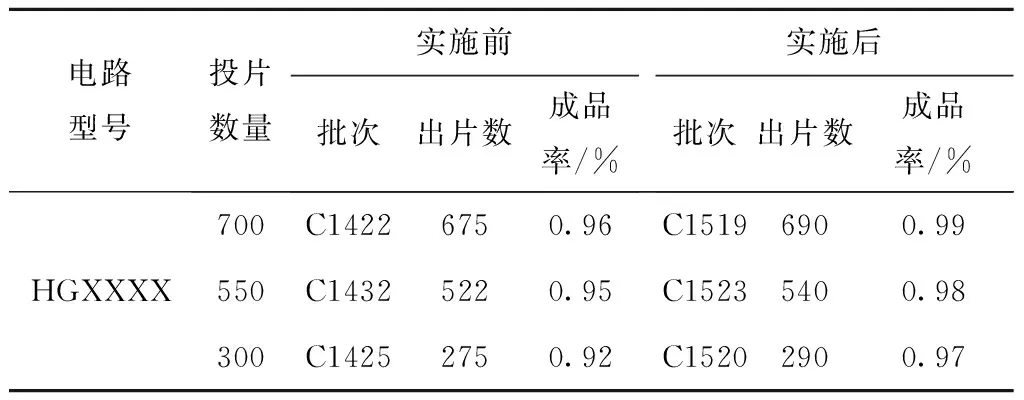

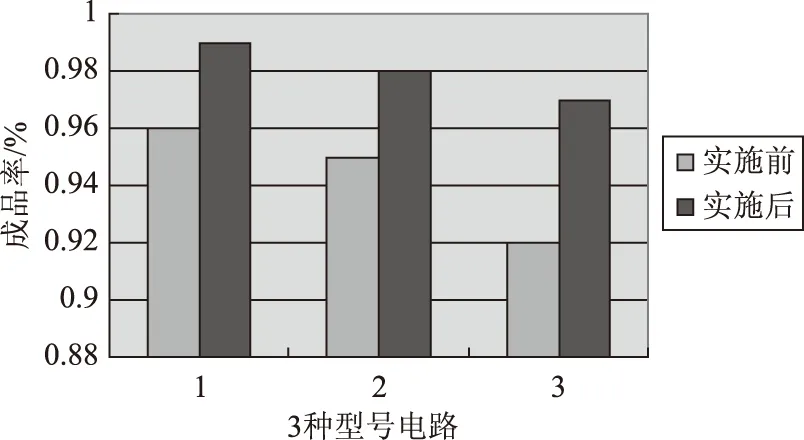

4.2提高成品率

通过采用改进的厚膜电阻加工技术,厚膜集成电路丝网印刷工艺组对各电路的电阻进行优化设计,并统计整理各电阻的膜厚范围,形成参考文件,确定控制办法,形成标准流程作业,节约了网印试阻和激光调阻所产生的废片,使产品质量得到了很大提高,加工成品率提高了3%以上。下述列举了部分电路实施前、后的成品率统计数据,数据表见表4,对比柱状图如图7所示。

表4 部分电路实施前、后的成品率统计数据表

图7 3种型号电路实施前、后的成品率对比柱状图

4.3提高阻值一致性

通过采用改进的厚膜电阻加工技术,对加工完成后的厚膜电阻阻值进行统计,原试阻加工方法因膜厚没有有效控制导致阻值离散性很大,阻值范围为50%~100%,而现在采用改进加工技术后,使厚膜电阻膜厚得到了有效监控,厚膜电阻阻值控制在70%~80%,其一致性好,从而使厚膜电阻质量得到了有效保证。

5 结语

通过采用改进的厚膜电阻加工技术,不仅提高了产品的成品率和加工效率,使生产成本得到了有效控制,同时产品的一致性也得到了提高,使产品质量得到了有效保证。避免了加工过程中不必要的浪费,增强了丝网印刷组员工的节约意识和质量意识,并从技术上提高了工艺加工水平,减少了调机次数和返工片数,从而降低了成膜基板加工成本,显著提高了经济效益。

[1] Licari J J, Enlow L R. 混合微电路技术手册[M]. 朱瑞廉,译.北京:电子工业出版社,2004.

责任编辑郑练

Researoh of the Thick-film Resistor Printing Technology Innovation

YOU Guangwei, ZOU Jian’an, XIAO Lei

(China Ordnance Industry No.214 Research Institute, Bengbu 233042, China)

Aimed at problems like excessively larger distribution of resistance discrete characteristic, low-efficiency in thick-film resistor printing and large amount of material wasting in resistance-testing, the relevant thick-film production technical research has been carried out. Through the analysis of resistance designing and production principles, it has been found that the thick-film resistor printing thickness has a vital impact on its resistance value, then apply the thick-film resistor printing thickness in monitoring the printing process, and the relevant resistance values could be well controlled. Firstly, define the thick-film resistor printing thickness range. Secondly, adjust the resistor printing thickness range by various square resistances. Finally, the actual thick-film resistor printing work is directly referred to the after-adjustment resistor printing thickness range. Through the practical validation experiments, the thick-film resistor printing efficiency and production yields are improved, and the working consistency is elevated.

thick-film hybrid IC, thick-film resistor printing, printing thickness measurement

TN 452

A

尤广为(1969-),男,高级工程师,主要从事厚膜混合集成电路技术等方面的研究。

2015-12-18