低功耗直接衬底耦合QVCO的分析与设计

2016-08-09戚玉华何如龙

戚玉华,何如龙

(海军工程大学 电子工程学院,湖北 武汉 430033)

0 引言

在大多数现代收发系统中,正交信号都扮演着重要的角色.为了得到较好的性能,要求在较低功耗下获得较低相位噪声的正交信号.目前,有多种用于产生正交信号的电路方法,例如文献[1]所采用的频率分频器电路,虽然该方法能产生所需求的正交信号,但是功耗太大;另一种方法是采用多相滤波器电路[2],但是滤波器的损耗较大,为了产生功率足够的信号,需要额外的缓冲电路,导致电路的功耗上升;环形振荡器是产生正交信号最简单的方法[3],但是相位噪声性能较差;第四种电路方法是采用正交压控振荡器QVCO (Quadrature Voltage-Controlled Oscillator)电路[4],该方法能够在较低的功耗下产生较低相位噪声的正交信号.

传统的QVCO电路有两种类型:并联耦合QVCO和串联耦合QVCO.对于并联耦合QVCO,耦合晶体管和开关对的并联引起了共振相位偏移,因而恶化了相位噪声,而在串联耦合QVCO中,晶体管的串联耦合降低了电路的电压裕度并且增加了电路的功耗.而采用衬底耦合技术的QVCO既取得了低相位噪声,又降低了功耗[5].然而,上述这些电路结构的输出都与负载有关并且都需嵌有缓冲电路,因而增加了电路功耗.基于此,文献[6]提出了一种电容抽头技术,然而并没有阐明此技术对相位噪声的影响.本文设计了一种新颖的QVCO电路,该电路由两个与负载无关的传统压控振荡器VCO(Voltage-Controlled Oscillator)组成.并且在电路中采用电容抽头技术取得了与负载无关的振荡频率,降低了相位噪声;而且将交叉耦合晶体管对操作在丙类状态以进一步降低相位噪声和功耗.

1 电路设计

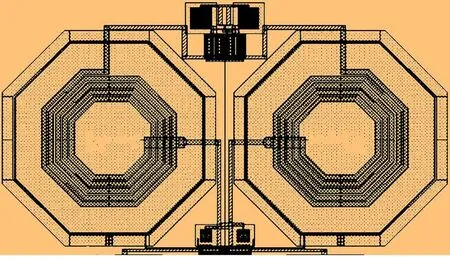

衬底耦合互补QVCO电路如图1所示.晶体管M1、M2和M3、M4组成互补电容交叉耦合晶体管对,该结构能够提供较大的回路电压摆幅.输出Qn耦合到M2、M4的衬底上,Qp耦合到M1、M3的衬底上,输出In和Ip的耦合方式与Qn和Qp类似.NMOS晶体管和PMOS晶体管全部耦合的结构能够取得较高的耦合系数,进而保持较低的相位误差.电感L和可变电容Ct组成谐振回路核心,C1和C2作为抽头电容使用.

图1 本文设计的衬底耦合QVCO电路图

1.1 直接衬底耦合

本文设计的QVCO的耦合采用直接衬底耦合技术,该技术避免了额外的并联或串联晶体管的使用.输出信号的共模电压正向偏置晶体管的衬底,可以获得较低的阈值电压,进而使得晶体管能够操作在低电压下,取得较低的功耗.而且阈值电压的降低,可以为互补结构中堆叠的NMOS和PMOS管对提供较大的电压裕度.并且衬底的正偏状态降低了PMOS管的闪烁噪声,改善了QVCO的相位噪声,鉴于衬底耦合取得了小于单位1的耦合系数,因而可以取得较优的相位噪声.

为了研究直接衬底耦合效应对相位噪声的影响,首先研究该效应对漏极电流开关速度的影响.漏极电流的开关速度表征了电路在零点处对噪声的灵敏度,可以用于评估相位噪声的大小.开关晶体管M3的各级电压可以表示为:

Ug=Acos(ωot)+Uo,

(1)

Ud=Acos(ωot+π)+Uo,

(2)

Ub=Acos(ωot+θ)+Uo.

(3)

其中:A是振荡信号的电压幅度,ωo为振荡角频率,Uo为输出端的直流偏置电压,θ为衬底偏置时的初始相位.

在输出信号电压的零点处,可假定M3工作在饱和区,此刻,若忽略沟道长度调制效应,则M3的漏极电流为:

Id=K(Ugs-Ut)2,

(4)

其中:K为晶体管的导电因子,Ugs为栅源级电压,Ut为晶体管的阈值电压.Ut的表达式为:

(5)

式(5)中:Ut0为衬底偏压为零时的阈值电压,γ为体效应系数,φ为半导体的表面势,Ubs为衬底偏压.

定义漏极电流的开关速度如式(6):

(6)

由于晶体管源极电位恒定,因而有:

(7)

而且,阈值电压关于时间t的偏导数为:

(8)

在正交信号注入衬底的情况下,θ=±π/2,在零点处,ωot=±π/2,因而式(7)和式(8)可重写如式(9):

(9)

将式(9)代入式(6)中,可见正交衬底交流耦合并没有对零点处的漏极电流开关速度造成影响,鉴于此,直接衬底耦合可以作为在低功耗下实现正交耦合的方法.然而,仅仅只有直流耦合作为输出偏置电压的话,降低了Ut,提高了漏极电流开关速度,因而,在本文设计中为了取得较好的相位噪声性能,同时采用直流和交流耦合[7].

1.2 电容抽头技术

本文为了降低功耗和闪烁噪声,将PMOS管偏置在丙类工作状态下,文献[8]的研究成果表明相比较于传统的QVCO而言,晶体管工作丙类状态下可以使得QVCO的相位噪声改善约3.9 dB.为了进一步降低相位噪声,取得与负载无关的振荡频率,该QVCO采用电容抽头技术.图1中抽头电容C1和C2组成的电压分频器在不影响输出信号摆幅的前提下,增加了谐振回路的电压摆幅,进而改善了相位噪声.

附加在谐振回路上的并联寄生电容为:

(10)

QVCO载频在频偏△ω处的相位噪声可被表示为:

(11)

电容抽头技术的引入增加了谐振回路电压摆幅,随着谐振回路电压摆幅的增加,QVCO相位噪声的降低量为:

(12)

其中:下标1代表的是引入电容抽头技术的QVCO,下标2代表的是传统QVCO,可见由于本文中C1∶C2=1∶1.9,使得谐振回路摆幅增加到原先的190%,由式(12)可得出,电容抽头技术使得QVCO的相位噪声至少应降低5.5dB.

2 电路设计与仿真

该QVCO基于TSMC0.13μmCMOS工艺设计,电路版图是另一个影响Ka波段QVCO性能的关键因素,其中的LC振荡回路的版图对其性能影响最大,此部分采用较厚的金属层以更好的减少寄生电容和寄生电阻.采用CadenceSpectraRF对其进行电路的仿真设计.并用CadenceVirtuos进行版图绘画,图2所示即为该QVCO的版图,版图大小为0.75mm×0.45mm.该QVCO在1.1V电压的供电下,所消耗的功耗为2mW.

图2 QVCO版图

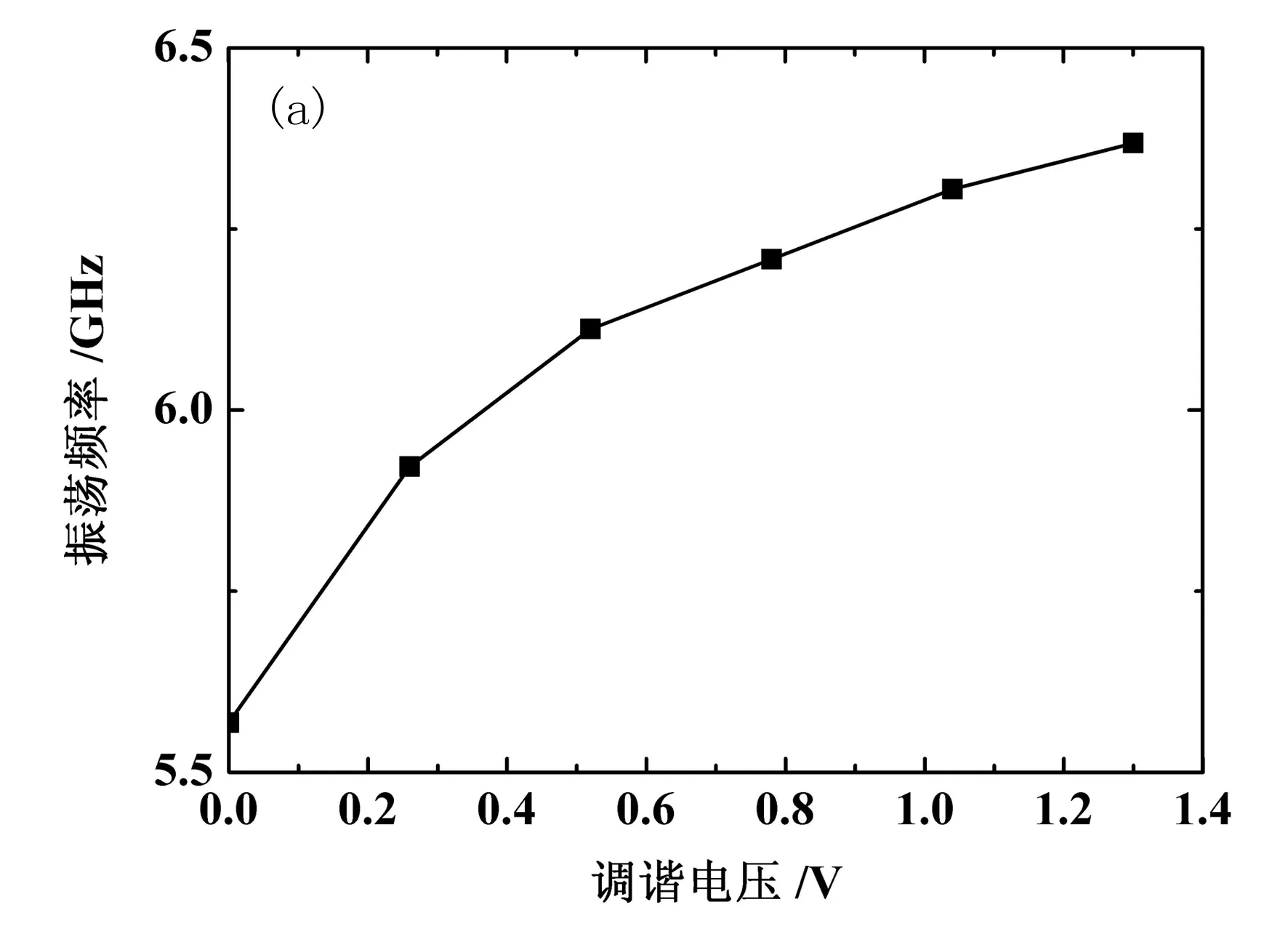

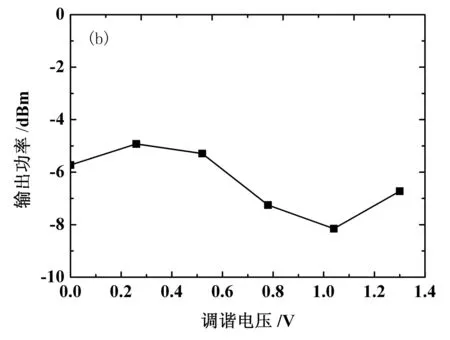

图3给出了利用谐波平衡法所得到的QVCO振荡频率后仿真结果和输出射频功率随着调谐电压的变化曲线. 图4给出了在载频6 GHz处,相位噪声的版图后仿真结果.

图3 QVCO振荡频率和输出射频功率的后仿真结果(a) 振荡频率 (b) 输出射频功率

图4 QVCO相位噪声版图后仿真结果

由图3可见振荡频率为5.57~6.37 GHz,调谐范围为800 MHz,并且QVCO的输出射频功率为-8.15~-4.93 dBm,具有足够的功率用以驱动接收机当中QVCO的下级混频器电路.由图4可见在偏移载波1 MHz处,相位噪声为-119.11 dBc/Hz,相比较于传统的QVCO,相位噪声约改善了6.7 dB.

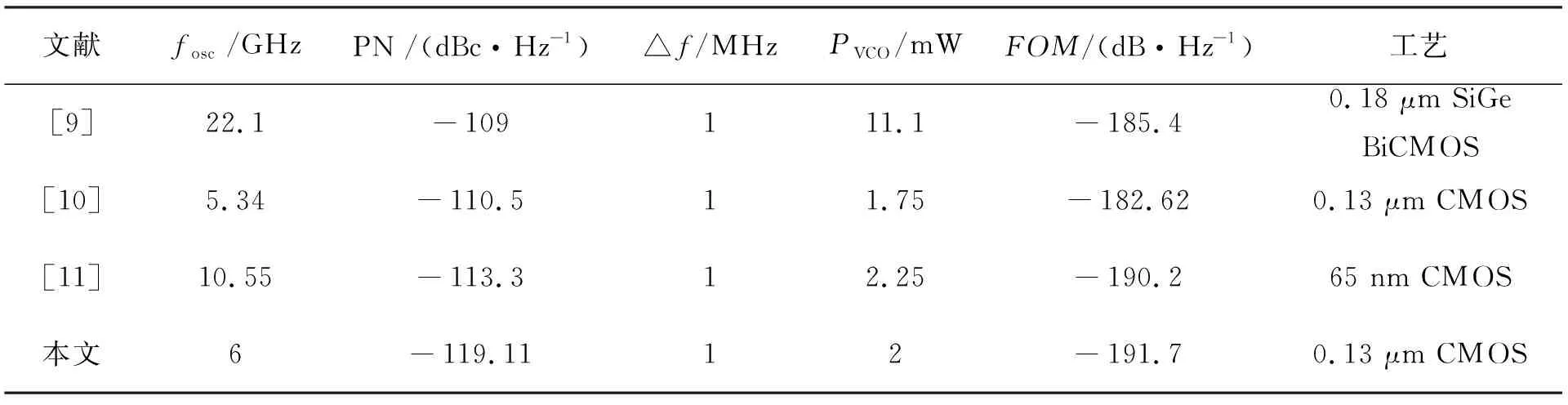

表1总结了本文所设计的QVCO与以往文献的射频QVCO的性能比较结果,其中FoM指标采用式(13)计算而得,其中PN为中心振荡频率fosc在频偏Δf处的相位噪声,Pvco为电路的功耗,由表可见,本文所设计的QVCO的FOM指标达到-191.7 dB/Hz,取得了良好的性能.

FOM=PN-

(13)

表1 射频QVCO的比较结果

3 结论

低功耗低相位噪声QVCO有效地减小了晶体管的闪烁噪声,并且降低了电路对于供电电压的要求,降低了电路功耗.而且,衬底耦合技术的采用不需要附加额外的耦合晶体管,改善了QVCO的相位噪声.交叉耦合PMOS晶体管对工作在丙类状态下,进一步改善了相位噪声,降低了电路功耗.电容抽头技术的采用使QVCO取得了与负载无关的振荡频率.版图后仿真结果表明:该QVCO的振荡频率为5.57~6.37 GHz,实现了-119.11 dBc/Hz@1MHz较低的相位噪声,而电路仅消耗了2 mW的功耗.