FPGA在数字逻辑电路教学中的应用

2016-07-21郝建卫

易 艺,郝建卫

(桂林电子科技大学 信息科技学院 电子工程系, 广西 桂林 541004)

FPGA在数字逻辑电路教学中的应用

易艺,郝建卫

(桂林电子科技大学信息科技学院 电子工程系, 广西桂林541004)

摘要从独立学院培养应用服务型人才的目标出发,以组合逻辑电路和时序逻辑电路的设计为例,提出将FPGA、Quartus II和Verilog HDL等知识融入数字逻辑电路教学。实践表明,该教学方法可以激发学生的学习兴趣,对培养学生的实践动手能力和创新意识起到了积极的促进作用,提高了教学质量。

关键词独立学院;数字逻辑电路;现场可编程门阵列;组合逻辑电路;时序逻辑电路;教学改革

数字逻辑电路是通信工程、电子信息工程、计算机科学与技术、自动化等电子类专业的基础必修课[1-2],是一门理论性和实践性很强的课程[3]。通过对该课程的学习,使学生熟悉数字逻辑电路基本器件的功能和使用方法,掌握数字逻辑电路的分析方法和设计方法,培养学生对数字逻辑电路的应用能力和动手实践能力,为学生学习后续专业课程准备必要的基础理论知识和实验技能。

传统的数字逻辑电路教学模式采用黑板板书和PPT的形式进行,以教师讲授传统的教学内容为主,学生听讲为辅的灌输式教学,学生处于被动学习的状态,学习兴趣匮乏,课堂学习效率和教学效果很不理想[4-6]。针对存在的这些问题,从独立学院培养应用服务型人才的目标出发,根据独立学院学生的学习接受能力,在数字逻辑电路的教学中适当引入FPGA、Quartus II和Verilog HDL等知识,将传统数字电子技术与现代数字电子技术的知识有机融合为一体,在Quartus II开发环境下根据任务的要求,利用Verilog HDL描述出满足设计需要的数字电路,并进行仿真验证,最后下载到FPGA实验箱上进行硬件验证。在设计过程中,学生可以直观、形象地感受到教学内容,进而提高学习的积极性和学习兴趣,实现在有限的课堂时间内将知识和技术高效率地传授给学生,帮助学生理解数字逻辑电路中的理论知识,一定程度地提高学生在数字逻辑电路方面的实际动手能力和创新能力,取得了良好的教学效果[7]。

下面以组合逻辑电路和时序逻辑电路的设计为例,介绍FPGA 在数字逻辑电路课程教学中的应用。

1FPGA在组合逻辑电路设计中的应用

组合逻辑电路是数字逻辑电路的重要组成部分,是学生重点掌握的知识点之一。传统组合逻辑电路的设计方法和步骤[8]如下:

1)分析设计要求,确定输入、输出信号及其因果关系,并列出真值表;

2)根据真值表写出逻辑函数式;

3)选定器件的类型和数目,并将逻辑函数式进行化简或作适当的变换;

4)根据化简后的逻辑函数式画出逻辑电路图。

整个设计过程非常复杂,特别是逻辑函数式的化简,当组合逻辑电路的输入变量较多时,常使学生对逻辑函数式的化简望而生畏。为此,将FPGA、Quartus II和Verilog HDL等知识引入到组合逻辑电路设计中,采用现代的数字电路设计方法来设计组合逻辑电路。现代的设计方法和步骤[8]如下:

1)分析设计要求,确定输入、输出信号及其因果关系;

2)根据输入信号与输出信号的关系用Verilog HDL语言描述组合逻辑电路;

3)用Quartus II开发环境对用Verilog HDL语言描述的组合逻辑电路进行编辑、编译、综合和仿真;

4)将Quartus II开发环境综合后的网表文件下载到FPGA实验箱进行硬件验证。

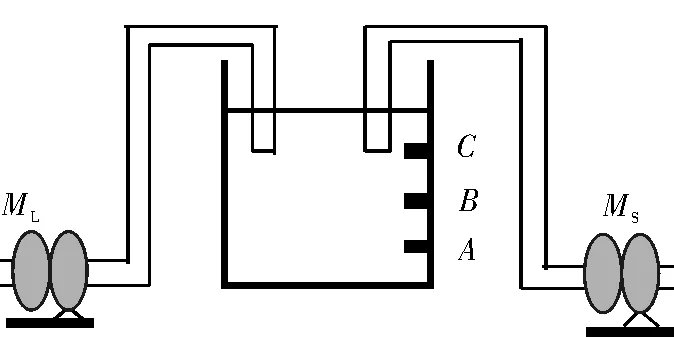

下面以设计一个控制水泵的组合逻辑电路为例详细讲解组合逻辑电路传统和现代的设计方法。如图1所示,由大水泵ML和小水泵MS供水,当水面超过C点,大小两台水泵都不工作;当水位低于C点高于B点时,小水泵MS工作;水位低于B点高于A点时,大水泵ML工作;水位低于A点时,大小两台水泵同时工作[9]。

图1 水箱

1.1采用传统的设计方法进行设计

1)分析设计要求,确定输入信号为检测元件A、B、C,输出信号为水泵ML和MS,依题意得到真值表如表1所示。在真值表中,水面低于检测元件用“1”表示;否则用“0”表示。水泵供水用“1” 表示;否则用“0”表示。

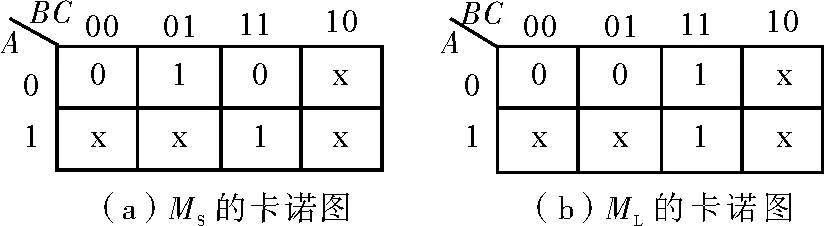

2)根据真值表写出逻辑函数式,选定器件的类型,并进行化简。由真值表分别得到MS的卡诺图,如图2(a)所示;ML的卡诺图,如图2(b)所示。

表1 水泵控制电路真值表

图2 MS和ML卡诺图

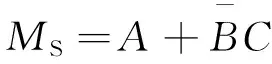

由卡诺图化简后得到的ML和MS逻辑函数式分别为:

(1)

ML=B

(2)

3)由逻辑函数式和选定的器件画出控制水泵的组合逻辑电路图,如图3所示。

图3 控制水泵的组合逻辑电路图

1.2采用现代的设计方法进行设计

1)分析设计要求,确定输入信号为检测元件A、B、C,输出信号为水泵ML和MS。

2)用Verilog HDL语言描述输入与输出信号之间的逻辑电路关系。

module waterctrl(A,B,C,MS,ML);

inputA,B,C;

output regMS,ML;

always @(A,B,C)

begin

if((A==1)&&(B==1)&&(C==1))

beginMS=1;ML=1; end

else if((A==0)&&(B==1)&&(C==1))

beginMS=0;ML=1; end

else if((A==0)&&(B==0)&&(C==1))

beginMS=1;ML=0; end

else

beginMS=0;ML=0; end

end

endmodule

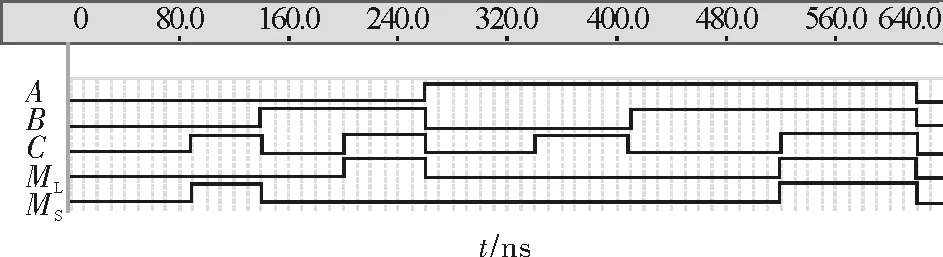

3)用Quartus II开发环境对用Verilog HDL语言描述的组合逻辑电路进行编辑、编译、综合和仿真[10],得到的仿真波形如图4所示。

图4 水泵控制电路仿真图

从图4可看出,当ABC=001时,MS工作,ML停止;当ABC=011时,ML工作,MS停止;当ABC=111时,ML和MS都工作;当ABC为其他情况时,ML和MS都不工作,满足题目的要求。

4)将Quartus II软件综合后的waterctrl.sof文件下载到FPGA实验箱进行硬件的验证。

基于上述两种设计方法分析可知:采用现代的数字电路设计方法,不要求学生必须推导出逻辑函数式,也不需要人工化简逻辑函数式,这些都可以通过使用Quartus II软件,交给计算机处理[11],还可通过仿真来验证设计的电路是否满足题目的要求。使一些看不见、摸不着的抽象理论知识,可以通过仿真和硬件验证,直观、形象地呈现在学生的面前,从而提高学生学习的兴趣。

2FPGA在时序逻辑电路设计中的应用

时序逻辑电路的设计是数字逻辑电路课程中重要的教学内容,也是要求学生重点掌握的知识点之一。同步时序逻辑电路传统的设计方法很复杂,设计方法和具体步骤[8]如下:

1)建立原始状态转换图,并进行状态编码;

2)画出状态卡诺图并化简,求出各级触发器的状态方程和电路的输出方程;

3)检查电路的自启动能力;

4)选定触发器类型并求出驱动方程;

5)根据驱动和输出方程画出电路的逻辑图。

现代的设计方法比传统的设计方法简单易行,更具有优越性。现代的设计方法和具体步骤[8]如下:

1)分析设计要求,进行逻辑抽象,确定输入、输出端口;

2)根据设计要求,用Verilog HDL语言来描述时序逻辑电路的功能;

3)用Quartus II软件对用Verilog HDL语言描述的时序逻辑电路编辑、编译、综合和仿真;

4)将Quartus II软件综合后的网表文件下载到FPGA实验箱进行硬件验证。

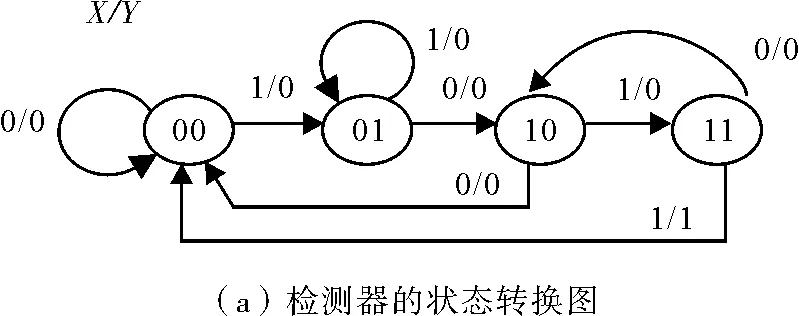

下面以设计一个序列信号检测器为例详细讲解时序逻辑电路传统和现代的设计方法。要求设计一个序列信号检测器,X为序列信号输入端,CP为时钟脉冲输入端,当检测到正确序列信号“1011”时,输出端Y=1,其他情况下Y=0。

2.1采用传统的设计方法进行设计

1)建立原始状态转换图[8],并确定触发器的级数,然后进行状态编码,如图5(a)所示。

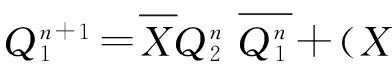

2)画出状态卡诺图,如图5(b)所示,化简后求得各级触发器的状态方程和电路的输出方程为:

(3)

(4)

(5)

3)经过分析得到电路具有自启动的能力,选定触发器类型为JK触发器,根据JK触发器的特性方程求出电路的驱动方程为:

(6)

(7)

J2=X

(8)

(9)

4)根据驱动方程和输出方程画出序列信号检测器的逻辑电路图,如图5(c)所示。

图5 检测器的状态转换图、卡诺图和逻辑电路图

2.2采用现代的设计方法进行设计

1)分析设计要求,确定输入信号为X、CP,输出信号为Y。

2)用Verilog HDL来描述电路的功能。

module xljcq(X,CP,Y);

inputX,CP;

outputY;

reg[2:0]temp;

reg temp1;

always @(negedge CP)

begin

temp=temp<<1;

temp[0]=X;

end

always @(temp)

begin

if(temp==’b101)temp1=’b1;

elsetemp1=’b0;

end

assignY=temp1&X;

endmodule

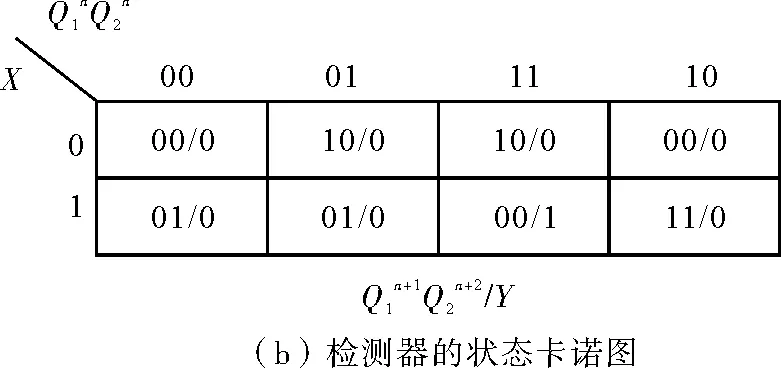

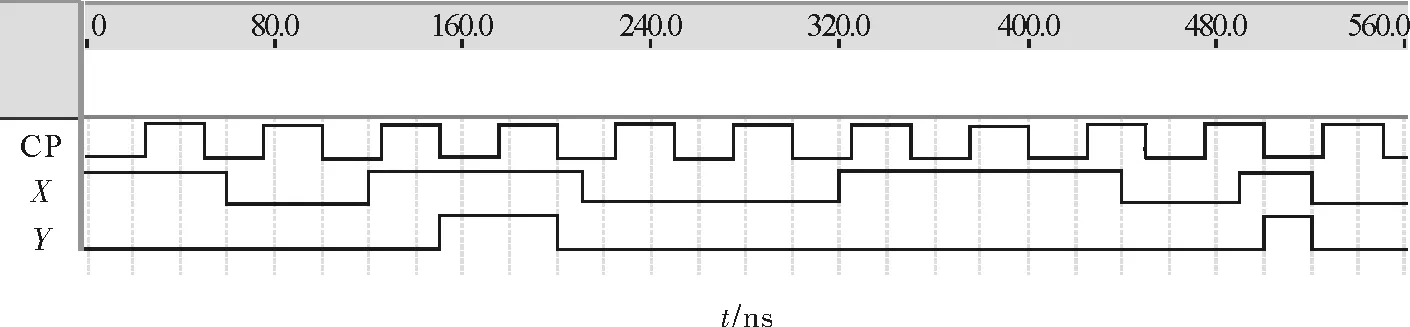

3)用Quartus II软件对用Verilog HDL语言描述的时序逻辑电路进行编辑、编译、综合和仿真[12],得到的仿真波形如图6所示。

图6 序列检测电路仿真图

从图6可看出,当输入端X接收到连续的1011序列信号时,输出端Y=1;否则Y=0。满足题目的要求。

4)将Quartus II软件综合后xljcq.sof下载到FPGA实验箱进行硬件验证。

基于上述两种设计方法分析可知:传统的时序逻辑电路设计方法比较繁琐,设计速度慢,不易掌握;现代的设计方法设计速度快,可以很好地将授课内容进行实验验证,加深了学生对理论知识的理解,可取得很好的教学效果。因此,在数字逻辑电路的教学过程中,我院采用先教师简要讲授传统的设计方法,使学生了解组合逻辑电路和时序逻辑电路传统的设计方法和步骤;然后引入现代的设计方

法,使学生感受到使用现代设计方法的优势,并要求学生重点掌握现代的设计方法和步骤。同时,教师还要注意对学生应用能力和创新意识的培养,鼓励学生对设计题目进行拓展;提倡学生从多方面、多角度去考虑问题;加强与学生的互动,增强学生的自信心[13]。

3结束语

根据当前社会对人才的需求以及独立学院培养应用服务型人才的方针,对数字逻辑电路课程教学进行了教学改革与实践,在讲解传统的知识和技术时,引入一些新颖的、实用的知识和技术,意在激发学生的学习兴趣,培养学生的应用能力以及勇于探索、不断创新的能力。近年来,我院学生在全国各类大学生电子设计竞赛中连获佳绩,得益于运用FPGA来设计数字电路,这与将FPGA技术应用于数字逻辑电路课程的教学是分不开的。为了进一步提高数字逻辑电路课程的教学质量,我院将继续深化数字逻辑电路课程的教学改革,积极探索提高理论教学与实践教学质量的新方法和新途径,为培养出设计能力强、应用能力强和创新意识强的大学生而努力[13]。

参 考 文 献

[1]任爱锋,孙万蓉,石光明.EDA 实验与数字电路相结合的教学模式的实践[J].实验技术与管理,2009,26(4):200-202.

[2]王美玲,陶涛鑫君,江泽民,等.基于PSoC 的数字电子技术教学改革探索[J].实验室研究与探索,2014,33(8):163-165.

[3]叶佳卓,卢斌,程栋.基于EDA 技术的数字电路实践教学探讨[J].实验技术与管理,2010,27(11):249-252.

[4]崔国玮,李文涛.基于EDA技术的数电课程设计新模式的探索与实践[J].实验技术与管理,2008,25(1):123-125.

[5]魏坚华,贾熹滨.基于EDA技术推进数字逻辑课程改革和精品课程建设[J].计算机教育,2011(16):41-43.

[6]任风华,熊凤,许勇.基于Quartus II 9.0 的《数字电路》教学研究[J].现代计算机,2012,10(中):57-59.

[7]方天红,张升义.Proteus在《数字逻辑电路》课程项目驱动教学中的应用[J].实验室研究与探索,2014,33(4):195-197.

[8]江国强.新编数字逻辑电路[M].2版.北京:北京邮电大学出版社,2013.

[9]阎石.数字电子技术基础[M].5版.北京:高等教育出版社,2006.

[10]潘明,潘松.数字电子技术基础[M].北京:科学出版社,2008.

[11]艾明晶.基于自动设计方法的数字逻辑课程改革研究与实践[J].实验技术与管理,2012,29(9):151-155.

[12]王忠林,韩敬伟.EDA技术在时序逻辑电路实验中的应用[J].滨州学院学报,2013,29(6):84-87.

[13]易艺,齐庆堃,郝建卫.独立学院《模拟电子技术》实验教学改革与实践[J].科技资讯,2011(1):169-171.

Application of FPGA in Digital Logic Circuit Teaching

YI Yi,HAO Jianwei

(Department of Electronic Engineering,Institute of Information Technology,Guilin University of Electronic Technology,Guilin 541004,China)

AbstractAccording to the goal of independent college to cultivate application service-oriented talents.The paper presents the field programmable gate array(FPGA),Quartus II and Verilog HDL knowledge to the teaching method in the teaching of digital logic circuit using the combinational logic circuits and sequential logic circuits as a design example.The teaching practice shows that this teaching method can motivate students’ interest in learning.It plays a positive role in promoting students’ practice ability and innovation consciousness,thus enhance the teaching quality.

Key wordsindependent college; digital logic circuit; FPGA; combinational logic circuit; sequential logic circuit;teaching reform

收稿日期:2015-06-30;修改日期: 2015-07-30

作者简介:易艺(1983-),男,讲师,实验师, 主要从事数字逻辑电路和EDA技术的教学和科研工作。 郝建卫(1956-),男,高级实验师,主要从事电子技术、电视技术和电源技术的教学和科研工作。

中图分类号TP 331.2; TP 319

文献标志码A

doi:10.3969/j.issn.1672-4550.2016.02.004